[NAND Flash 3.2] 3D NAND 工艺与发展前沿

依公知及经验整理,原创保护,禁止转载。

专栏 《深入理解NAND Flash》

全文 6200 字,?2023.12.12 更新

1. 导论

1.1 何为 3D NAND?

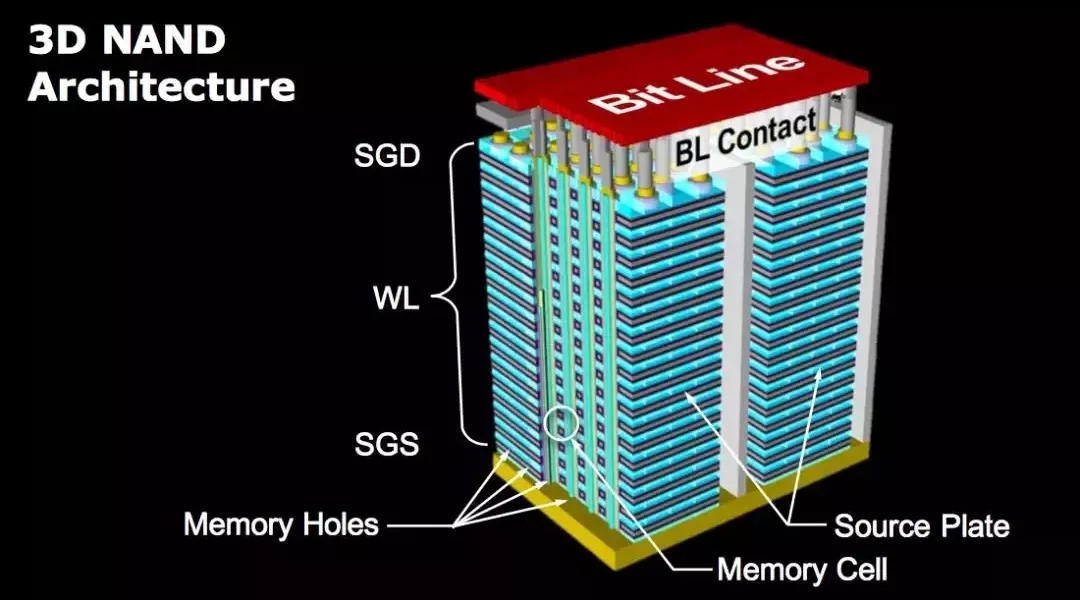

3D NAND, 也叫做 Sumsung V-NAND, 是一种高密度闪存。

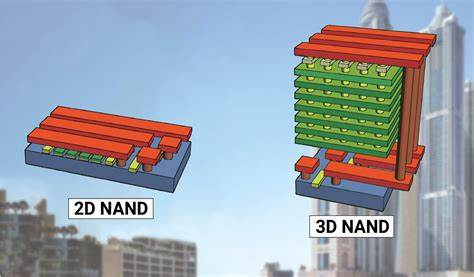

以前,把NAND闪存颗粒,直接平铺在SSD固态硬盘电路板上,叫2D技术。后来,厂家为节约成本,节省空间,像建高楼一样,一层又一层地平铺上去,就成为了3D堆叠闪存技术。

3D NAND闪存是一种新兴的闪存类型,通过把内存颗粒堆叠在一起来,解决2D或者平面NAND闪存带来的限制。相同颗粒数的96层堆叠闪存比32层堆叠闪存的容量大很多,所需要的技术难度也更大。

3D NAND相对2D NAND来说,是一次闪存技术上的变革。而且不同于基于微缩技术的平面闪存,3D存储器的关键技术是薄膜和刻蚀工艺,技术工艺差别较大。

图片来源: https://www.futurepath.com.cn/

1.2 2D to 3D

2D NAND就是平面上的2个维度, 3D就是立方体的3个维度。

多年以前(2018年以前),2D NAND 一直都是半导体工业光刻(lithography)技术的发展推动力,其印刷尺寸是最小的,而且保持逐年下降。随着 2D NAND 的制程缩小到了十几纳米节点(16nm、15nm甚至 14nm),每个单元也变得非常小,使得每个单元中仅有少数几个电子,而串扰问题又使得进一步缩小变得非常困难而且不够经济。

随着 2D NAND 的问题越来越多,已达到瓶颈。前辈们不想一直被二维平面空间局限, 目光投向三维空间,业界开始着眼于 3D NAND。现在,我们正见证着 3D NAND 的快速增长,3D 位产量正在超过 2D 位产量。随着 3D NAND 扩展到 64 层及以上,所有主要制造商的位成本都将低于 2D NAND 的位成本。

1.3 3D 发展史

三星在2013年最先量产了3D NAND,命名为V-NAND。第一代V-NAND作为全球首款量产的3D NAND,只有24层(注意我们所说的XX层,都是指有效WL的层数)。Toshiba在2016年推出了BiCS2(48层)。量产时间整整比三星晚了3年。

2. 3D NAND 工艺

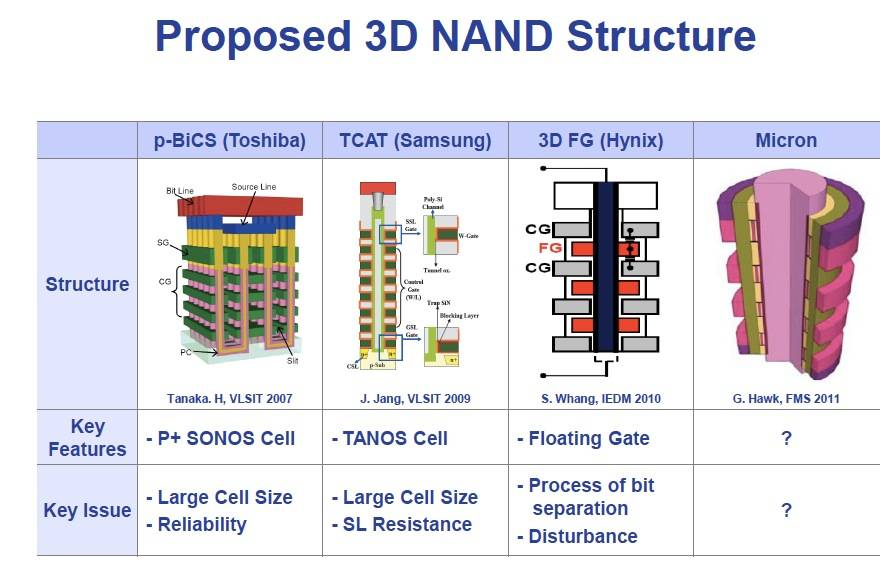

东芝和三星在 3D NAND 上的早期开拓性工作带来了两大主要的互相竞争的 3D NAND 技术。

图片来源: http://www.tuicool.com/

2.1 BICS 工艺

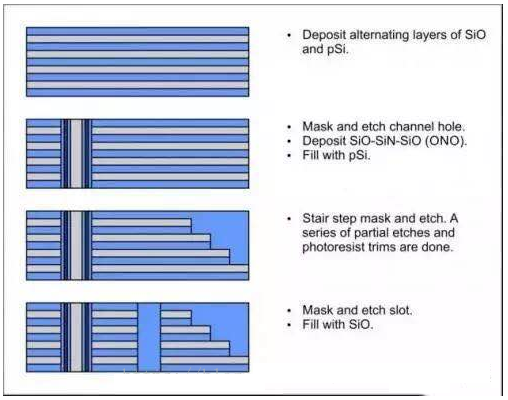

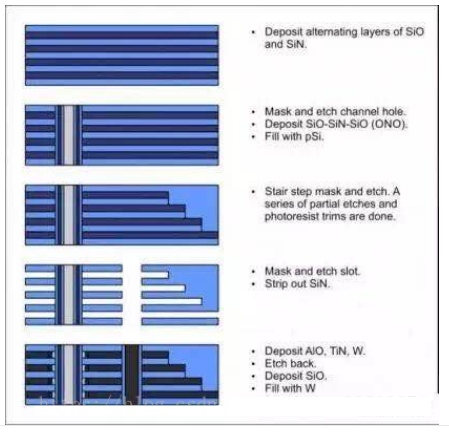

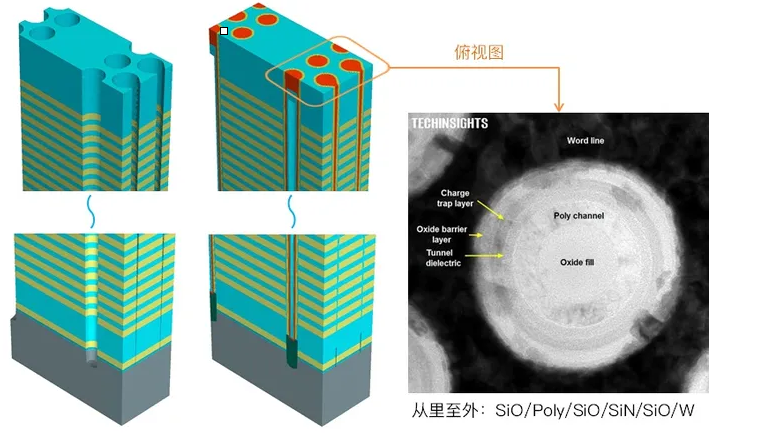

东芝开发了一种叫做 Bit Cost Scalable(BiCS)的工艺。BiCS 工艺采用了一种先栅极方法(gate-first approach),这是通过交替沉积氧化物(SiO)层和多晶硅(pSi)层实现的。然后在这个层堆叠中形成一个通道孔,并填充氧化物-氮化物-氧化物(ONO)和 pSi。然后沉积光刻胶,通过一个连续的蚀刻流程,光刻胶修整并蚀刻出一个阶梯,形成互连。最后再蚀刻出一个槽并填充氧化物。如图 1 所示。

图 1:BiCS 工艺

2.2 TCAT 工艺

三星则开发了一种 Terabit Cell Array Transistor (TCAT)工艺。TCAT 是一种后栅极方法( gate-last approach),其沉积的是交替的氧化物和氮化物层。然后形成一个穿过这些层的通道并填充 ONO 和 pSi。然后与 BiCS 工艺类似形成阶梯。最后,蚀刻一个穿过这些层的槽并去除其中的氮化物,然后沉积氧化铝(AlO)、氮化钛(TiN)和钨(W)又对其进行回蚀(etch back),最后用坞填充这个槽。如图 2 所示。

图 2: TCAT 工艺

这两种工艺都能得到电荷陷阱存储单元(charge trap memory cell)。

从前面的讨论和图中可以看出,这两种工艺的基本不同在于 BiCS 使用了 pSi 字线的先栅极方法,而 TCAT 则使用 W 字线的后栅极方法。

长时间以来,业内都有传言说东芝做不出有效的 BiCS,而东芝的生产部分基本上就是复制的 TCAT 工艺,尽管东芝还是称之为 BiCS。

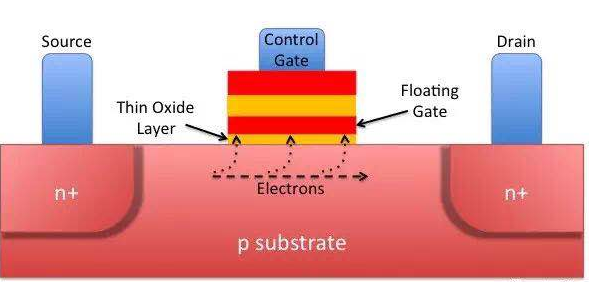

2.3 floating gates 工艺

Hynix走了一条类似于 BiCS 的路,只不过他们构建的是浮栅极(floating gates)。

3. 3D NAND 制作过程

实际上,3D NAND的制作过程相对复杂一些,涉及到多个关键步骤。下面以三星48L V-NAND为例,简单介绍一下3D NAND的制作过程。

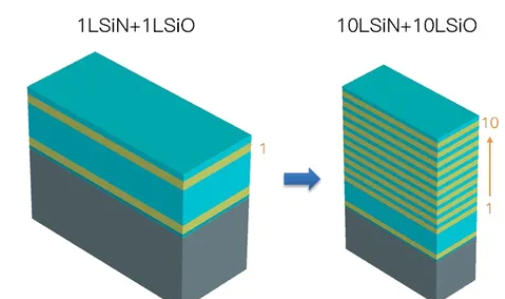

首先,制作3D NAND的第一个关键步骤是刻蚀。在刻蚀之前,需要先进行叠层结构的制作。在V-NAND中,叠层采用的是Channel First工艺,即先制作Control Gate (W)后做叠层。叠层材料一般是由SiN (硅氮化物)和SiO (二氧化硅)组成,按照一定的模式叠放。而在BiCS (Bit Cost Scalable)结构中,叠层则采用的是Gate First工艺,叠层材料是由SiO (二氧化硅)和W (钨)组成。叠层的层数一般较高。

3.1 刻蚀

图片来源 http://www.b-uv.com/

NAND Flash刻蚀的过程包括:

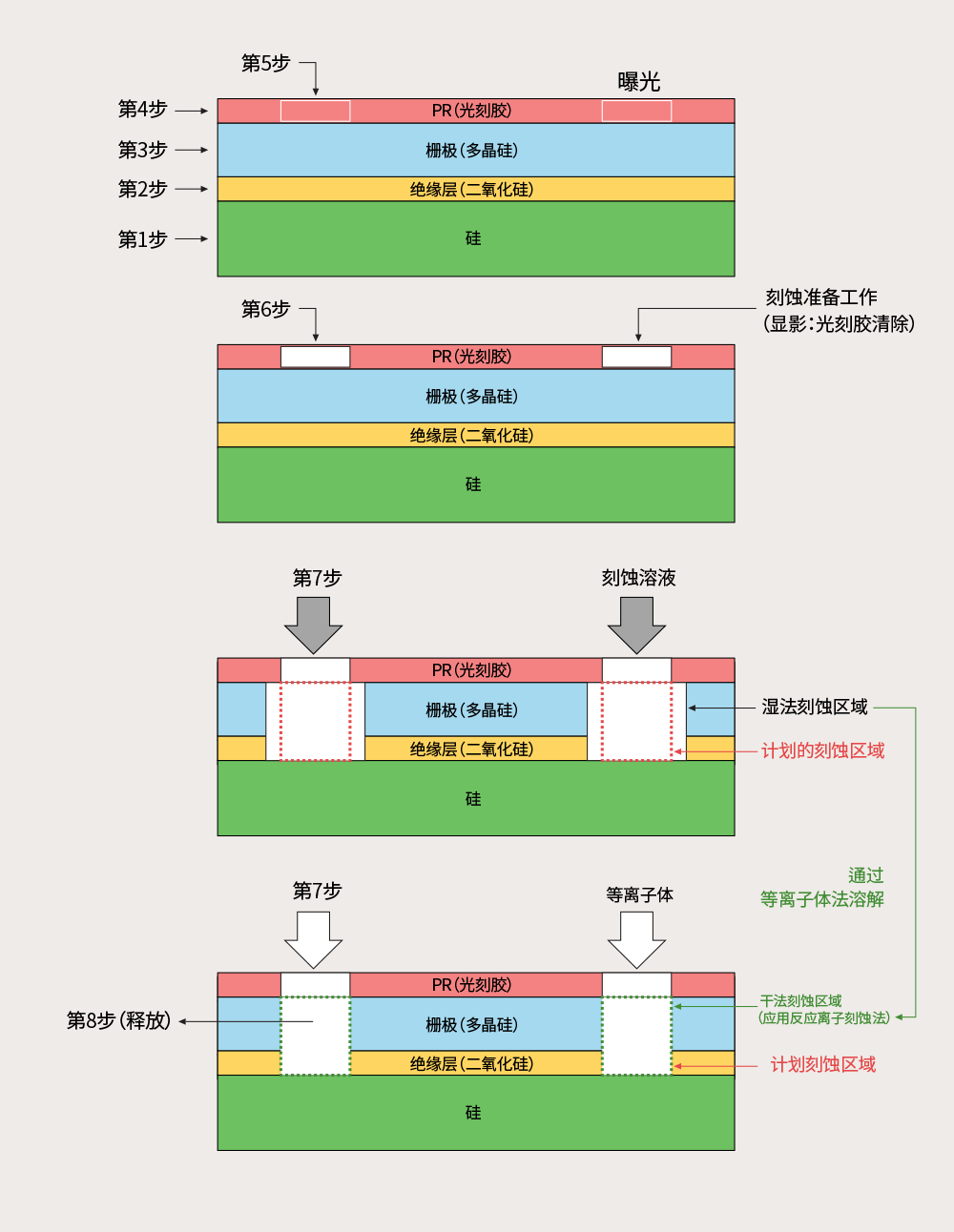

掩膜制备:在硅片上涂覆一层光刻胶,并使用光刻机将芯片的结构图案转移到光刻胶上。然后,使用化学溶液将未曝光区域的光刻胶去除,形成掩膜。

刻蚀:将硅片放置于刻蚀机中,刻蚀机会使用气体或液体化学溶液,根据掩膜上的图案来去除硅片上的材料。刻蚀过程通常包括湿刻蚀和干刻蚀两种方法。湿刻蚀使用液体化学溶液进行刻蚀,而干刻蚀则使用气体进行刻蚀。

清洗和检测:刻蚀后,需要对硅片进行清洗,以去除残留的刻蚀剂和其他杂质。然后,使用显微镜或其他检测设备对硅片进行检测,以确保刻蚀过程的质量和准确性。

可以在硅片上制造出多个NAND闪存器件。

3.2 沉积

通过物理气相沉积或化学气相沉积,将金属层沉积在wafer上,形成电极和连线。

沉积过程包括以下几个主要步骤:

基片准备:基片是制造NAND Flash的基础。首先,基片经过镀金处理,以提高电气连接性。然后,它经过化学机械抛光(CMP)处理,使表面更加平整。

介电层沉积:在基片上沉积一层薄膜,作为NAND Flash的电介质层。这通常是使用化学气相沉积(CVD)或物理气相沉积(PVD)技术完成的。

通道沉积:在介电层上方沉积一层材料,形成NAND Flash的通道。通常使用化学气相沉积技术将硅沉积在介电层上。

电源沉积:在通道上方沉积一层材料,称为电源。电源层用于控制NAND Flash的电荷存储和擦除。

控制层沉积:在电源层上方沉积一层材料,称为控制层。控制层用于控制电荷的流动和操控NAND Flash的操作。

金属沉积:在控制层上方沉积一层金属,用于连接NAND Flash的各个部分。

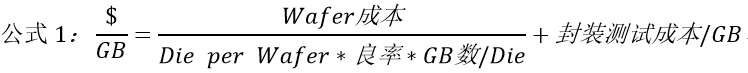

4. 3D NAND的成本计算

NAND每GB容量的成本,等于每片晶圆制造成本除以每片晶圆上能产出对少个Good die对应的GB数,加上每GB封装成本,如下公式1:

随着NAND层数的增加,每片晶圆能生产出的Good Die的数量,并乘以每Die GB数,总的GB数会相应的成比例的增加,同上所述,这是每GB成本下降的核心动力。

封装测试成本取决于封装方式、Pin脚数、以及每颗NAND芯片经过的CP、FT测试转换成的测试成本,通常封测成本相对固定,变化不大。

图片来源: FMS 2022:NAND层数与成本趋势图

5. 3D NAND Scaling的方式

3D NAND Scaling是指通过不同的技术方法来增加3D NAND闪存的单位面积密度(即每平方毫米可以存储的数据量)。与传统的2D NAND相比,3D NAND可以通过增加层数、增加2D平面上的位密度、扩展架构和扩展存储单元的比特位等多种技术手段来实现密度的增加。

- Z Scaling,意思是增加3D NAND层数。Z Scaling是3D NAND当前增加存储密度最重要的方法

增加层数,生产制造上需要对应层数的Etch(蚀刻)新的设备和工艺。

层数越高,一般采用多层堆叠的方式,并解决内存孔(Memory Hole)贴合问题。

400层以上3D NAND的生产制造成本将会受到更多的挑战

- XY Scaling,3D NAND在2D平面空间XY如何微缩以达到增加存储密度的方法,有以下几种:

在XY平面空间上减少Non-cell的面积,也叫Slit reduction,即增加Slit和Slit之间的内存孔的数量,如由九个增加至十四个

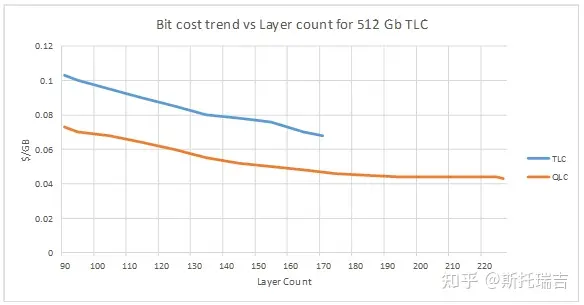

- Architecture Scaling,CMOS和Array如何进行架构设计,有以下几种:

CnA(CMOS and Array)是将CMOS电路和Array左右分开放在2D平面上,但比较占Die的面积(增加成本);

CuA(CMOS Under Array)将CMOS电路置于Array下面大大减小Die面积,因此渐渐的NAND上CuA架构取代了CnA架构。

Xtacking?:同CuA类似,Xtacking?是将CMOS置于Array的上面,CMOS和Array分别设计和生产制造在两块独立的晶圆上,然后键合在一起。

- Logical Scaling,逻辑扩展是用NAND比特位扩展来提升存储密度的方法。从 SLC(一个Cell单元存储1个比特);后来出现了MLC(Multi Level Bit)及TLC(Triple Level Bit),QLC一个Cell单元存储4个比特。

6. 3D NAND 发展前沿

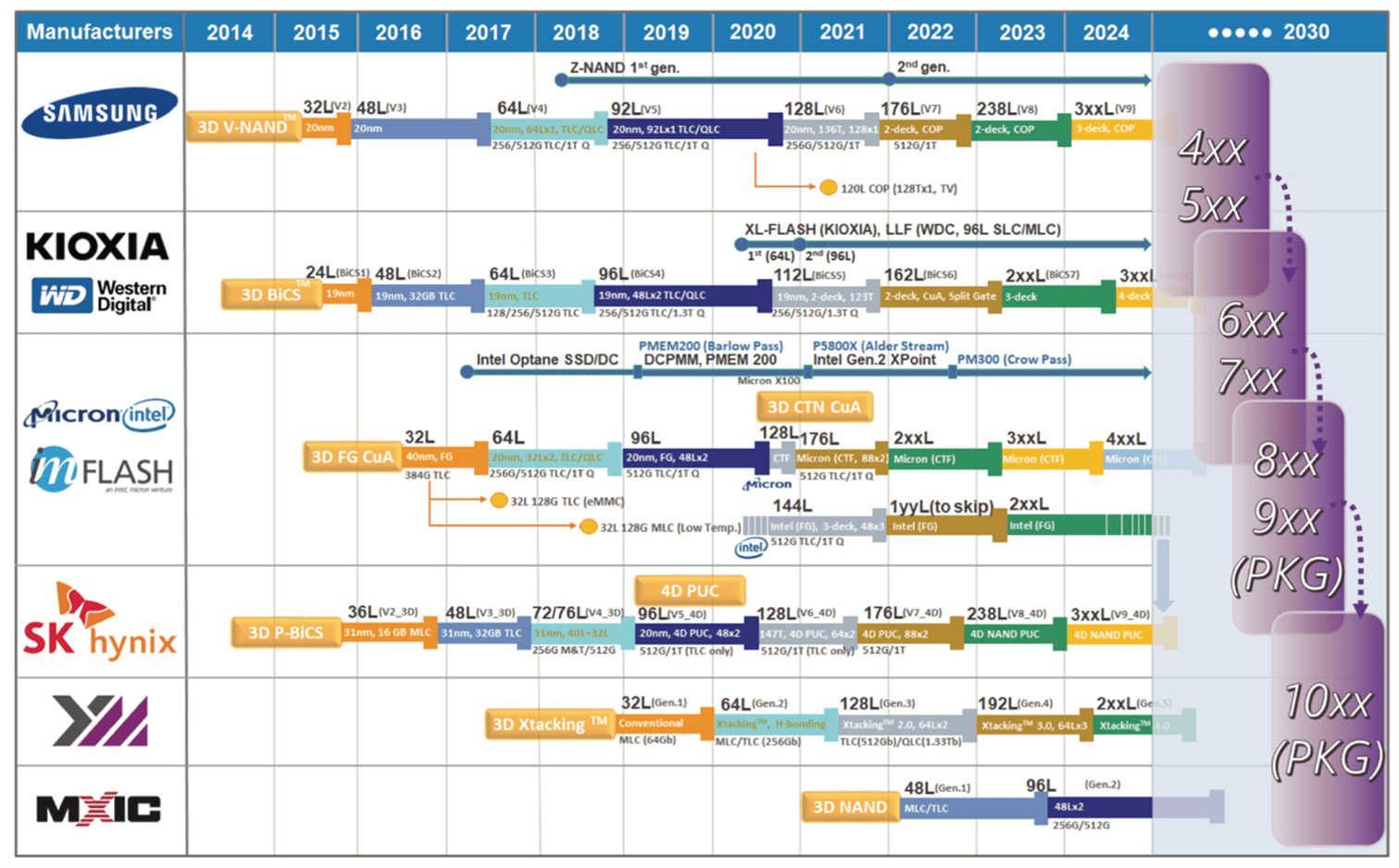

6.1 NAND Roadmap

图片来源: https://www.eettaiwan.com/

最新(2023)进展

- Samsung 236-Layer TLC

- SK hynix 238-Layer TLC

- Solidigm 192-Layer QLC

- KIOXIA/Western Digital 218-Layer TLC/QLC

- Micron – further insights into their 232-layer TLC

- YMTC – further insights into their 128-layer QLC

6.2 创新与展望

三星的V-NAND采用了单VC垂直蚀刻工艺,最多堆叠128层(V6);其他所有的3D NAND产品采用多层的string整合,比如英特尔的144层,3-deck,上中下各48层。这些技术都是基于20nm或19nm的位线半间距,也就是说3D NAND主要是基于ArF-i和双重曝光微影工艺。

随着堆叠的层数增加,垂直NAND的string高度也增加。例如,176层的NAND string高度为12μm。追求高层数的核心目标当然是提高单位面积内的存储密度,并降低存储相同容量数据的成本。QLC芯片目前可以达到15Gb/mm2的密度;每纵列NAND string的栅总数也增加到200个或更多。

6.3 3D NAND技术挑战

制造高度垂直的多层存储单元需要非常精确的制造工艺。由于存储单元非常小,制造过程中的微小偏差或缺陷可能会对性能和可靠性产生不利影响。

3D NAND技术需要使用更多的层数来增加储存密度。然而,随着层数的增加,信号透过多层间的难度也会增加。这可能导致信号交叉和干扰,影响读取和写入速度。

3D NAND技术还要面临储存单元之间的耦合问题。由于存储单元非常接近,其电荷可能会泄漏到周围的单元中,导致数据损坏或交叉干扰。

最后,长期使用3D NAND技术可能会导致单元故障的增加。由于存储单元是在垂直方向叠加的,故障一个单元可能会影响其上面的所有单元。这可能导致大规模的数据丢失。

<<<< 返回总目录 <<<<

参考

| 1 | https://zhuanlan.zhihu.com/p/181189831 |

| 2 | https://www.21ic.com/embed/news/technology/201707/47024.html |

| 3 | https://www.eettaiwan.com/20220628nt61-dram-amd-nand-market-and-technology-development/ |

| 4 | 《Hybrid Cloud and AI through the lens of 3D-NAND technology》 Ranjana Godse. |

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!