【FPGA图像处理实战】- 图像行缓存设计实现方式一(FIFO)

2023-12-13 11:58:06

图像处理中稍复杂点的算法,就需要行缓存,以实现3*3窗口、6*6窗口的数据计算。

本文将介绍使用FIFO来实现图像行缓存的设计,包括关键逻辑分析,源代码实现分享。

一、行缓存功能的设计框架

图像数据一般都是按照从左到右,从上到下,一行行数据的方式发送传输的。

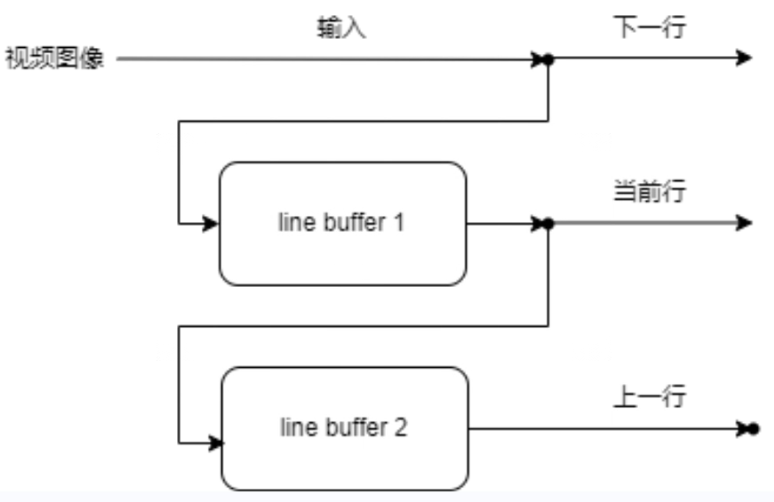

这里以3*3窗口为例,需要同时输出三行(上一行、当前行、下一行),如下图所示。

网上通常看见的行缓存实现,3*3窗口需要3个行缓存,这里我分享更加节省资源的方式,实际只需通过2个行缓存即可实现。

二、行缓存设计的关键思想

每一个行缓存fifo,都是在缓存完一行数据后,如果有新的数据输入,则同步输出一个数据出去。

这样当新的一行数据到来时,第1个行缓存刚好输出上一行数据,第2个行缓存输出当前行数据,刚到来的新的一行数据直接当做下一行数据输出即可。

有些特殊位置数据需要处理:以当前行为图像边界数据时,上一行和下一行数据实际不存在,需要直接给0或者复制当前行来处理。

这里以以3*3窗口为例,边界行处理逻辑如下:

- 第1个行缓存,是整个画面的第1行时, 上一行数据不存在,复制第1个行缓存或者直接为0输出。

- 第1个行缓存,是整个画面的最后第1行时, 下一行数据不存在,复制第1个行缓

文章来源:https://blog.csdn.net/mengzaishenqiu/article/details/134962381

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!