《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(9)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(8)

2.2 HOST主桥

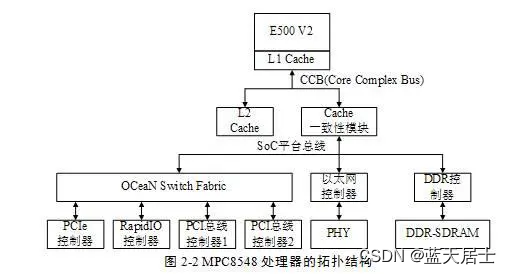

MPC8548处理器的拓扑结构如图2-2所示:

2.2.3?PCI总线域地址空间到存储器域地址空间的转换

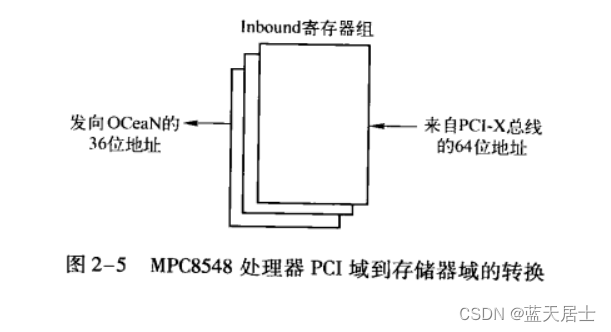

MPC854处理器使用Inbound寄存器组将PCI总线域地址转换为存储器域的地址。PCI设备进行DMA读写时,只有访问的地址在Inbound窗口中时,HOST主桥才能接收这些读写请求,并将其转发到存储器控制器。MPC8548处理器提供了3组Inbound寄存器,即提供3个Inbound寄存器窗口(Outbound是5个),实现PCI总线地址到存储器地址的反向映射。

从PCI设备的角度来看,PCI设备访问存储器域的地址空间时,首先需要通过Inbound窗口将PCI总线地址转换为存储器域的地址;而从处理器的角度来看,处理器必须将存储器地址通过Inbound寄存器组反向映射为PCI总线地址空间,才能被PCI设备访问。

PCI设备只能使用PCI总线地址访问PCI总线域的地址空间。HOST主桥将这段地址空间通过Inbound窗口转换为存储器域的地址之后,PCI设备才能访问存储器域地址空间。这个地址转换过程如图2?5所示:

在介绍MPC8548处理器如何使用Inbound寄存器组进行PCI总线域地址空间到存储器域地址空间的转换之前,我们首先简要介绍Inbound寄存器组中的相应寄存器。该组寄存器的地址偏移、属性和复位值如表2?3所示:

表2-3 PCI/X ATMU Inbound 寄存器组

| 偏移 | 寄存器名 | 属性 | 复位值 |

|---|---|---|---|

| 0x0_8DA0/C0/E0 | PITARn | 可读写 | 0x00000000 |

| 0x0_8DA8/C8/E8 | PIWBARn | 可读写 | 0x00000000 |

| 0x0_8DAC/CC | PIWBEARn | 可读写 | 0x00000000 |

| 0x0_8DB0/D0/F0 | PIWARn | 可读写 | 0x00000000 |

值得注意的是,Inbound寄存器组除了可以进行PCI总线地址空间到存储器域地址空间的转换之外,还可以转换分属不同PCI总线域的地址空间,以支持PCI总线的Peer-to-Peer数据传送方式。

(1)PITARn

PITARn寄存器保存当前Inbound窗口在存储器域中的36位地址空间的基地址,其地址窗口的大小至少为4KB,因此在该寄存器中仅存放存储器域地址的第0~23位,该寄存器的其主要字段如下所示:

- TEA字段存放存储器地址空间的第0~3位。

- TA字段存放存储器地址空间的第4~23位。

(2)PIWBARn和PIWBEARn寄存器

PIWBARn和PIWBEARn寄存器保存当前Inbound窗口在PCI总线域中的64位地址空间的基地址的第63~12位,Inbound窗口使用的最小地址空间为4KB,因此在这两个寄存器中不含有PCI总线地址空间的第11~0位。这两个寄存器的主要字段如下所示:

- PIWBARn寄存器的BEA字段存放PCI总线地址空间的第43~32位。

- PIWBARn寄存器的BA字段存放PCI总线地址空间的第31~12位。

- PIWBEARn寄存器的BEA字段存放PCI总线地址空间的第63~44位。

(3)PIWARn寄存器

PIWARn寄存器描述当前Inbound窗口的属性,该寄存器由以下位和字段组成:

- EN位,第0位。该位是Inbound窗口的使能位,为1表示当前Inbound寄存器组描述的存储器地址空间到PCI总线地址空间的映射关系有效;为0表示无效。

- PF位,第2位。该位为1表示当前Inbound窗口描述的存储区域支持预读;为0表示不支持预读。

- TGI字段,第8~11位。该字段为0b0010表示当前Inbound窗口描述的存储区域属于PCIe总线域地址空间;为0b1100表示当前Inbound窗口描述的存储区域属于RapidIO总线域地址空间。该字段对于OCeaN实现不同域间的报文转发非常重要,如果当前Inbound窗口的TGI字段为0b0010,此时PCI总线上的设备可以使用该Inbound窗口,通过OCeaN直接读取PCIe总线的地址空间,而不需要经过SoC平台总线;如果TGI字段为0b1111表示Inbound窗口描述的存储器区域属于主存储器地址空间,这也是最常用的方式。使用该字段可以实现HOST主桥的Peer-to-Peer数据传送方式。

- RTT字段和WTT字段,分别为该寄存器的第12~15位和第16~19位。Inbound窗口的RTT/WTT字段的含义与Outbound窗口的RTT/WTT字段基本类似。只是在Inbound窗口中可以规定PCI设备访问主存储器时,是否需要进行Cache一致性操作(Cache Lock and Allocate),在进行DMA写操作时,数据是否可以直接进入到Cache中。该字段是PowerPC处理器对PCI总线规范的有效补充,由于该字段的存在,PowerPC处理器的PCI设备可以将数据直接写入Cache,也可以视情况决定DMA操作是否需要进行Cache共享一致性操作。

- IWS字段,第26~31位。该字段描述当前窗口的大小,Inbound窗口的大小在4KB~16GB之间,其值为2^IWS+1。

(4)使用Inbound寄存器组进行DMA操作

PCI设备使用DMA操作访问主存储器空间,或者访问其它PCI总线域地址空间时,需要通过Inbound窗口,其步骤如下:

1) PCI设备在访问主存储器空间时,将首先检查当前PCI总线地址是否在PIWBARn和PIWBEARn寄存器描述的窗口中。如果在这个窗口中,则将这个PCI总线地址通过PITARn寄存器转换为存储器域的地址或者其他PCI总线域的地址;如果不在,将禁止本次访问。

2)如果PCI设备访问的是存储器地址空间,HOST主桥将来自PCI总线的读写请求发送到存储器空间,进行存储器读写操作,并根据Inbound寄存器组的RTT/WTT位决定是否需要进行Cache一致性操作,或者将数据直接写入到Cache中。

结合Outbound寄存器组,可以发现PCI总线地址空间与存储器地址空间是有一定联系的。如果存储器域地址空间被Inbound寄存器组反向映射到PCI空间,这个存储器地址具有两个地址,一个是在存储器域的地址,一个是在PCI总线域的地址;同理PCI总线空间的地址如果使用Outbound寄存器映射到寄存器地址空间,这个PCI总线地址也具有两个地址,一个是在PCI总线域的地址,一个是在存储器域的地址。

由此可以看出,如果MPC8548处理器的某段存储器区域没有在Inbound窗口中定义时,PCI设备将不能使用DMA机制访问这段存储器空间;同理如果PCI设备的空间不在Outbound窗口,HOST处理器也不能访问这段PCI地址空间。

在绝大多数PowerPC处理器系统中,PCI设备地址空间都在HOST主桥的Outbound窗口中建立了映射;而MPC8548处理器可以选择将哪些主存储器空间共享给PCI设备,从而对主存储器空间进行保护。

更多内容请看下回。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!