vivado 主时钟分析

主时钟

主时钟是通过输入端口或千兆位进入设计的板时钟收发器输出引脚(例如恢复的时钟)。主时钟只能由create_clock命令定义。主时钟必须附加到网表对象。此网表对象表示中的点所有时钟边沿源自其并在时钟树上向下游传播的设计。换句话说,主时钟的源点定义Vivado IDE使用的时间零点当计算松弛方程中使用的时钟延迟和不确定性时。

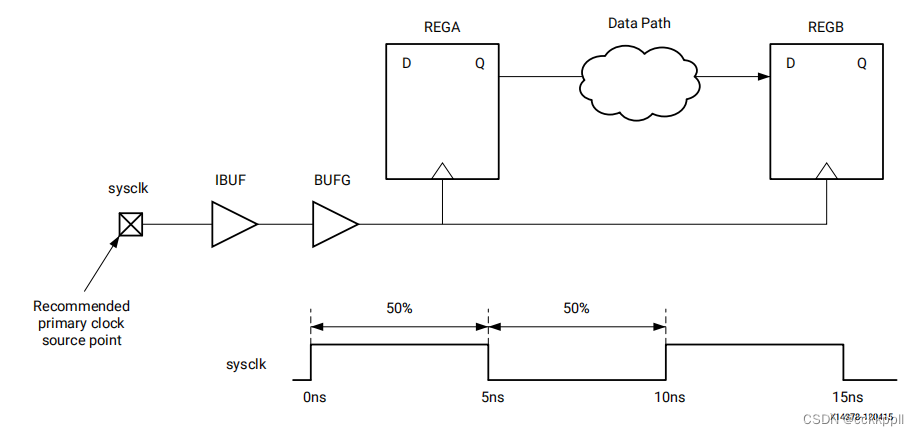

必须首先定义主时钟,因为其他定时约束通常会引用它们。主时钟示例如下图所示,板时钟通过端口sysclk进入设备,然后在到达路径寄存器之前传播通过输入缓冲器和时钟缓冲器。

?其周期为10 ns。

?其工作循环为50%。

?其相位没有偏移。

与sysclk类似,板时钟devclk通过端口ClkIn进入设备。

?其周期为10 ns。

?其工作循环为25%。

?相位偏移90度。

对应的XDC:

create_clock -name devclk -period 10 -waveform {2.5 5} [get_ports ClkIn]

下图显示了一个收发器gt0,它从高速恢复时钟rxclk板上的链接。时钟rxclk具有3.33ns的周期,50%的占空比,并且被路由到MMCM,它为设计生成几个补偿时钟。当在GT0的输出驱动器引脚上定义rxclk时,由MMCM有一个共同的源点,即gt0/RXOUTCLK。路径上的松弛计算它们之间使用适当的时钟延迟和不确定性值。

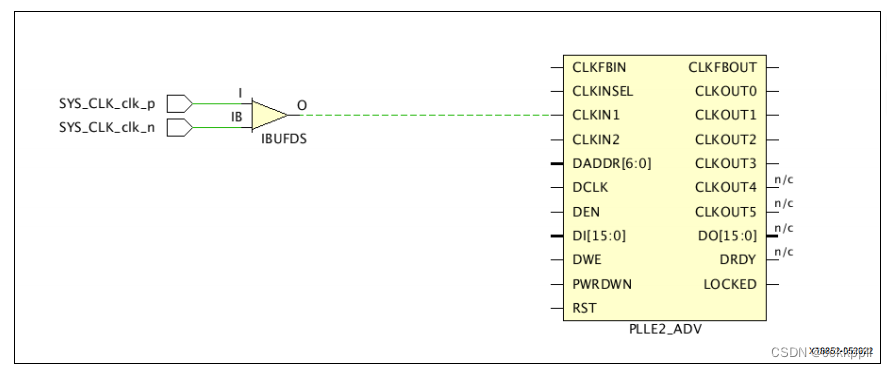

在下图中,差分缓冲器驱动PLL。在这种情况下,主时钟必须仅在差分缓冲器的正输入上创建。在上创建主时钟缓冲器的每个正/负输入将导致不切实际的CDC路径。对于示例:

虚拟时钟

虚拟时钟是指在设计中没有物理连接到任何网表元素的时钟。虚拟时钟是通过create_clock命令定义的,而不指定源对象虚拟时钟通常用于指定其中一个中的输入和输出延迟约束以下情况:

?外部设备I/O参考时钟不是设计时钟之一。

?FPGA I/O路径与无法正确计时的内部生成时钟有关与衍生它的板时钟相反。

注意:当两个周期之间的比率不是整数时,就会发生这种情况。这导致了一个非常紧凑且不切实际的时序路径要求。

?您只想为与I/O延迟相关的时钟指定不同的抖动和延迟而不修改内部时钟特性。

例如,时钟clk_virt具有10ns的周期,并且不附加到任何网表对象。未指定[<objects>]参数。在这种情况下,-name选项是必需的。create_clock-名称clk_virt-周期10在被输入和输出延迟约束使用之前,必须定义虚拟时钟。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!