计算机组成原理(存储器与CPU的连接)

2023-12-19 22:12:01

题目:

设 CPU 共有 16 根地址线。8 根数据线,并用 作访存控制信号,R/

作读/写命令信号。现有这些存储芯片:ROM (2K*8 位、4K*4 位、8K*8 位),RAM(1K*4 位、2K*8 位、4K*8 位)及 74138 译码器和其他门电路(门电路自定)。试从上述规格中选用合适的芯片,画出 CPU和存储芯片的连接图。要求如下

(1) 最小4K 地址作为系统程序区,4096~16383 地址范围为用户地址区

(2) 指出选用的存储芯片类型及数量

(3)?详细画出片选逻辑

解:

本类型题目需要注意的点:

(1)在本题目中需要记住的一个知识点就是系统程序区使用的是ROM的芯片,用户地址区使用的是RAM芯片;

(2)指出存储芯片的类型和数量就是我们所说的字扩展、位扩展、字位扩展;不明白的可以看这篇文章特辑 存储器的一些基础问题;在这个文章中我也说过扩展顺序,先进行位扩展,形成满足位要求的存储芯片组;再使用存储芯片组进行字扩展,也就是先变宽,再变长。

(3)

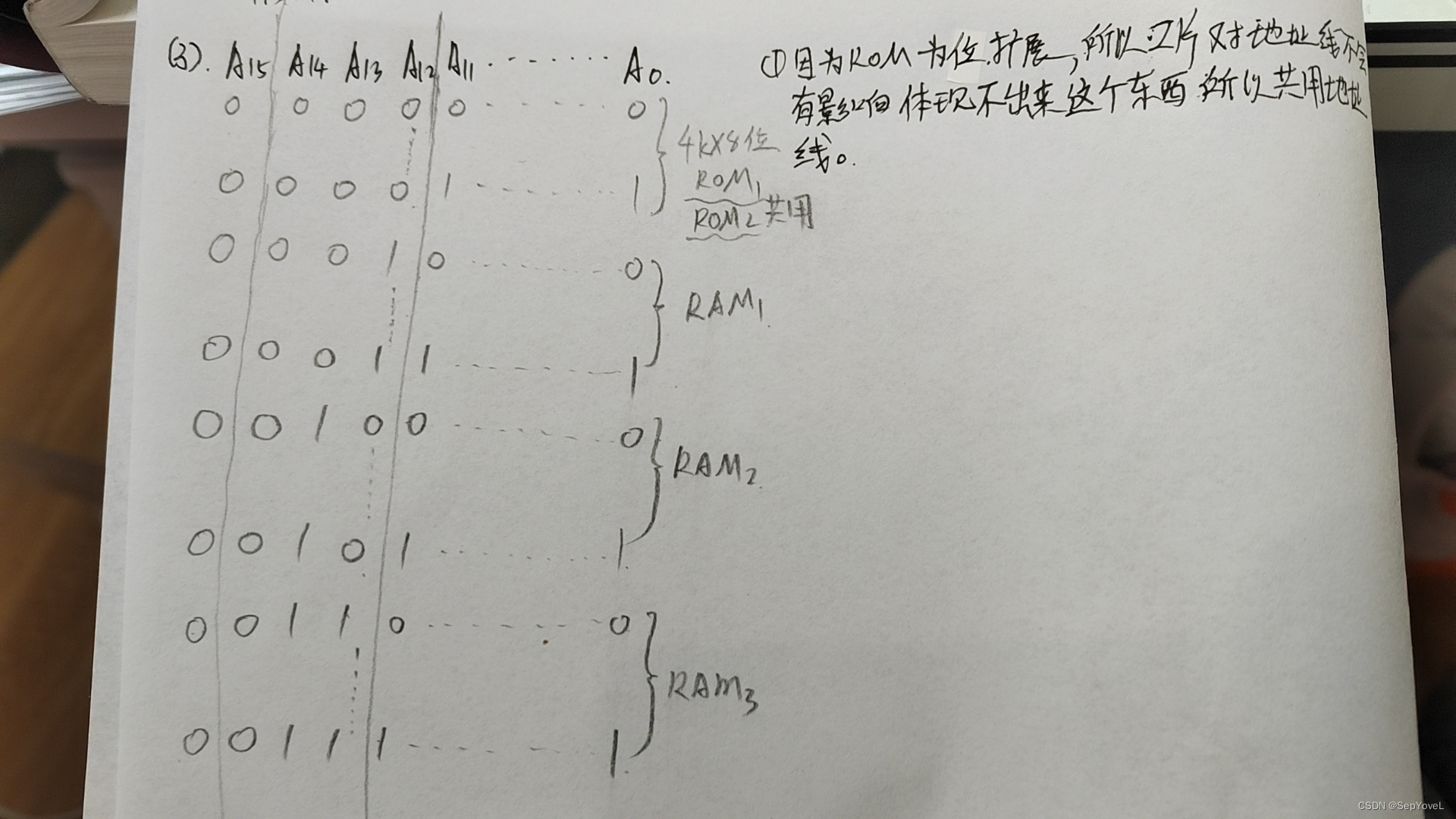

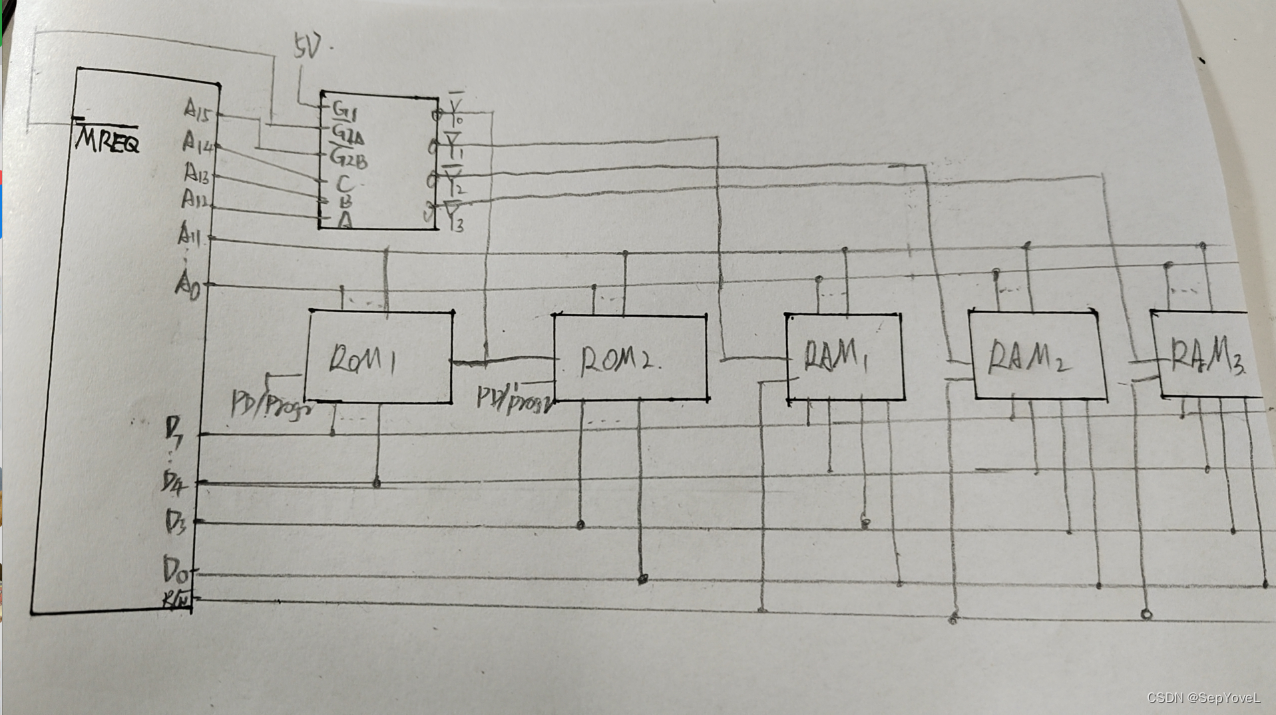

在第一问我们只是把总的一个地址的范围进行了书写,在第三问我们就要将芯片分开来书写地址这样在后面分配地址线的时候好看,方便分配。在这道题目里面需要注意的就是在位扩展时对地址线是不能体现的,会在数据线进行一个体现,所以题目中的ROM1和ROM2公用一种数据线。

在画CPU与存储器连线图的时候,?是必须要连的并且是低电平有效,G1必须为1高电平有效,

和

必须为0低电平有效,这些都可以使用多余的地址线进行连接,做到完全利用。

今天先讲这一个题,后期会慢慢补充,有问题的可以私信我,一起努力学习吧!!!

文章来源:https://blog.csdn.net/weixin_63947322/article/details/135079796

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!