4.8 SUMMARY && 4.9 EXERCISES

总之,在现代处理器中,程序的执行速度可能会受到内存速度的严重限制。为了很好地利用CUDA设备的执行吞吐量,应该在内核代码中获得高计算与全局内存访问率。如果获得的比率很低,则内核受内存约束;即其执行速度受从内存访问其操作数的速度的限制。

CUDA定义了寄存器、共享内存和常量内存。这些存储器比全局存储器小得多,但可以以更高的速率访问。有效使用这些记忆需要重新设计算法。我们使用矩阵乘法来说明平铺,这是一种广泛使用的技术,可以增强数据访问的局部性,并有效地使用共享内存。在并行编程中,tile迫使多个线程在执行的每个阶段共同关注输入数据的子集,以便子集数据可以放入这些特殊的内存类型中,从而提高访问速度。我们证明,通过16×16的tile,全局内存访问不再是矩阵乘法性能的主要限制因素。

然而,CUDA程序员需要意识到这些类型的内存大小有限。他们的能力取决于实施。一旦超过他们的容量,他们就会限制在每个SM中同时执行的线程数量。在开发应用程序时推理硬件限制的能力是计算思维的一个关键方面。

虽然我们在CUDA编程的背景下引入了tile算法,但该技术是在几乎所有类型的并行计算系统中实现高性能的有效策略。原因是应用程序必须在数据访问中表现出局部性,才能在这些系统中有效使用高速存储器。在多核CPU系统中,数据局部性允许应用程序有效地使用片上数据缓存,以减少内存访问延迟并实现高性能。因此,当读者使用其他编程模型为其他类型的并行计算系统开发并行应用程序时,读者会发现tile算法很有用。

线程数并不是“越多越好”。在CUDA编程中,合适的线程数取决于多个因素,包括内核执行的计算密集度、内存访问模式、硬件限制和并行算法的特性。理解这些因素对于优化CUDA程序至关重要。

以下是一些决定线程数的重要考虑因素:

-

硬件限制:每个CUDA设备都有对线程块大小和网格大小的硬件限制。例如,较老的CUDA设备可能限制每个线程块最多包含1024个线程。

-

线程块的尺寸:理想情况下,一个线程块的尺寸应该是warp的倍数。在NVIDIA的CUDA架构中,一个warp包含32个线程。这样可以确保硬件在执行时没有空闲的线程,从而提高效率。

-

资源分配:每个线程块的线程共享该块的寄存器和共享内存。如果一个线程块中的线程数太多,可能会导致这些资源的耗尽,从而迫使内核减少并行执行的块数或者导致更多的全局内存访问,这都会降低性能。

-

内存访问:合适的线程数可以帮助优化内存访问模式,特别是当访问全局内存时。通过设计合理的线程数和内存访问模式,可以减少内存延迟并提高带宽利用率。

-

计算与内存访问的平衡:在计算密集型任务中,较多的线程可以帮助保持GPU的高利用率。然而,在内存密集型任务中,线程数过多可能会导致内存带宽饱和,从而成为性能瓶颈。

-

占用率(Occupancy):占用率是指GPU上活动的warp数与最大可能的warp数的比率。理想的占用率可以帮助隐藏内存延迟,但并不是占用率越高越好。有时候较低的占用率可能因为更高的资源分配而提供更好的性能。

因此,选择合适的线程数通常需要通过对特定应用程序的分析和基准测试来确定。通常,开发者会尝试不同的配置,并通过分析工具来观察性能指标,以此来找到最佳的线程配置。

什么情况下可以隐藏延迟

在CUDA编程中,隐藏延迟(latency hiding)是指当某些线程在等待某些操作(如内存访问或数据依赖)完成时,GPU可以执行其他线程的指令。这种技术可以提高硬件的利用率和整体的性能。以下是几种可以隐藏延迟的情况:

-

多线程并行:GPU具有数千个并行线程。当一些线程等待内存访问时,GPU可以切换到其他线程执行计算。这种快速的上下文切换是隐藏内存访问延迟的关键。

-

足够的占用率:占用率是指GPU上活跃的warp相对于最大可能的warp的比例。如果占用率足够高,GPU就有足够的warp可以在其他warp等待时进行切换,从而隐藏延迟。

-

异步操作:CUDA允许在不同的流中异步执行内核和内存传输操作。如果GPU在执行一个操作(如数据传输)的同时,可以在另一个流中执行计算,这样可以隐藏数据传输的延迟。

-

预取和缓存:通过预取数据到共享内存或L1/L2缓存,可以在数据被实际使用之前就准备好它们,减少等待全局内存访问的时间。

-

计算与内存访问的重叠:如果一个内核的设计允许在执行计算的同时进行内存访问,那么计算可以隐藏内存访问的延迟。

-

使用流水线:在某些算法中,可以将计算分解成若干阶段,并将这些阶段组织成流水线。当某个阶段等待数据时,其他阶段可以继续执行,从而提高整体的吞吐量。

为了最大化延迟隐藏,通常需要仔细设计内核,优化线程数量和占用率,以及合理安排计算和内存访问的顺序。CUDA编程模型和GPU架构的设计就是为了利用这种延迟隐藏来提高并行计算的效率。开发者可以使用CUDA提供的分析工具(如NVIDIA Nsight Compute)来评估和优化他们的代码,以实现更好的延迟隐藏和性能提升。

- 考虑矩阵加法。可以使用共享内存来减少全局内存带宽消耗吗?提示:分析每个线程访问的元素,看看线程之间是否有任何共性。

矩阵加法是一个简单的逐元素操作,每个元素的计算都是独立的。具体来说,矩阵加法的操作可以表示为:

C [ i ] [ j ] = A [ i ] [ j ] + B [ i ] [ j ] C[i][j] = A[i][j] + B[i][j] C[i][j]=A[i][j]+B[i][j]

在这个操作中, C C C 是结果矩阵, A A A 和 B B B 是要相加的两个矩阵, i i i 和 j j j 分别是元素的行索引和列索引。

在CUDA中,通常会为每个元素分配一个线程来执行这个加法操作。由于矩阵加法是逐元素进行的,且每个元素的计算都是独立的,所以每个线程访问的元素是唯一的,没有重复访问同一元素的情况。这意味着在执行矩阵加法时,线程之间没有共享数据的需求。

由于没有数据重用(即每个元素只被读取一次,然后进行计算),使用共享内存并不会减少全局内存带宽的消耗。共享内存主要用于当多个线程需要访问同一数据时,通过将数据缓存到共享内存中来减少全局内存访问的次数和提高访问速度。但在矩阵加法的情况下,每个元素只被一个线程访问一次,因此没有必要将它们复制到共享内存中。

因此,对于矩阵加法这样的逐元素操作,最佳实践通常是直接从全局内存中读取元素,执行加法,然后将结果写回全局内存。这样做的好处是简单且直接,没有额外的内存复制开销,并且可以使得内存访问模式是连续的,这有利于利用GPU的内存带宽。

-

画出相当于图4.14的用于8x8矩阵乘法,2x2 tile和4x4 tile。验证全局内存带宽的减少确实与瓷砖的尺寸成正比。

-

如果在图4.16的内核中省略一个或两个_syncthreads(),可能会发生什么类型的不正确执行行为?

在CUDA编程中,__syncthreads() 是一个同步屏障,用于在同一个线程块内的所有线程之间进行同步。当一个线程执行到 __syncthreads() 时,它会等待,直到同一个线程块内的所有其他线程都达到这个屏障点,然后所有线程才会一起继续执行。这能够确保在继续执行更多的操作之前,所有线程都已经完成了某个特定的工作阶段。

在某些情况下,比如当使用共享内存时,__syncthreads() 尤其重要。共享内存是线程块内所有线程共享的内存区域,它允许快速的数据交换,但也需要仔细的同步来避免竞争条件和数据不一致。

如果省略了 __syncthreads(),可能会发生以下类型的不正确执行行为:

-

竞争条件(Race Condition):如果多个线程同时读写共享内存中的同一位置,而没有适当的同步,那么最终的结果可能取决于线程的执行顺序,这是不确定的。

-

数据不一致(Data Inconsistency):如果一部分线程已经写入了共享内存,而另一部分线程还没有到达写入点,省略

__syncthreads()可能导致某些线程读取到旧的、不一致的数据。 -

死锁(Deadlock):虽然在省略

__syncthreads()的情况下不太可能直接导致死锁,但如果同步屏障用于控制资源访问的顺序,其缺失可能导致逻辑上的死锁,因为线程可能在等待永远不会到来的条件。 -

线程执行顺序问题:某些算法可能依赖于线程执行的特定顺序,

__syncthreads()用于确保所有线程在继续之前都处于相同的执行点。省略它可能导致算法逻辑上的错误。 -

假设容量不是寄存器或共享内存的问题,给出一个重要理由,为什么使用共享内存而不是寄存器来保存从全局内存中获取的值是有价值的?解释你的答案。

共享内存相对于寄存器的一个关键优势在于它是线程间可共享的。这意味着一个线程可以从全局内存中读取数据并将其存储在共享内存中,然后这些数据可以被同一线程块中的其他线程访问,而不需要每个线程都从全局内存中重新读取相同的数据。

这种共享机制在以下情况下特别有价值:

-

数据重用:当多个线程需要读取和处理相同的全局内存数据时,将数据加载到共享内存中可以减少全局内存访问的次数。这对减少内存带宽的消耗和降低延迟非常重要。例如,在矩阵乘法中,每个元素都是由多个线程用于计算不同的输出元素,因此将输入矩阵的块加载到共享内存中可以显著提高效率。

-

协作计算:某些算法需要线程间协作来计算共同的结果,如归约(reduction)或前缀和(prefix sum)计算。在这些情况下,使用共享内存可以让线程块内的线程快速地交换和更新计算中间值。

-

减少全局内存通信:由于全局内存的访问延迟比共享内存高得多,使用共享内存可以减少对全局内存的访问,从而提高性能。寄存器虽然访问速度更快,但它们是线程私有的,不能用于线程间的数据共享。

-

同步控制:共享内存的另一个好处是可以与

__syncthreads()结合使用,以确保线程间的同步。这是寄存器无法做到的,因为寄存器是线程私有的,无法在不同线程间实现同步。

因此,尽管寄存器提供了最快的数据访问速度,但共享内存在需要线程间共享数据时提供了更高的性能和灵活性。在设计CUDA内核时,了解何时使用共享内存而不是寄存器(或相反)对于优化性能至关重要。

- 对于我们的tile矩阵矩阵乘法内核,如果我们使用32x32 tile,输入矩阵M和N的内存带宽使用减少是什么?

A. 1/8 of the original usage

B. 1/16 of the original usage

C. 1/32 of the original usage

D. 1/64 of the original usage

在矩阵乘法中使用tile技术时,我们通常是为了减少对输入矩阵M和N的全局内存访问次数,从而减少内存带宽的使用。通过将输入矩阵分成较小的块(tiles),每个tile被加载到共享内存一次,然后被线程块中的多个线程重复使用来计算输出矩阵的多个元素。

如果我们使用32x32的tile,这意味着每个tile包含 32 × 32 = 1024 32 \times 32 = 1024 32×32=1024个元素。在不使用tile技术的情况下,每个输出元素的计算需要从矩阵M和N中读取32个元素(假设矩阵是方阵且宽度为32的倍数)。因此,对于KxK的输出矩阵,我们需要 K × K × 32 K \times K \times 32 K×K×32次访问M和N中的每个元素。

当使用32x32的tile时,每个tile中的元素只需要从全局内存中读取一次,然后可以用来计算tile区域内32x32的输出矩阵元素。这意味着每个元素的全局内存访问次数从32次降低到1次。

所以,内存带宽的使用减少了32倍,即每个元素的访问从32次减少到1次。这对应于选项C:1/32 of the original usage。

- 假设一个CUDA内核启动时有1000个线程块,每个线程块都有512个线程。如果一个变量在内核中声明为局部变量,那么在内核执行的生命周期内,将创建多少个版本的变量?

在CUDA中,局部变量是每个线程独有的。这意味着每个线程都会有自己的一份局部变量的副本。

给定有1000个线程块,每个线程块有512个线程,那么总的线程数将是:

1000 ?线程块 × 512 ?线程/线程块 = 512 , 000 ?线程 1000 \text{ 线程块} \times 512 \text{ 线程/线程块} = 512,000 \text{ 线程} 1000?线程块×512?线程/线程块=512,000?线程

因此,如果每个线程都声明了一个局部变量,那么在内核执行的生命周期内,将创建512,000个版本的该局部变量。

- 在上一个问题中,如果一个变量被声明为共享内存变量,那么在内核执行的整个生命周期内,将创建多少个版本的变量?

在CUDA中,共享内存是线程块内的线程所共有的。这意味着在同一个线程块内的所有线程共享一份共享内存变量的副本。

如果你有1000个线程块,并且每个线程块声明了一个共享内存变量,那么在内核执行的整个生命周期内,将创建1000个版本的该共享内存变量,因为每个线程块有其自己的共享内存空间。

- 考虑对两个尺寸为N X N的输入矩阵进行矩阵乘法。在以下情况下,从全局内存请求输入矩阵中的每个元素多少次?

A. 如果没有使用tiling(分块),那么在矩阵乘法过程中,每个元素都需要被访问多次。具体地,每次计算输出矩阵的一个元素时,都需要访问输入矩阵的一行和一列。因此,对于输出矩阵中的每个元素,输入矩阵的一个元素将被访问一次。输出矩阵有 N × N N \times N N×N 个元素,所以每个元素将被访问 N N N 次。

B. 使用大小为 T × T T \times T T×T 的tiles时,情况就不同了。每个tile负责计算输出矩阵的一个 T × T T \times T T×T 的子矩阵。为了计算这个子矩阵,每个输入矩阵的tile将被加载到共享内存一次,并用于计算该子矩阵的所有输出值。因为每个tile用于计算 T × T T \times T T×T 个输出值,所以输入矩阵中的每个元素将被加载到共享内存中 N T \frac{N}{T} TN? 次(这里假设 N N N 是 T T T 的倍数,以简化计算)。

总的来说,对于每个矩阵:

- 没有tiling时,每个元素被访问 N N N 次。

- 使用tiling时,每个元素被访问 N T \frac{N}{T} TN? 次。

- 一个kerel每个线程执行36个浮点操作和7个32位单词gobal内存访问。对于以下每个设备属性,请指明此内核是计算bound还是内存bound。

A. Peak FLOPS= 200 GFLOPS, Peak Memory Bandwidth= 100 GB/s

B. Peak FLOPS= 300 GFLOPS, Peak Memory Bandwidth= 250 GB/s

为了确定内核是计算绑定(受限于处理器的计算能力)还是内存绑定(受限于内存带宽),我们需要比较每个内核的计算与内存访问的需求与设备的峰值性能。

首先,我们计算每个内核的计算需求和内存访问需求。

计算需求:

- 每个内核执行 36 个浮点操作。

内存访问需求:

- 每个内核执行 7 个 32 位单词的全局内存访问,每个单词 4 字节,总共 7 × 4 = 28 7 \times 4 = 28 7×4=28 字节。

现在,我们计算每个内核的计算吞吐量和内存带宽需求。

设备A:

- 峰值 FLOPS = 200 GFLOPS

- 峰值内存带宽 = 100 GB/s

设备B:

- 峰值 FLOPS = 300 GFLOPS

- 峰值内存带宽 = 250 GB/s

接下来,我们计算每个内核的计算吞吐量和内存带宽需求:

计算吞吐量需求 (FLOPS):

- 每个内核需要 36 FLOPS。

内存带宽需求 (GB/s):

- 每个内核需要 28 28 28 字节。为了将字节转换为吉字节,我们除以 2 30 2^{30} 230。

现在,我们需要计算内核在峰值性能下可以执行多少次操作。这可以通过将设备的峰值 FLOPS 和峰值内存带宽除以每个内核的计算和内存需求来计算。

设备A的计算限制(内核数/秒):

200

×

1

0

9

?FLOPS

36

?FLOPS/内核

=

200

×

1

0

9

36

?内核/秒

\frac{200 \times 10^9 \text{ FLOPS}}{36 \text{ FLOPS/内核}} = \frac{200 \times 10^9}{36} \text{ 内核/秒}

36?FLOPS/内核200×109?FLOPS?=36200×109??内核/秒

设备A的内存限制(内核数/秒):

100

×

1

0

9

?字节/秒

28

?字节/内核

=

100

×

1

0

9

28

?内核/秒

\frac{100 \times 10^9 \text{ 字节/秒}}{28 \text{ 字节/内核}} = \frac{100 \times 10^9}{28} \text{ 内核/秒}

28?字节/内核100×109?字节/秒?=28100×109??内核/秒

设备B的计算限制(内核数/秒):

300

×

1

0

9

?FLOPS

36

?FLOPS/内核

=

300

×

1

0

9

36

?内核/秒

\frac{300 \times 10^9 \text{ FLOPS}}{36 \text{ FLOPS/内核}} = \frac{300 \times 10^9}{36} \text{ 内核/秒}

36?FLOPS/内核300×109?FLOPS?=36300×109??内核/秒

设备B的内存限制(内核数/秒):

250

×

1

0

9

?字节/秒

28

?字节/内核

=

250

×

1

0

9

28

?内核/秒

\frac{250 \times 10^9 \text{ 字节/秒}}{28 \text{ 字节/内核}} = \frac{250 \times 10^9}{28} \text{ 内核/秒}

28?字节/内核250×109?字节/秒?=28250×109??内核/秒

我们比较两个限制(计算和内存)来确定瓶颈。如果计算限制(内核数/秒)更低,那么内核是计算绑定的;如果内存限制(内核数/秒)更低,那么内核是内存绑定的。

计算上述数值,我们可以得出结论:

设备A的计算限制(内核数/秒): 约 5.56 亿内核/秒

设备A的内存限制(内核数/秒): 约 3.57 亿内核/秒

设备B的计算限制(内核数/秒): 约 8.33 亿内核/秒

设备B的内存限制(内核数/秒): 约 8.93 亿内核/秒

对于设备A,内存限制低于计算限制,所以内核是内存绑定的。

对于设备B,计算限制和内存限制相当接近,但计算限制略低,所以内核可能是轻微的计算绑定或者同时受到计算和内存的限制。实际情况可能取决于其他因素,如内存访问模式和缓存效率。

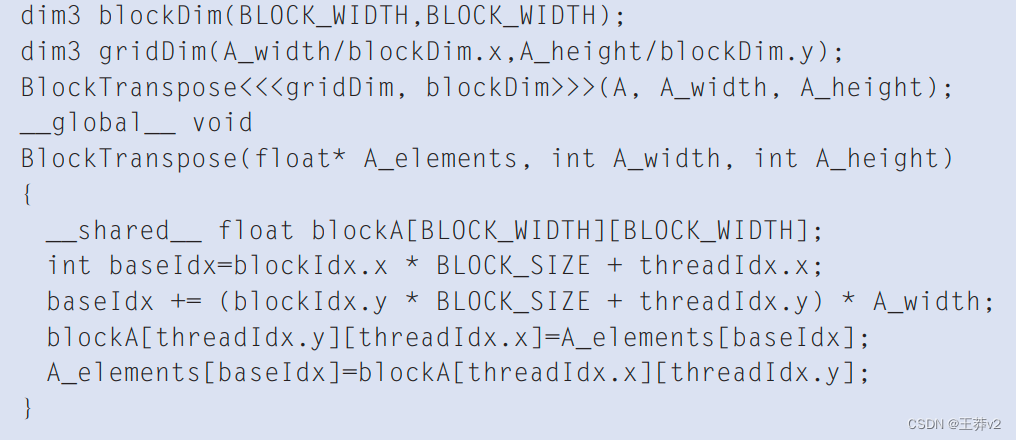

- 为了操作tile,一个新的CUDA程序员编写了以下device内核,该内核将在矩阵中转换每个tile。tile的大小为BLOCK_WIDTH,矩阵A的每个维度都已知是BLOCK_WIDTH的倍数。内核调用和代码如下所示。BLOCK_WIDTH在编译时是已知的,但可以在1到20之间设置。

A. Out of the possible range of values for BLOCK_SIZE, for what values of

BLOCK_SIZE will this kernel function execute correctly on the device?

B. If the code does not execute correctly for all BLOCK_SIZE values,

suggest a fix to the code to make it work for all BLOCK_SIZE values.

A. 在给定的代码中,BLOCK_SIZE 应该是 BLOCK_WIDTH 的一个错误,因为 BLOCK_WIDTH 已经在代码注释中提及,并且在内核调用中作为 blockDim 的参数。所以,我们将在后面的分析中假设 BLOCK_SIZE 实际上是 BLOCK_WIDTH。

这段代码试图在共享内存中转置一个 tile,然后将其写回全局内存。然而,这段代码有几个问题:

- 内存写入冲突:所有的线程都试图同时写入同一块全局内存。这会导致写入冲突,并且结果不可预测。

- 同步问题:在从共享内存写回到全局内存之前,没有同步线程。这意味着一些线程可能会在其他线程完成从全局内存读取之前就开始写入,这会导致错误的结果。

对于 BLOCK_WIDTH 的值,理论上,只要 BLOCK_WIDTH 的值不超过 GPU 的最大线程数限制,并且共享内存的大小足够,这个内核就能在设备上正确执行。然而,由于上述问题,此代码在任何 BLOCK_WIDTH 值下都不能保证正确执行。

B. 为了修复代码,我们需要确保所有线程都完成了共享内存的写操作,并且在从共享内存读取并写回全局内存之前进行同步。此外,我们需要确保内核在写回数据时不会覆盖还未读取的数据。下面是修复后的代码示例:

__global__ void BlockTranspose(float* A_elements, int A_width, int A_height)

{

__shared__ float blockA[BLOCK_WIDTH][BLOCK_WIDTH];

// 计算原始全局内存索引

int xIndex = blockIdx.x * BLOCK_WIDTH + threadIdx.x;

int yIndex = blockIdx.y * BLOCK_WIDTH + threadIdx.y;

int index_in = xIndex + (yIndex * A_width);

// 转置坐标

int xIndex_transposed = blockIdx.y * BLOCK_WIDTH + threadIdx.x;

int yIndex_transposed = blockIdx.x * BLOCK_WIDTH + threadIdx.y;

int index_out = xIndex_transposed + (yIndex_transposed * A_height);

// 从全局内存加载到共享内存

blockA[threadIdx.y][threadIdx.x] = A_elements[index_in];

// 同步确保所有数据都加载到共享内存

__syncthreads();

// 从共享内存写回到全局内存的转置位置

A_elements[index_out] = blockA[threadIdx.x][threadIdx.y];

}

在这个修正的版本中,我们添加了 __syncthreads() 来同步线程,确保所有读取操作完成后再进行写操作。我们还计算了转置后的索引 index_out,这样每个线程都会将其共享内存中的元素写入全局内存的正确位置。这个修正的代码应该能够正确地在任何 BLOCK_WIDTH 值下执行,前提是 BLOCK_WIDTH 不超过 GPU 的最大线程数限制,并且共享内存大小足够。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!