【FPGA】Verilog:BCD 加法器的实现 | BCD 运算 | Single-level 16 bit 超前进位加法器 | 2-level 16-bit 超前进位加法器

2023-12-13 04:45:29

0x00 BCD 运算

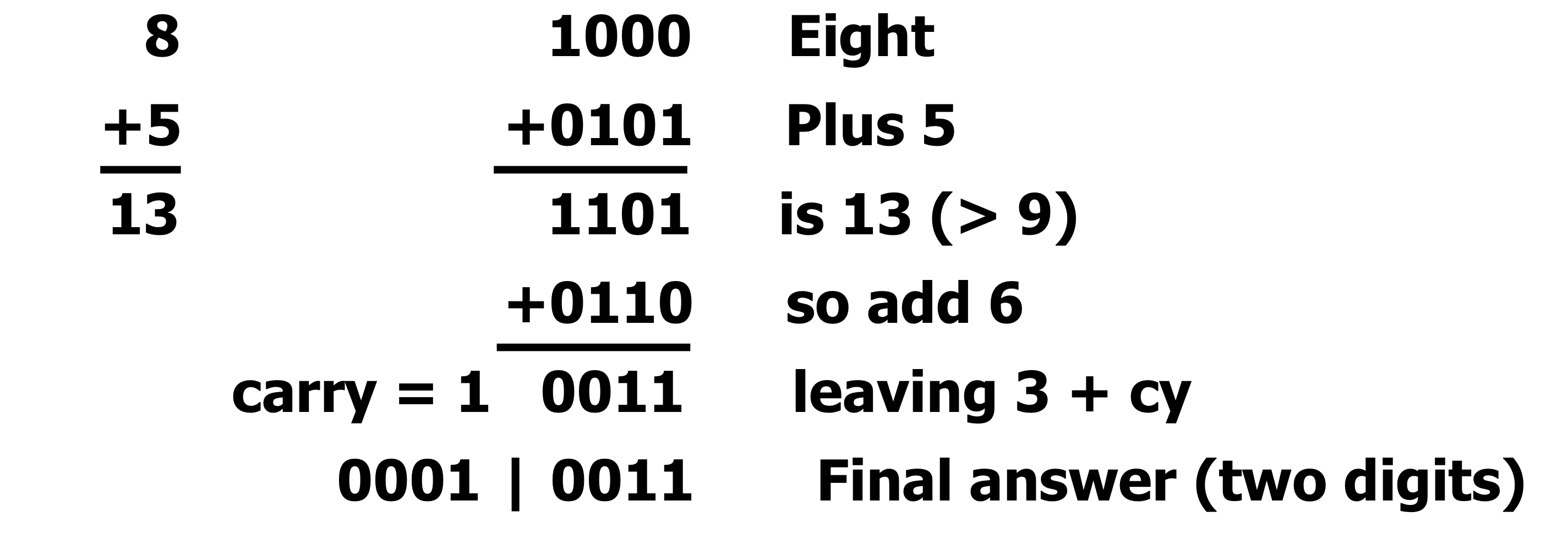

在 BCD 中,使用4位值作为操作数,但由于只表示 0 到 9 的数字,因此只使用 0000 到 1001 的二进制数,而不使用 1010 到 1111 的二进制数(don't care)。

因此,不能使用常规的 2'complement 运算来计算,需要额外的处理:如果 4 位二进制数的运算结果在 1010 到 1111 的范围内,需要将 6 (即 0110),添加到运算结果中。

| BCD 运算例子 |

|

|

0x01 BCD 加法器的实现

文章来源:https://blog.csdn.net/weixin_50502862/article/details/134880375

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!