Lowest cost with low-power CPLD

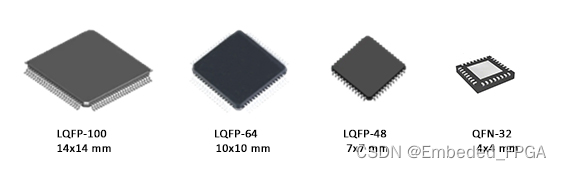

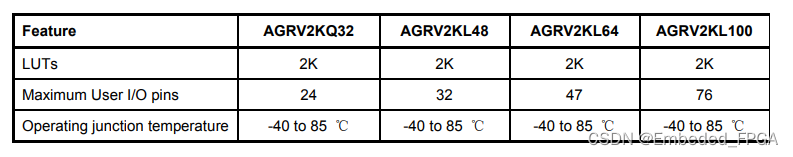

AGRV2K CPLDs is the lowest cost CPLDs. This instant-on, non-volatile CPLD family targets general-purpose and low-density logic. The logic density is 2K Logic Elements with LQFP-100(AGRV2KL100) , LQFP-64(AGRV2KL64) , LQFP-48(AGRV2KL48) and QFN-32 (AGRV2KQ32) packages.

Lowest Cost and low-power CPLD

Instant-on, non-volatile standard compatible architecture.

Up to 4 global clock lines in the global clock network that drive throughout the entire device.

Provides programmable fast propagation delay and clock-to-output times.

Provides PLL per device, clock multiplication, and phase shifting.

Contains 4 Embedded Block RAMs (EBRs) M9K, that can be configured to provide various memory functions, such as RAM, shift registers, ROM, and FIFO.

Supports 3.3-V logic level

Programmable slew rate, drive strength, bus-hold, programmable pull-up resistors, open-drain output, Schmitt triggers and programmable input delay.

Built-in Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry complaint with IEEE Std. 1149.1-1990

ISP circuitry compliant with IEEE Std. 1532

On-Chip oscillator is provided to support frequency to 8 MHz

3.3-V LVCMOS and LVTTL standards

AGRV2K CPLD 是成本最低的 CPLD。该即时启动、非易失性 CPLD 系列面向通用和低密度逻辑。逻辑密度为 2K 逻辑元件,采用 LQFP-100(AGRV2KL100)、LQFP-64(AGRV2KL64) 、 LQFP-48(AGRV2KL48) 和 QFN-32 (AGRV2KQ32) 封装。

堪称业内最低成本和低功耗 CPLD;

即时启动、非易失性标准兼容架构。

全局时钟网络中多达 4 条全局时钟线驱动整个器件。

提供可编程的快速传播延迟和时钟到输出时间。

为每个设备提供 PLL、时钟倍频和相移。

包含 4 个嵌入式 Block RAM (EBR) M9K,可配置为提供各种存储功能,例如 RAM、移位寄存器、ROM 和 FIFO。

支持 3.3V 逻辑电平;

可编程转换速率、驱动强度、总线保持、可编程上拉电阻、开漏输出、施密特触发器和可编程输入延迟。

内置联合测试行动组 (JTAG) 边界扫描测试 (BST) 电路符合 IEEE 标准。1149.1-1990。

ISP 电路符合 IEEE 标准。第1532章

提供片上振荡器以支持高达 8 MHz 的频率;

3.3V LVCMOS 和 LVTTL 标准。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!