HXDSP2441-Demo板

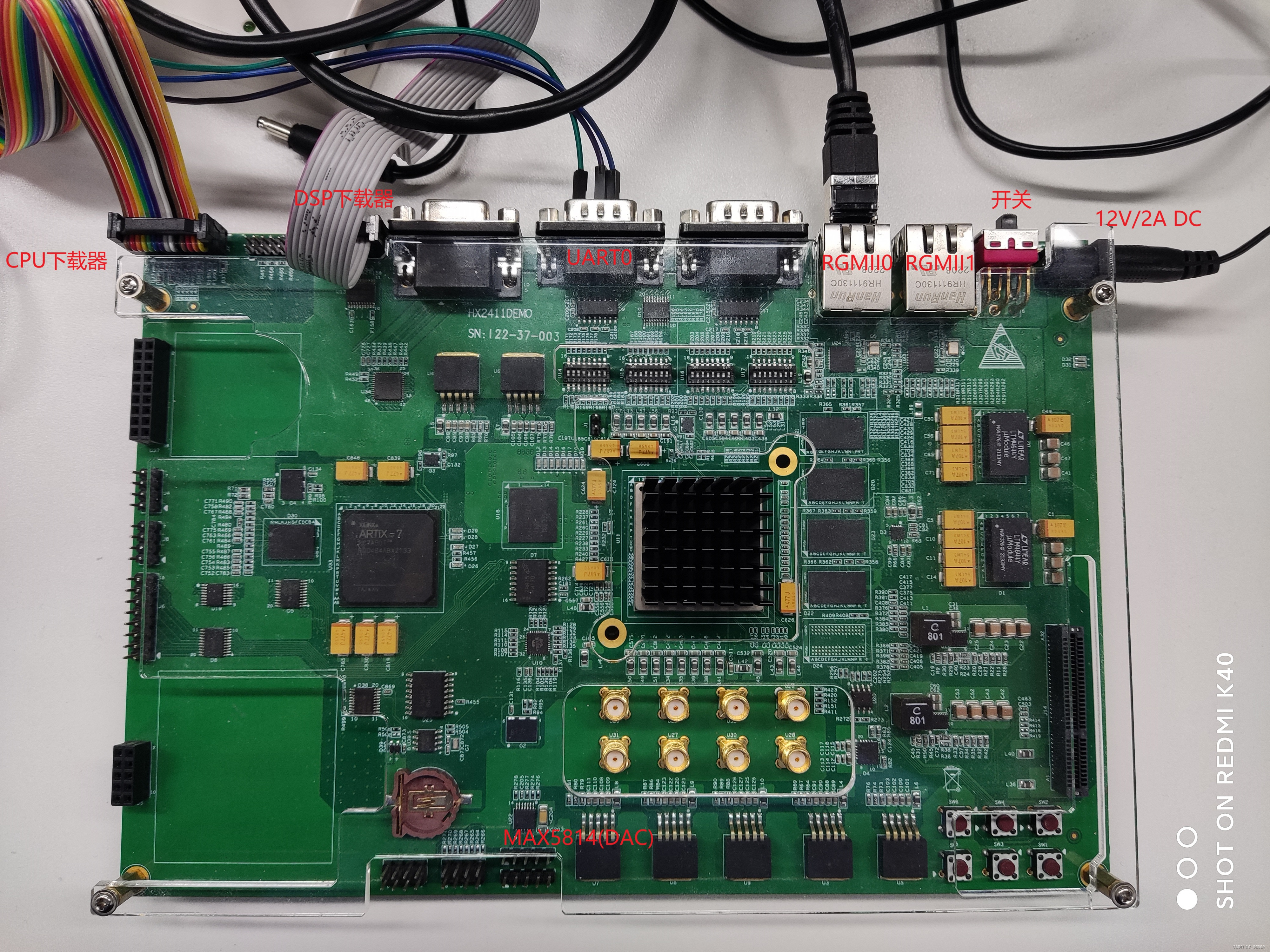

板卡图示

下图为HXDSP2441DEMO板,HXDSP2441DEMO板是围绕HXDSP2441构建的芯片演示验证平台。

板卡简介

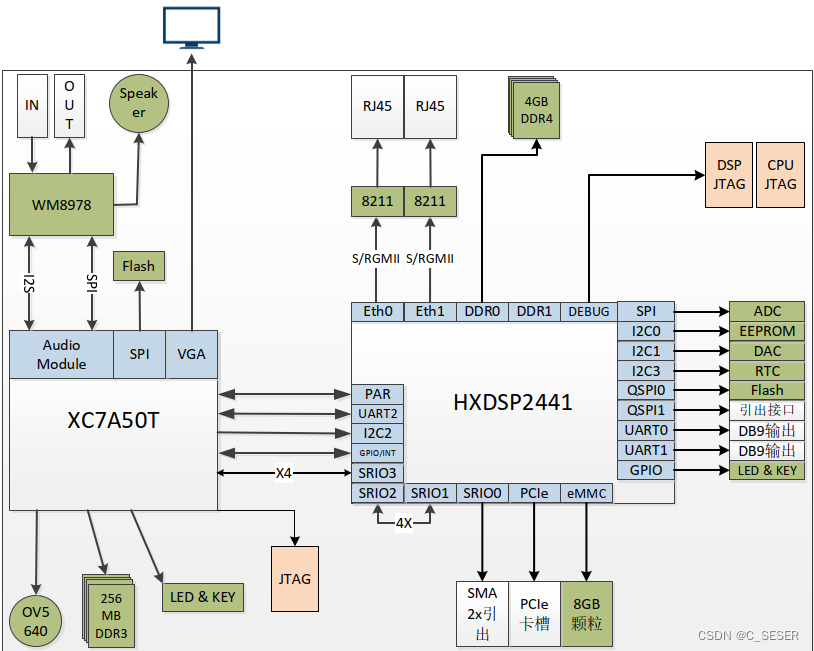

除了为HXDSP2441芯片提供供电、时钟、储存、网络及调试电路,来实现芯片最基本的功能,也添加了相关模块以搭建HXDSP2441的典型应用场景,如下图所示。

单纯进行HXDSP2441算力算法验证的用户,可以通过两路千兆以太网进行待处理数据的输入和处理后的数据输出。也可以通过引出的SRIO和PCIe链路,跨板进行数据交互,以构建更接近真实场景的工程原型。

1.添加FPGA音视频模块,使得音视频图像信号可以被FPGA采集,再通过SRIO或其他互联链路送至DSP进行处理,DSP处理后可以回传至FPGA进行音视频的播放。板载构建的这套系统(FPGA采集演示&DSP处理)方便用户进行各种图像及音视频算法的验证和教学。

2.PCIe卡槽为标准卡槽,基于Linux系统,可方便用户外联硬盘、网卡等标准PCIe外设,以拓展DEMO板硬件资源。

3.该板卡的技术指标如下所示。

处理能力

1片HXDSP2441高性能DSP的运算性能:350GFLOPs。

存储能力

DSP外挂1组4GB的DDR4,1片32MB的QSPIFlash,及一片8GB的

EMMC颗粒。

FPGA外挂1组256MB的DDR3,及1片32MB的SPIFlash。

传输带宽

板上DSP的SRIO0以SMA2X引出,支持数据带宽25Gbps跨板通信。

板上DSP的SRIO1与SRIO24X自环,方便用户学习与验证HXDSP2441的SRIO通信链路,数据带宽可达50Gbps。

板上DSP的SRIO3与FPGA4X相连,用于工程原型验证,带宽受限于FPGA,数据带宽可达25Gbps。

板上DSP的PCIe以GEN4插槽引出,数据带宽64Gbps。

板上DSP的两路千兆以太网通过RJ45引出,数据带宽2Gbps。

物理特性

尺寸:231.5mm×157.5mm;

调试器:J2连接HXDSP2441CPU调试器,J3连接HXDSP2441DSP调试器;J16连接FPGA调试器;

工作温度:.40℃~+70℃;

存储温度:.40℃~+70℃;

功耗:≤15W;

散热:支持风冷散热结构。

板卡硬件资源分配

本板卡 HXDSP2441 的硬件资源分配如下表所示

| 控制器 | 硬件资源分配 |

|---|---|

| ETH0/ETH1 | 通过 RTL8211 直联至RJ45 |

| DDR DDR0 | 外挂64.bit 4GB 颗粒(MT40A512M16LY);DDR1 悬空 |

| SPI | 连接ADC MAX11635 |

| I2C | (1) I2C0 连接EEPROM:M24M01 (2) I2C1 连接DAC:MAX5814 (3) I2C2 连接至FPGA (4) I2C3 连接 RTC:HYM8563 |

| QSPI | (1) QSPI0 连接 Flash:MT25QU256ABA8ESF (2) QSPI1 引出至J6 |

| UART | (1) UART0 以DB9 输出(J10) (2) UART1 以DB9 输出(J11) (3) UART2 连接至FPGA |

| GPIO/INT | (1) GPIO 部分连接LED、KEY (2) GPIO/INT 部分连接至FPGA |

| eMMC | 连接 8GB 颗粒(KLM8G1GETF) |

| PCIe | 以 GEN4 卡槽引出(J14) |

| SRIO | (1) SRIO0 以 SMA 2X 引出 (2) SRIO1 与 SRIO2 板板上 4X 自环 (3) SRIO3 4X 连接至FPGA |

| PAR | 连接至 FPGA |

引脚配置

拨码开关 U14、U15、U16 和U17 为HXDSP2441 的配置管脚,硬件设计向数

字标识拨为“1”。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!