「Verilog学习笔记」超前进位加法器

2023-12-27 14:30:55

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

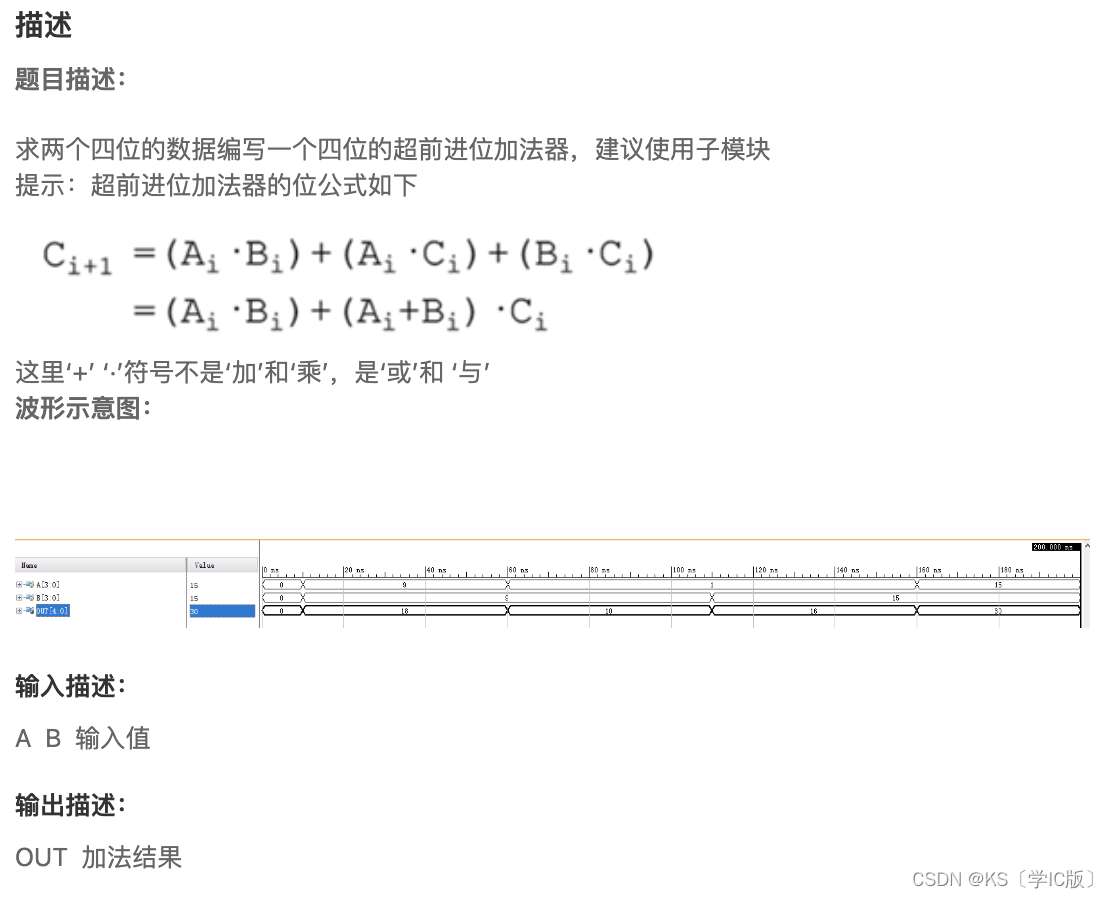

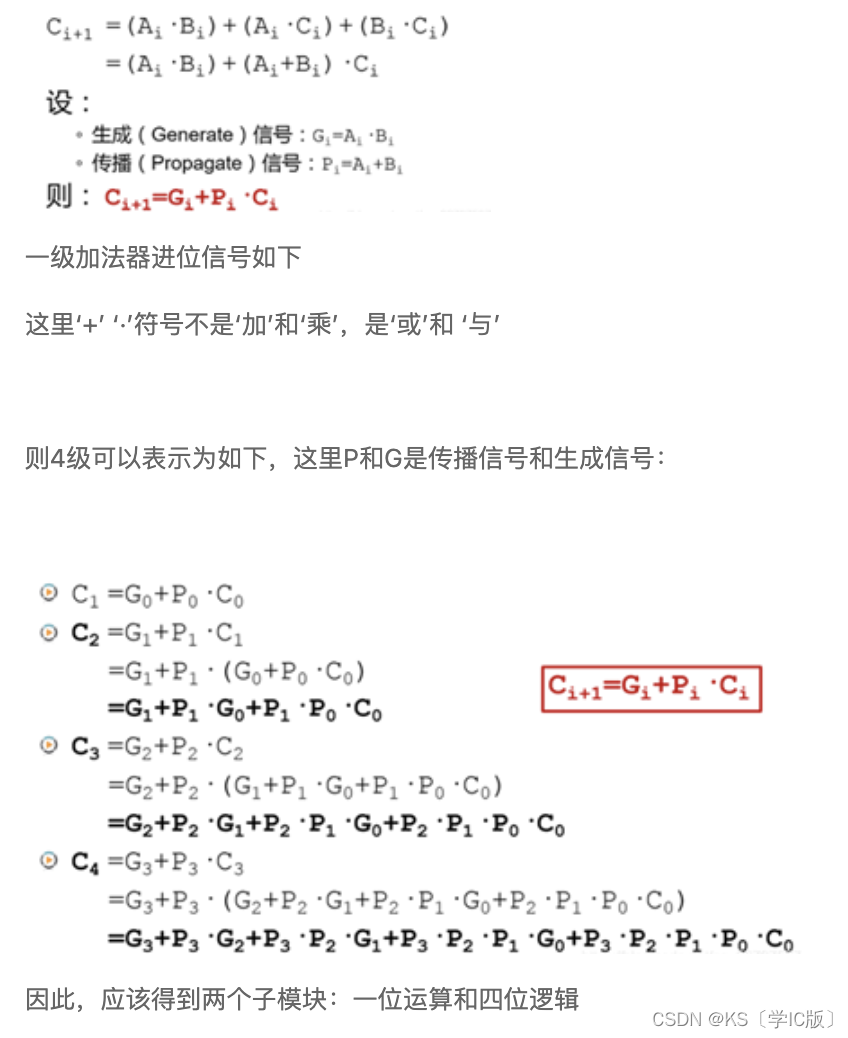

超前进位加法器的实质是:对于输出的每一位Si 其实都可以用Si = Ai ^ Bi ^ Cin来表示 我们需要做的只是判断加法结果的最高位该取几 例如本题中 输入的两个数A和B均为四位的二进制数 对于输出结果OUT的低四位都可以用上述公式计算 而最高位才是超前进位加法器需要解决的问题 即用更短的时间计算结果的最高位

`timescale 1ns/1ns

module huawei8//四位超前进位加法器

(

input wire [3:0]A,

input wire [3:0]B,

output wire [4:0]OUT

);

//*************code***********//

wire [3:0] G, P, F ;

wire [4:1] C ;

Add1 a1(.a(A[0]), .b(B[0]), .C_in(0), .f(F[0]), .g(G[0]), .p(P[0])) ;

genvar i ; // 在实例化过程中一般只能使用generate for块 不能直接使用for循环

generate

for (i = 1 ; i < 4 ; i = i + 1) begin : add_inst

Add1 a_i(.a(A[i]), .b(B[i]), .C_in(C[i]), .f(F[i]), .g(G[i]), .p(P[i])) ;

end

endgenerate

CLA_4 cla_inst(.P(P), .G(G), .C_in(0), .Ci(C), .Gm(), .Pm()) ;

assign OUT = {C[4], F} ; // 最高位和低四位

//*************code***********//

endmodule

//下面是两个子模块

module Add1

(

input a,

input b,

input C_in,

output f,

output g,

output p

);

assign f = a ^ b ^ C_in ;

assign g = a & b ;

assign p = a | b ;

endmodule

module CLA_4(

input [3:0]P,

input [3:0]G,

input C_in,

output [4:1]Ci,

output Gm,

output Pm

);

assign Ci[1] = G[0] | (P[0] & C_in);

assign Ci[2] = G[1] | (P[1] & Ci[1]) ;

assign Ci[3] = G[2] | (P[2] & Ci[2]) ;

assign Ci[4] = G[3] | (P[3] & Ci[3]) ;

endmodule

文章来源:https://blog.csdn.net/m0_54689021/article/details/135240441

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!