单总线cpu设计(包含定长指令周期和变长指令周期和现代时序设计)

来都来了点个赞收藏一下再走呗~~~🌹🌹🌹🌹🌹

一、定长指令周期cpu设计

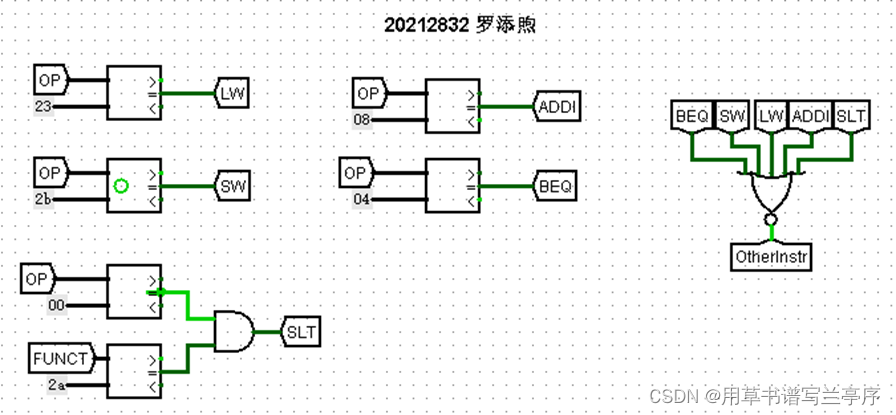

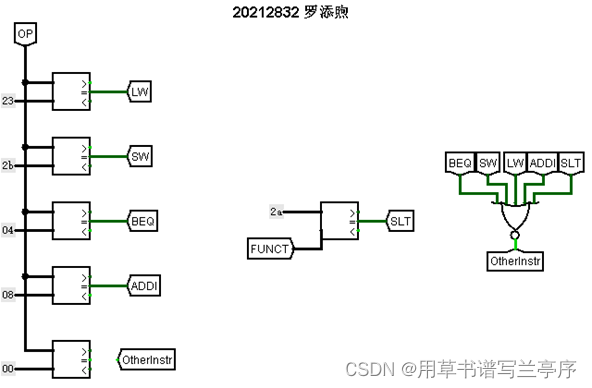

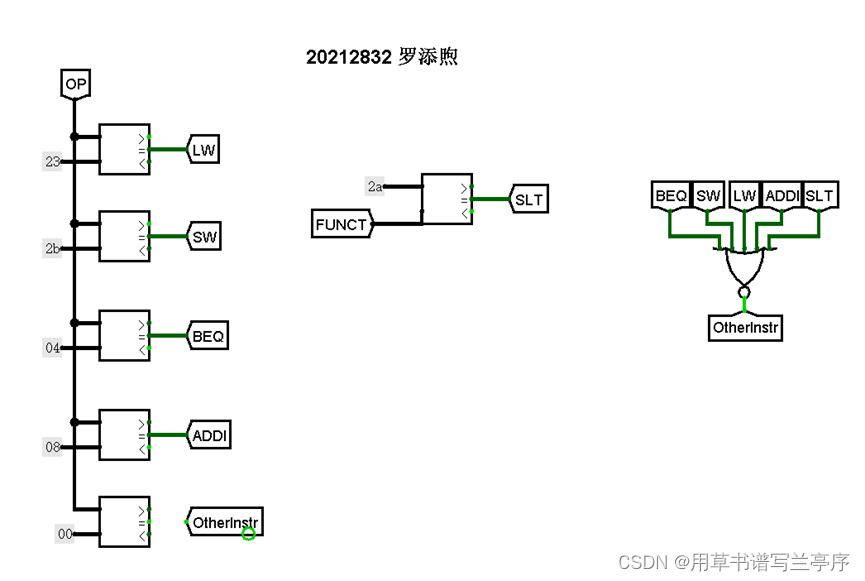

第1关:MIPS指令译码器设计

此实验就是只需要知道mips知道操作码op对应的值是什么就可以了,下面给出实验中用到的mips指令的op码的值如下表所示:

| Mips指令 | Op码 |

| LW | 100011(23) |

| SW | 101011(2b) |

| ADDI | 001000(08) |

| BEQ | 000100(04) |

| SLT | 000000(00) |

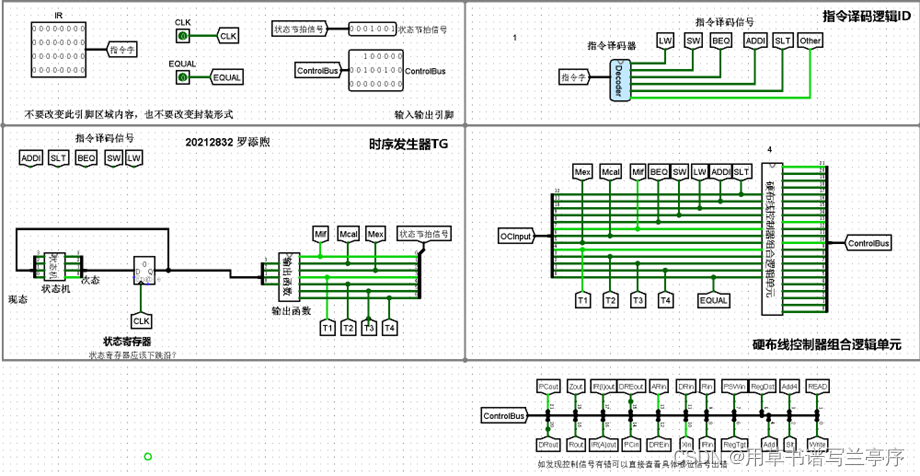

MIPS指令译码器电路图如图6.1所示:

图6.1 MIPS指令译码器电路图

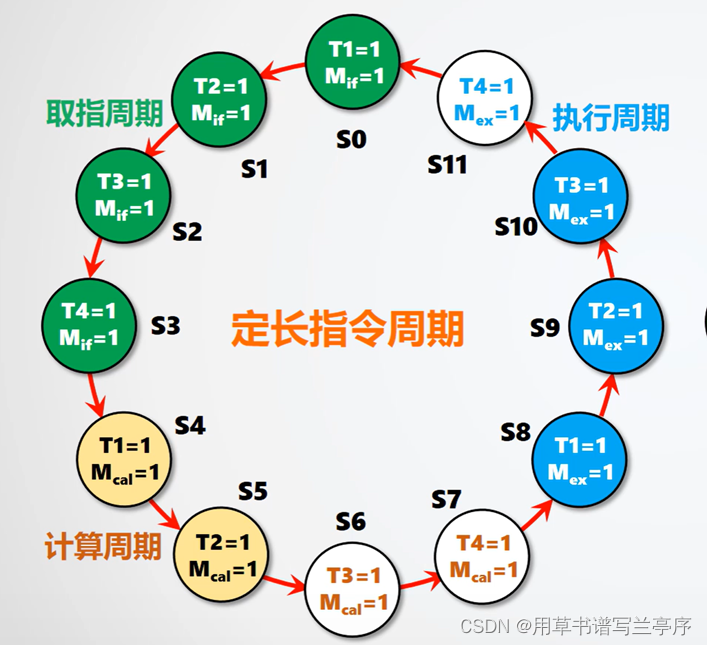

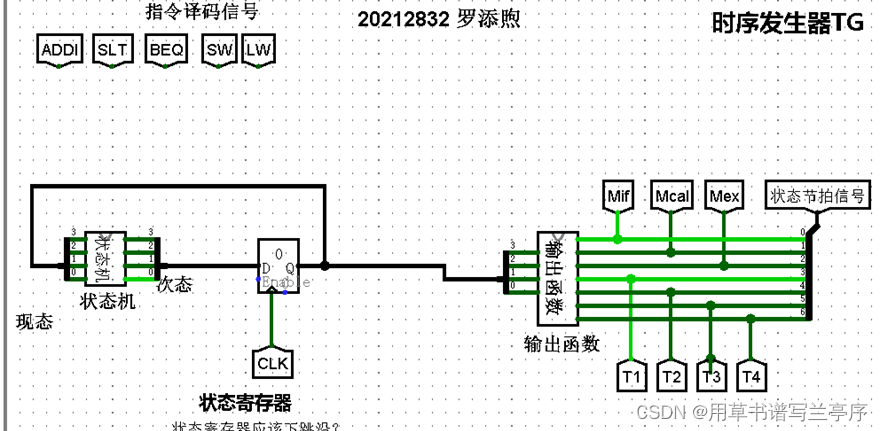

第2关:定长指令周期---时序发生器FSM设计

定长指令周期的状态转化机的状态转化如图6.2所示:

图6.2定长指令周期转化机

我们可以更具定长周期转化机的状态转化很容易的就可以填写出状态转化周期的execl表,从而得到逻辑生成函数实现自动生成电路,execl表如图6.3所示:

图6.3 定长指令周期转化execl表

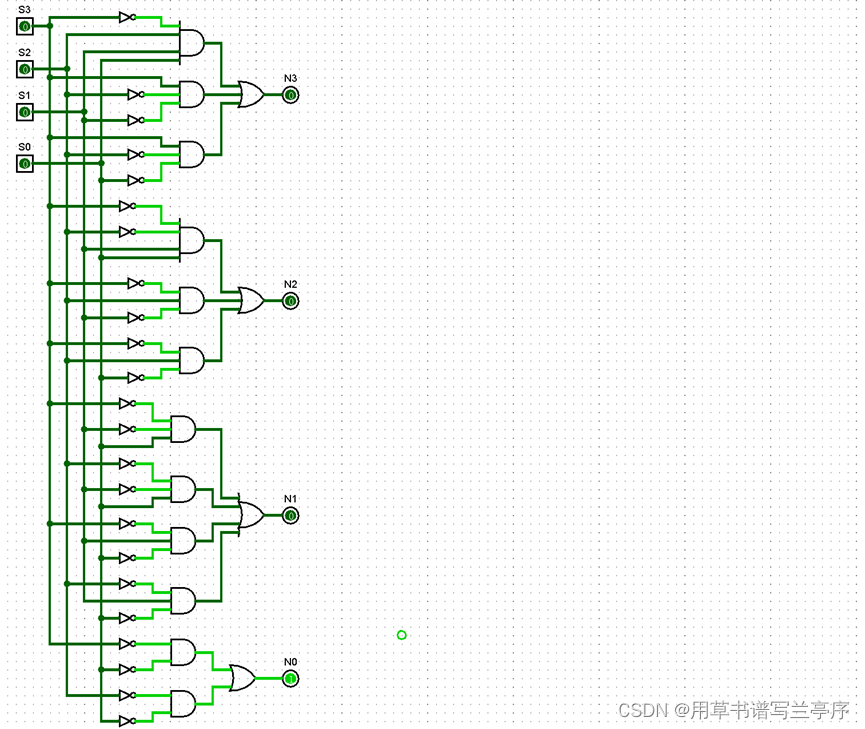

所以得到时序发生器状态机如图6.4所示:

图6.4 时序发生器状态机电路图

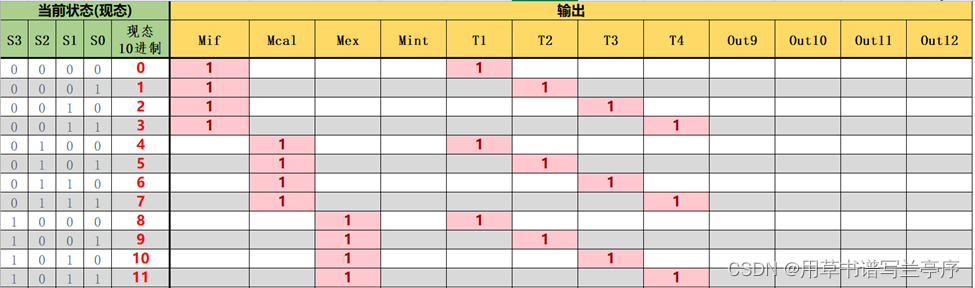

第3关:定长指令周期---时序发生器输出函数设计

?????? 根据状态转化图我们可以容易的填写输出函数的真值表,得到生成函数自动生成输出函数的逻辑电路,execl表如图6.5所示:

图6.5 输出函数execl表

?????? 由自动生成电路得到结果如图6.6所示:

图6.6 输出函数电路图

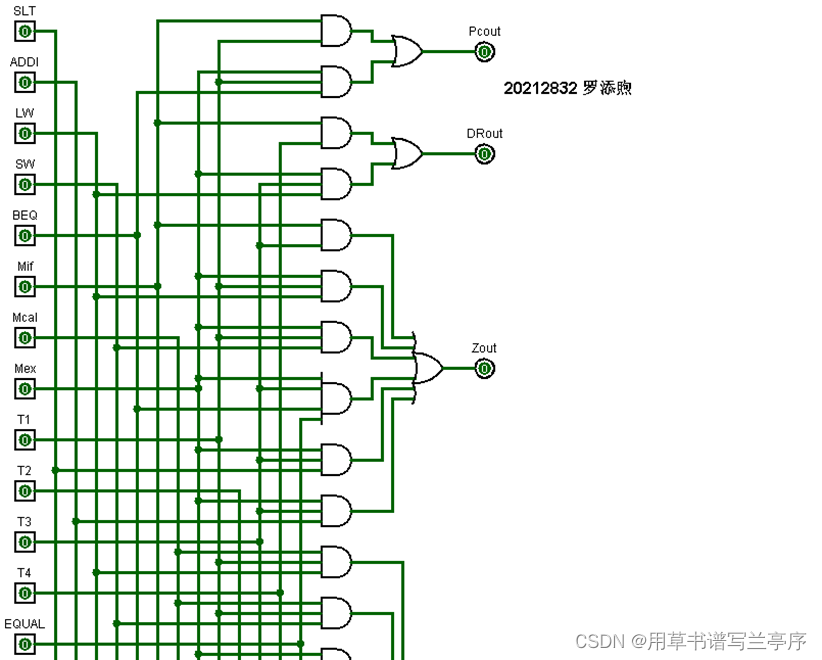

第4关:硬布线控制器组合逻辑单元

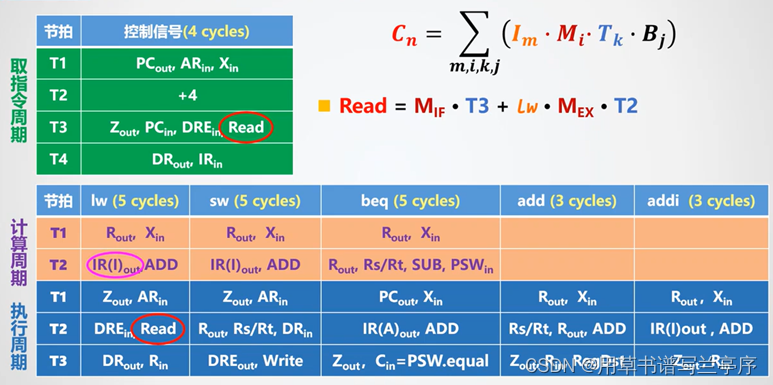

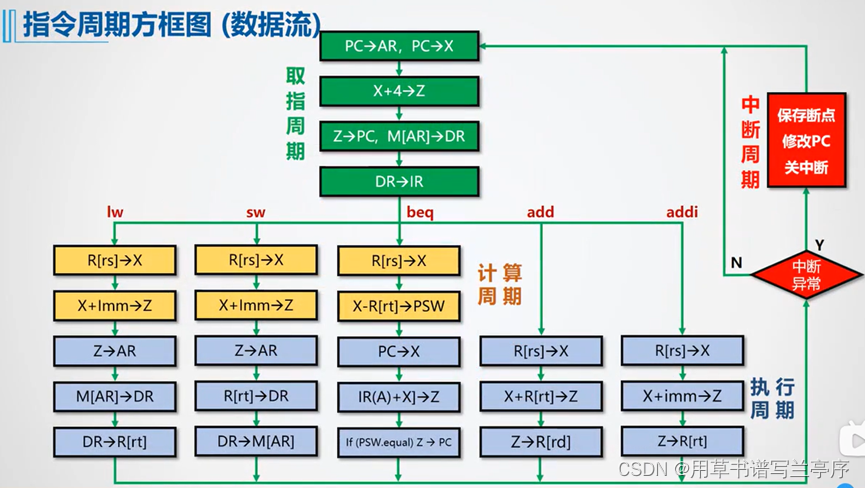

硬布线控制器的节拍的cpu指令周期(控制流)和指令周期方框图(数据流)如图6.7和6.8所示:

图6.7指令周期(控制流)

图6.8指令周期方框图(数据流)

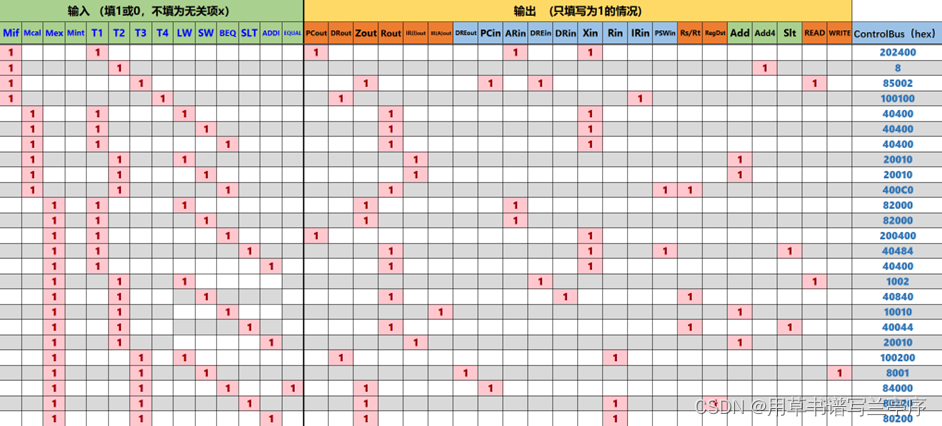

根据上面两个图我们可以填写出时序控制器的execl表格如图6.9所示:

图6.9 时序控制execl表

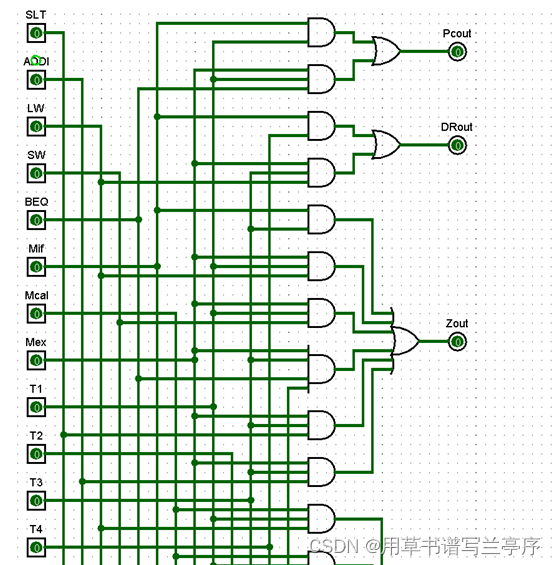

自动生成的电路图如图6.10所示:

图6.10 硬布线控制器电路图

第5关:定长指令周期---硬布线控制器设计

?????? 硬布线控制器设计如图6.11所示:

图6.11硬布线控制器电路图

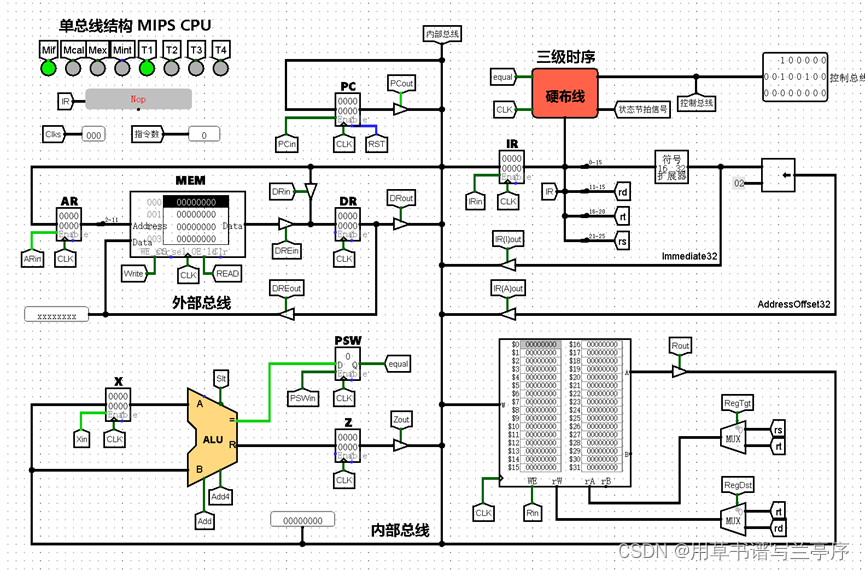

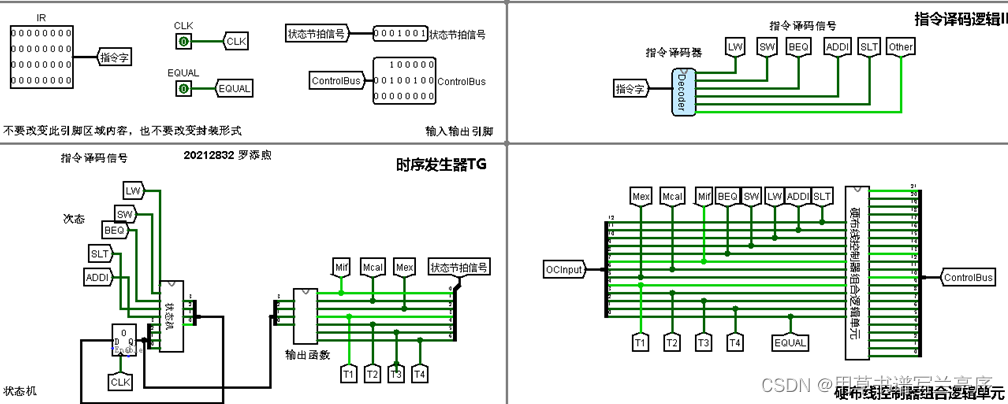

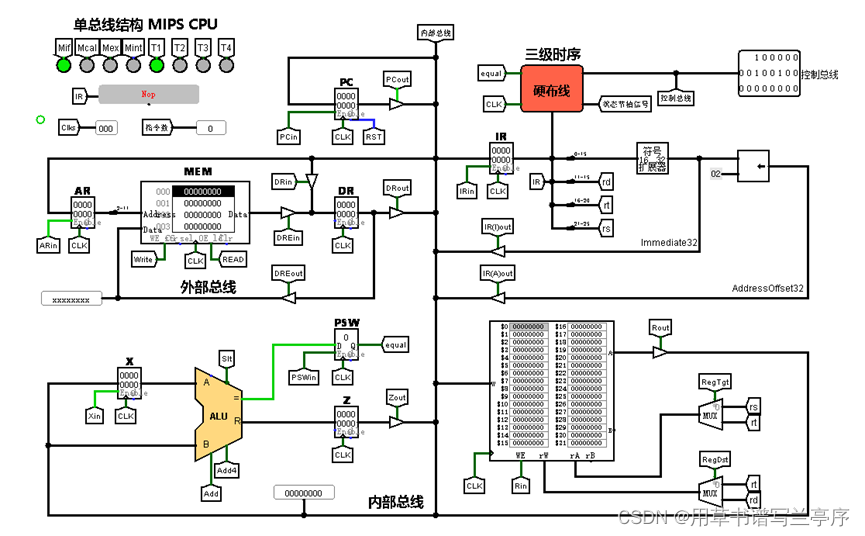

第6关:定长指令周期---单总线CPU设计

这个电路图是实验包中给出的具体的电路如图6.12所示:

图 6.12单总线cpu设计三、课程设计步骤

二、变长指令周期cpu设计

第1关:MIPS指令译码器设计

?????? Mips译码器和定长的是一样的如图6.1所示:

图6.1 MIPS指令译码器电路图

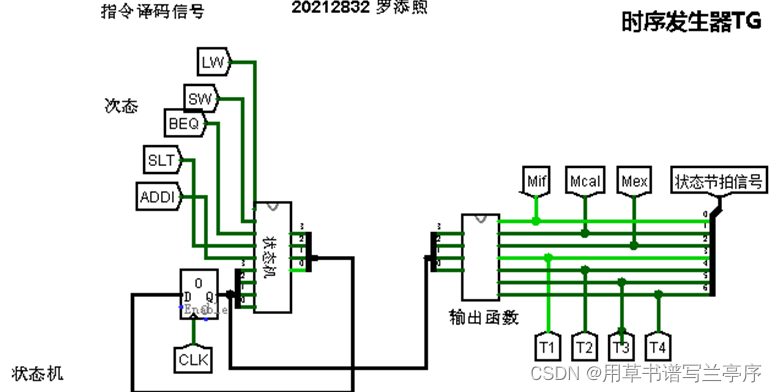

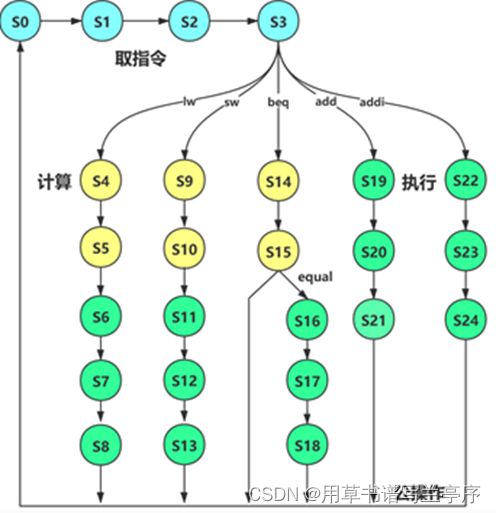

第2关:变长指令周期---时序发生器FSM设计

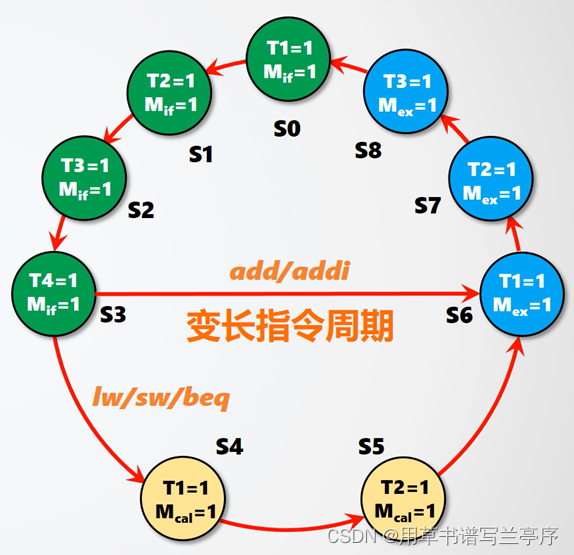

首先变长的状态机和定长的状态机是有区别的,所以我们需要根据变长的状态机的状态转化图如图6.2所示,填写execl表格自动生成电路。

图6.2 变长状态转化图

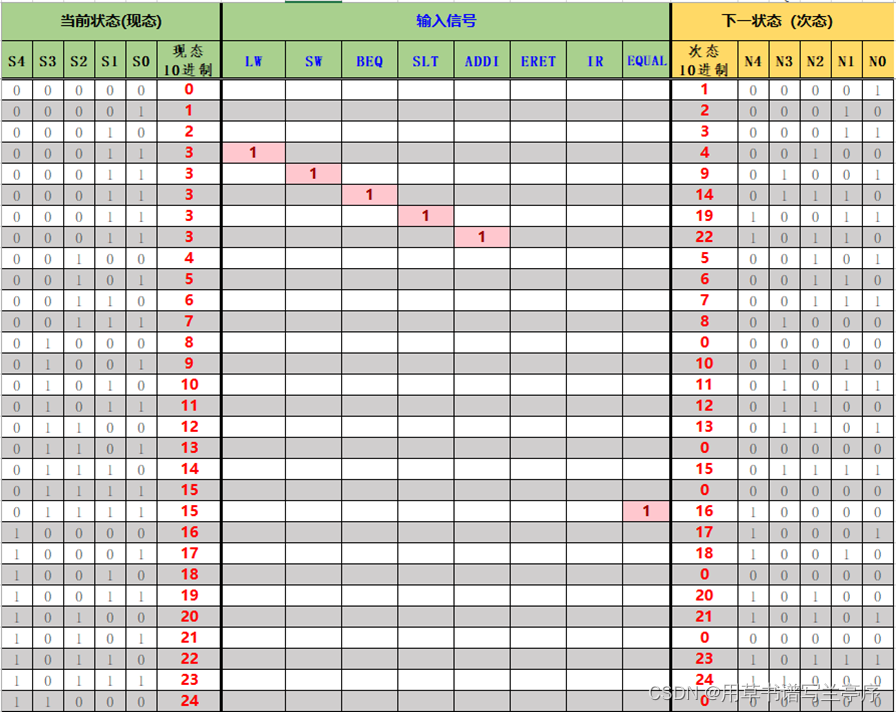

?????? 填写的execl表格如图6.3所示:

???????? 图6.3 execl表

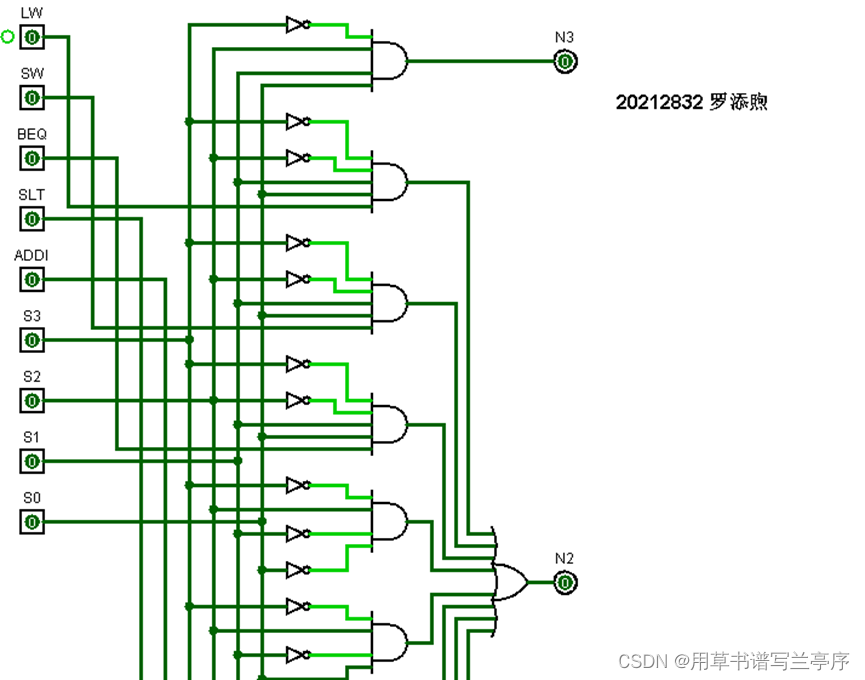

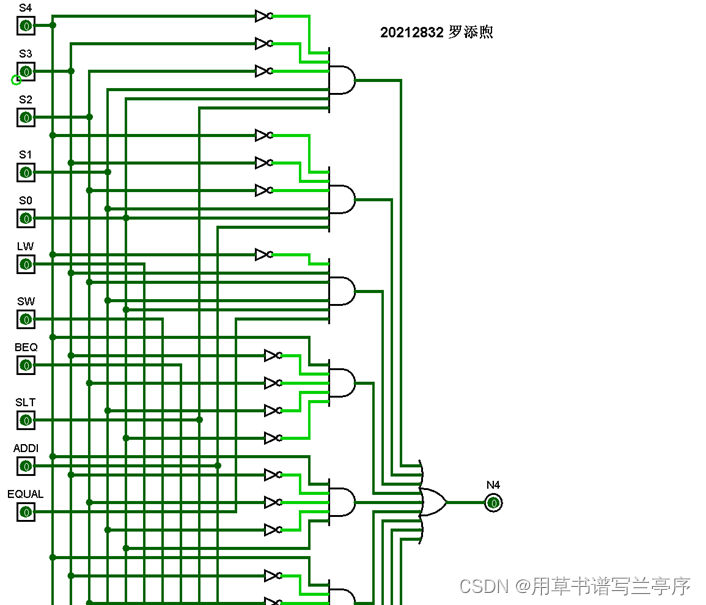

根据execl表自动生成的表达式自动生成的电路如图6.4所示:

图6.4生成电路(局部)

第3关:变长指令周期---时序发生器输出函数设计

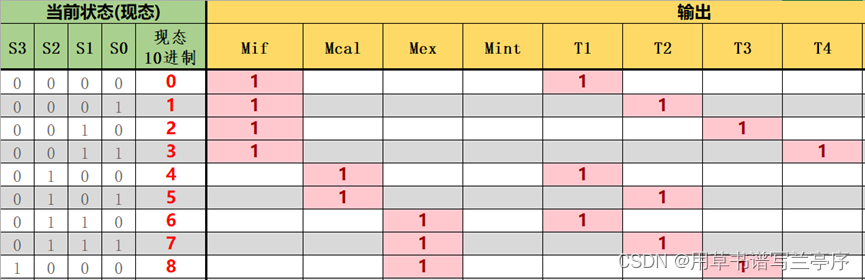

?????? 根据状态转化图我们可以很容易的填写出如图6.5所示的execl表格。

图6.5 输出函数execl表格

??????

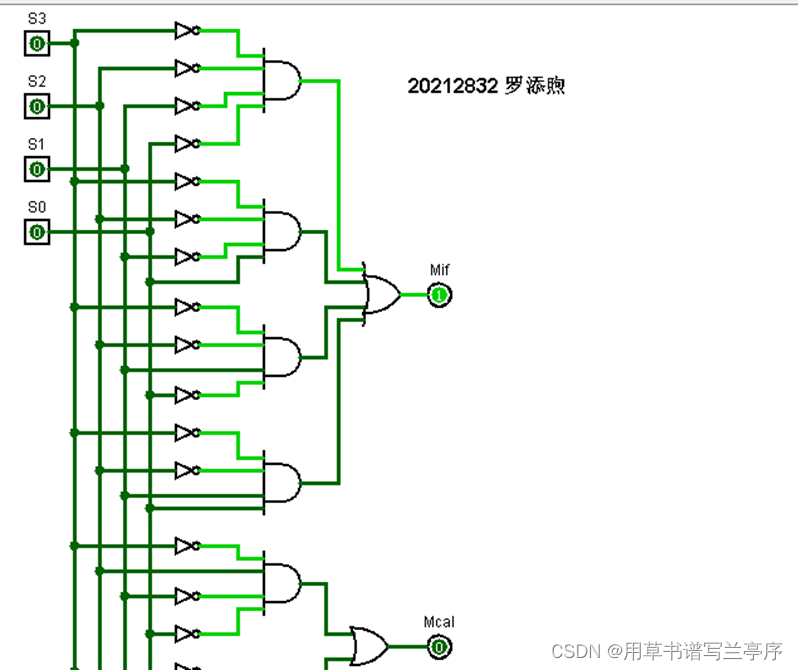

通过输出函数的自动生成的表达式我们可以得到如图6.6所示生成的电路:

图6.6 输出函数电路(局部)

第4关:硬布线控制器组合逻辑单元

因为变成的控制器实际上和变长的控制器是一样的所以我们可以直接使用定长的硬布线控制器组合逻辑单元的execl表直接来生成函数,硬布线控制器组合逻辑单元的电路图如图6.7所示:

图6.7 硬布线控制器组合逻辑单元电路图

第5关:变长指令周期---硬布线控制器设计

?????? 硬布线控制器很容易得出,但是要记住一点的就是要把状态机变成变长的状态机,电路如图6.8所示:

图6.8 硬布线控制器电路图

第6关:变长指令周期---单总线CPU设计

?????? 这个关卡也是由实验给出的电路,具体电路如图6.9所示:

图6.9 单总线CPU电路图

三、单总线CPU设计(现代时序)

第1关:MIPS指令译码器设计

?????? Mips指令译码器也就是和上面的实验中用到的一模一样,Mips指令译码器的电路图如图7.1所示:

图7.1 指令译码器电路图

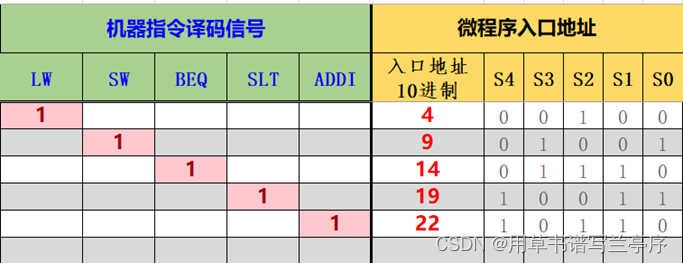

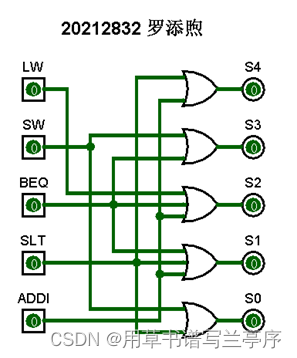

第2关:单总线CPU微程序入口查找逻辑

?????? 微程序的入口我们需要通过如图7.2所示的状态转化图来知道,并且把微程序入口的值填写到execl表中,采用自动生成逻辑表达式自动生成电路。

图7.2 微程序状态转化图

?????? 填写的execl表格如图7.3所示

图7.3 入口查找逻辑电路execl表格

?????? 生成的微程序入口查找逻辑电路如图7.4所示:

图7.3 入口查找逻辑电路图

第3关:单总线CPU微程序条件判别测试逻辑

生成电路的逻辑表达式

S0=P0

S1= P1 equal + P0 P1

自动生成的电路图如图7.4所示:

图7.4 微程序条件判别测试逻辑电路图

第4关:单总线CPU微程序控制器设计

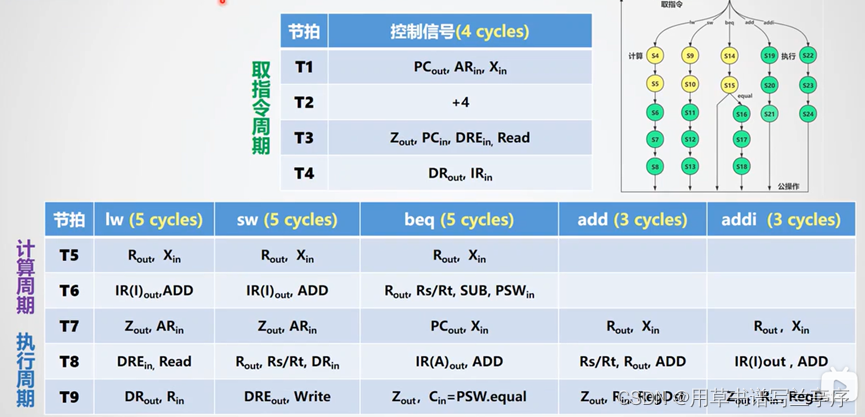

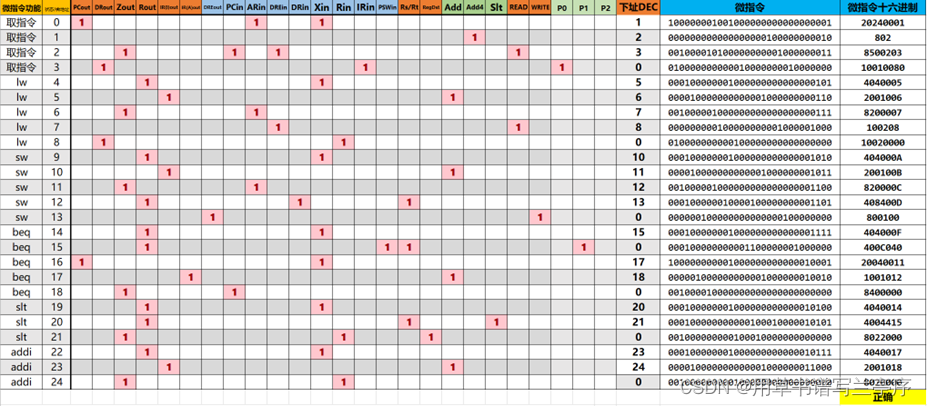

?????? 首先根据图7.2和如图7.5所示的指令周期节拍图,填写微程序自动生成的execl表格,execl表格如图7.6所示:

图7.5 指令周期图

图7.6微程序控制器execl表

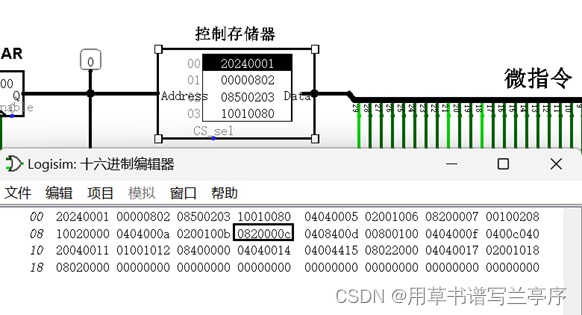

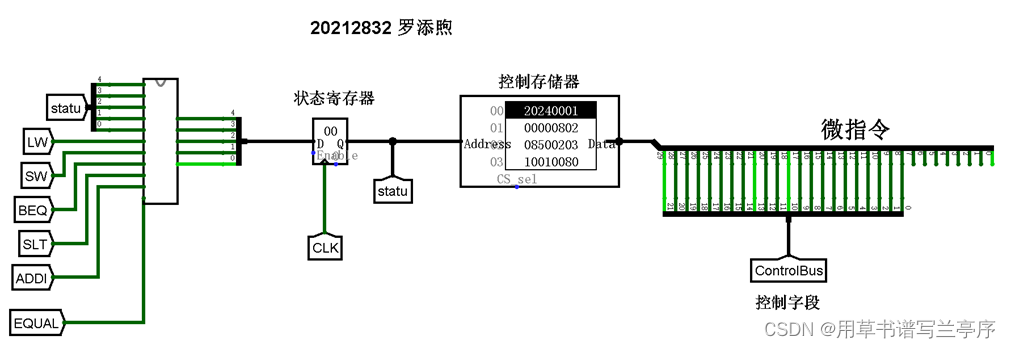

?????? 只需要把execl表中的微指令十六进制数复制到控制存储器中就可以完成此次实验了,控制存储器内如如图7.7所示:

图7.7 控制存储器内容

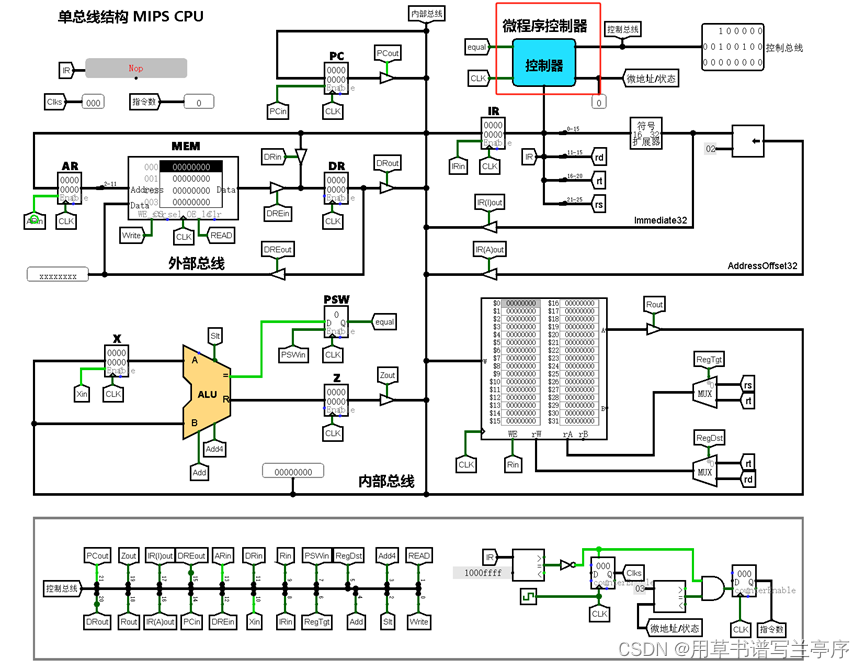

第5关:采用微程序的单总线CPU设计

在实现指令译码、现代时序状态机模块后,最终实现硬布线控制器的集成,在下图中完成硬布线控制器框架连接,注意硬布线控制器组合逻辑不需要实现直接采用微程序控制器的控制存储器代替即可,如图7.8所示:

图7.8 微程序的单总线CPU电路图

第6关:现代时序硬布线控制器状态机设计

?????? 首先我们需要根据图7.2填写硬布线控制器状态机execl表,结果图7.9所示:

图7.9 硬布线控制器状态机execl表

?????? 由execl表产生的自动生成式生成的电路如图7.10所示:

图7.10 硬布线控制器状态机电路图

第7关:现代时序硬布线控制器设计

现代时序硬布线控制器如图7.11所示:

??????

图7.11 现代时序硬布线控制器电路图

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!