硅像素传感器文献调研(四)

写在前面:

好喜欢这种短论文哈哈哈哈哈

感觉这篇文献已经提到了保护环的概念啊,只不过叫的是:场限制环。

1986——高压功率器件场终端横向掺杂的变化

?0.摘要

对于高压平面结提出了一个简单的新概念。通过在氧化物掩模中的小开口和随后的驱入注入来获得在结表面处的空间电荷区域的必要加宽,从而导致受控的掺杂剂分布。与其他平面结相比,该概念还产生了有源芯片面积的增益。实验结果表明了该概念的有效性。

1.引言

对于高压功率器件,需要1至10 kV范围内的阻断电压。对于这些器件中的许多,晶片被斜切以加宽空间电荷区并降低表面处的电场,以避免预击穿。只有当结深度足够大(通常为50-100 μ m)时,这种斜切过程才适用,因为只有这样,机械或化学斜切才变得足够可再现。

用IC技术生产的器件通常使用掺杂剂的注入和稍浅的结(1-20 μ m)。在这种情况下,斜切不再可行,因此高电压平面结变得合乎需要。

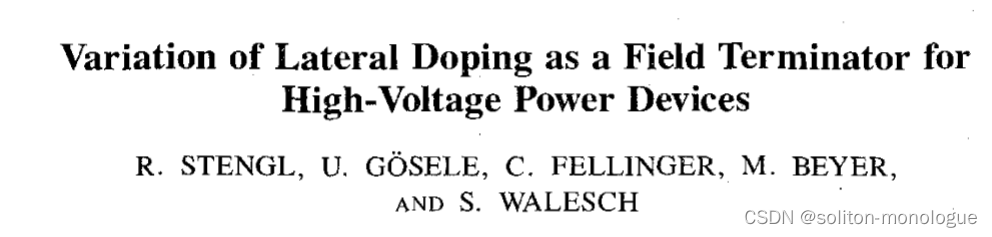

用于产生平面结的两种广泛使用的方法涉及“场板”[1]、[2]或“场限制环”;参见图1 [3]、[4]。击穿电压高于1 kV的场板很难实现,因为需要厚度大于8 μ m的氧化物。场环即使在更高电压下也没有这样的技术限制,但存在稳定性和设计问题。所有平面结的基本特征是在朝向器件边缘时降低面电荷密度。本文介绍了一种新的结构,实现了横向减少面电荷密度在一个相当自然的方式。

图1 场限环示意图? 电压UCA通过Δu1,Δu 2……逐步减小

2.新结构的基本要素

降低p-n结边缘处的面电荷密度的自然方式是与圆柱形(或球形)结相比在横向方向上非常缓慢地降低p区的掺杂剂量和穿透深度。这可以通过横向改变受主掺杂剂的注入剂量,然后进行驱入扩散来实现。为了完全有效,有效注入掺杂剂剂量(例如,在我们的情况下为硼)不需要低于1.3 × 10 12?* cm-2的约一半。该图由高斯定律的考虑得到,从高斯定律我们得出结论,带电掺杂剂的注入剂量对应于最大电场(Emax = 2 × 10 ~ 5 V)。在低掺杂硅(N,N,5 1 × m ~(-1))中,在载流子剧烈雪崩产生之前,通过

在(I)中,E是电场,E是介电常数,ρ是电荷密度,Q是总积分电荷,A是考虑的面积。从简单的静电考虑,我们还得出结论,当我们另外要求表面上的整个电压降发生在软p区,并且表面上的电场约为1e5V/cm(W是击穿时空间电荷区的宽度)时,这种低掺杂受主区域的横向扩展不需要超过0.5ΠW。此外,人们还需要大约1.5W的区域来平稳地从p-注入所需的高剂量下降到上述1.3×1012cm-2的最小剂量。

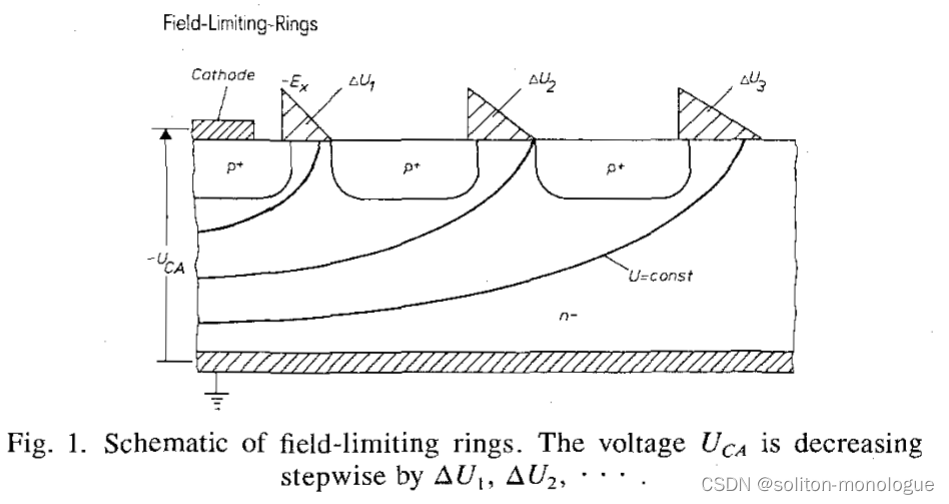

剂量必须变化的长度通常为几百微米。我们通过在用于掩蔽p注入的氧化物中打开小孔来实现横向减小的注入剂量。氧化物中的这些开口朝向结边缘变得越来越小。通过孔注入的掺杂剂在随后的驱入过程中充当源(图2)。

如果驱入时间足够长,则注入的掺杂剂的离散结构将被涂抹掉,并且可以实现具有非常低曲率的连续结。经由掩模氧化物中的离散开口的掺杂工艺不限于在前注入,而是还可以用于从气相或液体源掺杂剂扩散。

图2 VLD(横向掺杂变化)结构示意图。虚线是p-n结。

3.结果

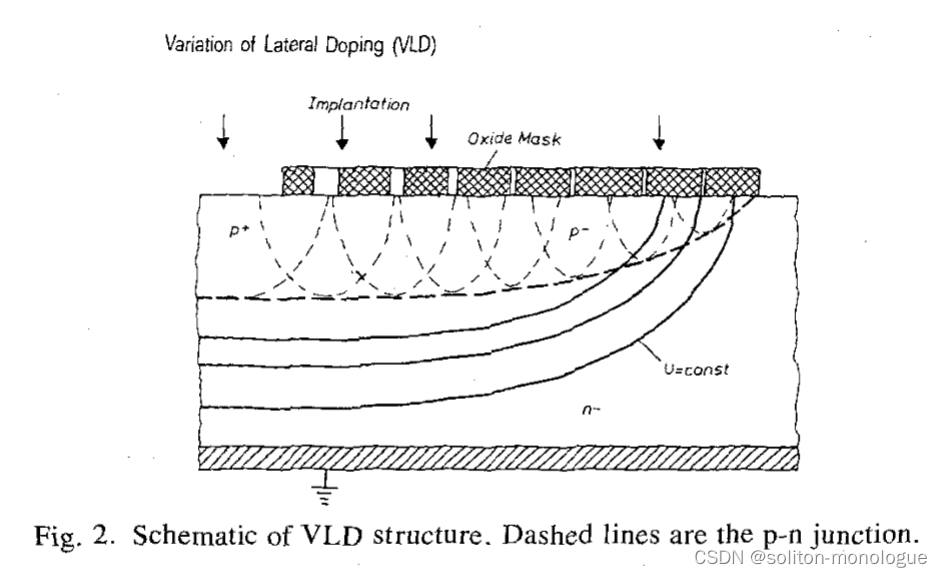

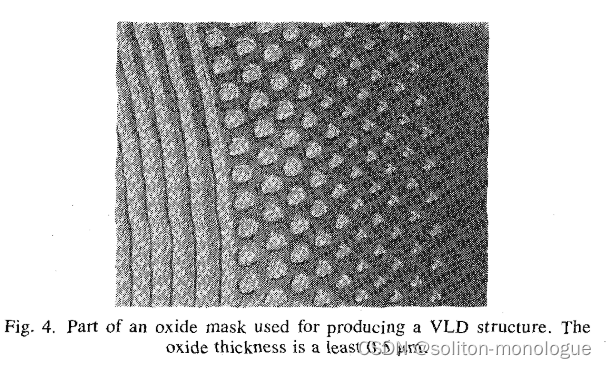

使用二维器件模拟程序BAMBI [5],在反向偏置条件下对不同衬底浓度和掺杂剂分布的p+-n二极管进行了计算机模拟。这些模拟的结果证实,低掺杂的p-区必须延伸到约三倍的空间电荷区,以达到超过90%的体积击穿电压。在优化设计的结构中,击穿发生在体中,并且表面处的电场相对较低。图3以等势线和等浓度线的形式显示了我们的第一批模拟结果之一(零等势线中的扭结是由于离散化造成的数值伪影)。还指示了本体内的电场的最大值。导致图3的掺杂分布是我们在60Ωcm磷掺杂衬底上对1cm2面积的芯片实验实现的第一个掺杂分布之一。在图4中,示出了用于在芯片边缘处进行硼注入的氧化物掩模的照片。植入后,在1200°C下进行持续数小时的驱入扩散。与这种新结构一起,在下文中表示为横向掺杂结构(VLD)的变型,在相同的晶片上制造了需要大约两倍空间的“经典”场环结构。场环被设计为提供给予大约相同的阻断电压。

图3?实曲线表示恒电位线.虚线表示等浓度线,+1013/cm 3和-2 X 1015cm 3。绘制的曲线示出了电场强度相等的线,2 × 10 5V/cm和1.8 × 10 ?5V/cm。

图4 生产VLD结构的部分氧化物掩膜,氧化物厚度至少为0.5um

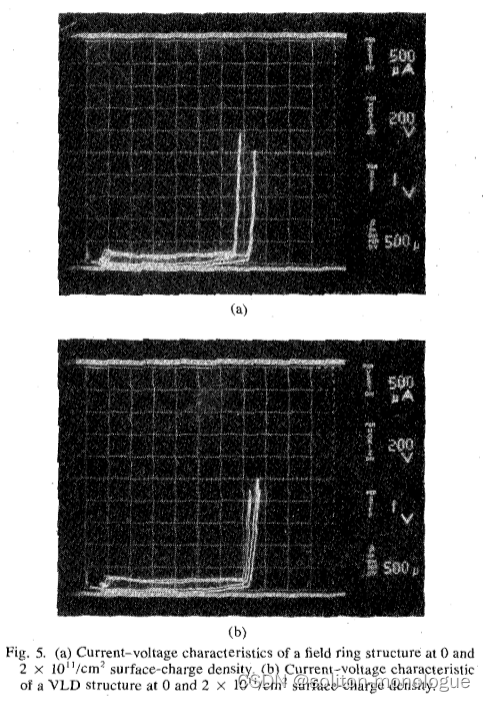

图5 (a)场环结构的电流-电压特性(0和2e11表面电荷浓度)(b)同等条件VLD结构的电流电压结构

VLD和场环结构都被表面上2.4 μ m厚的氧化物钝化。在图5(a)、(B)中,我们比较了两种结构相对于+2 X 1011/cm-1的场致表面电荷的稳定性。在这两种情况下,没有表面电荷时的阻断电压约为1500 V。当感应出正号的表面电荷时,VLD结构的击穿电压仅低约50 V,而场环的击穿电压降低150V.因此,VLD结构看起来对表面电荷不太敏感,至少只要面积表面电荷密度保持低于2X 10-cm-2。

4.总结

一个高压平面结实现了一个新的结构,结深约20 μ m。新的VLD结构显示出更好的表面稳定性,并比常用的场环结构需要更少的芯片面积。计算机模拟表明,VLD结构的稳定性主要是由于与场环的情况相反,表面电场很低,大部分表面压降发生在结的p侧。

新结构的优势应该用在5kV及以上的高压应用(低掺杂衬底)。最后,这些新结构的附加优点是用于掺杂的简单设计规则,例如,用于掩模氧化物中的开口,其可以容易地适应于更高的击穿电压。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!