从零开始学习vivado——day 2 3—8译码器的设计

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

研一从零开始学习verilog!!!此时不学何时学!

第一次写博客,以此激励自己努力学习!

我跟的视频教程是b站的一个up主,小梅哥爱漂流。

一、vivado是什么?

vivado是一个编译平台,可运行verilog代码,并且进行模拟仿真。

二、3-8译码器的设计

1.创建一个新的工程文件

默认RTL Project,器件随便选

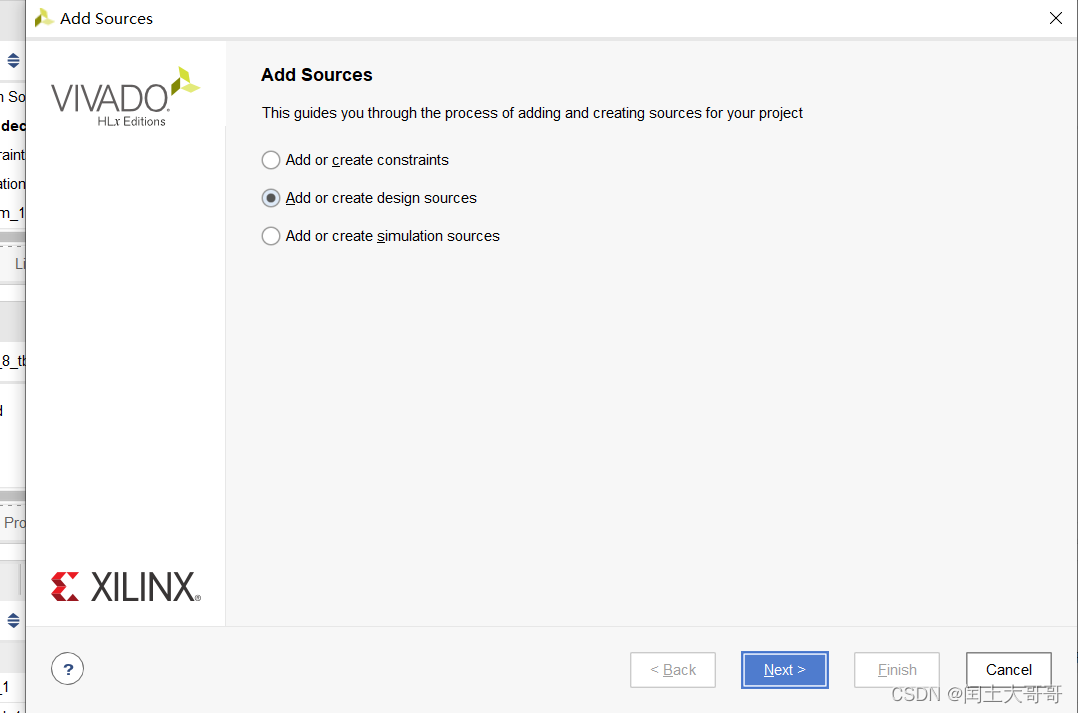

2.创建新的设计源文件

随后一路默认。开始手打代码!

2.设计源文件代码编译

①定义端口列表,因为是八个输出,所有定义的out位宽要8位,使用[7:0]来设定位宽为8位

module decoder3_8(

a,b,c,out

);

input a;

input b;

input c;

output reg [7:0]out;//位宽是8位,类型为reg类型,与always相配

//以always块描述的信号赋值,被赋值对象必须定义为reg类型

②利用always块编写3-8译码器

always@(*)//*代表a b c

case({a,b,c})//{a,b,c}变成了一个三位的信号,这种操作叫做位拼接

3'b000:out=8'b0000_0001;

3'b001:out=8'b0000_0010;

3'b010:out=8'b0000_0100;

3'b011:out=8'b0000_1000;

3'b100:out=8'b0001_0000;

3'b101:out=8'b0010_0000;

3'b110:out=8'b0100_0000;

3'b111:out=8'b1000_0000;

endcase

值得注意的是always@(*)与always@(*a,b,c)是等价的。

以及位拼接所使用的进制是可以更换的,

譬如

b代表二进制:3’b101 8’b0000_1010

d代表十进制:3’d5 8’d10

h代表十六进制: 8’ha

所以上述代码也可变成

3'd0:out=8'b0000_0001;

3'd1:out=8'b0000_0010;

3'd2:out=8'b0000_0100;

3'd3:out=8'b0000_1000;

3'd4:out=8'b0001_0000;

3'd5:out=8'b0010_0000;

3'd6:out=8'b0100_0000;

3'd7:out=8'b1000_0000;

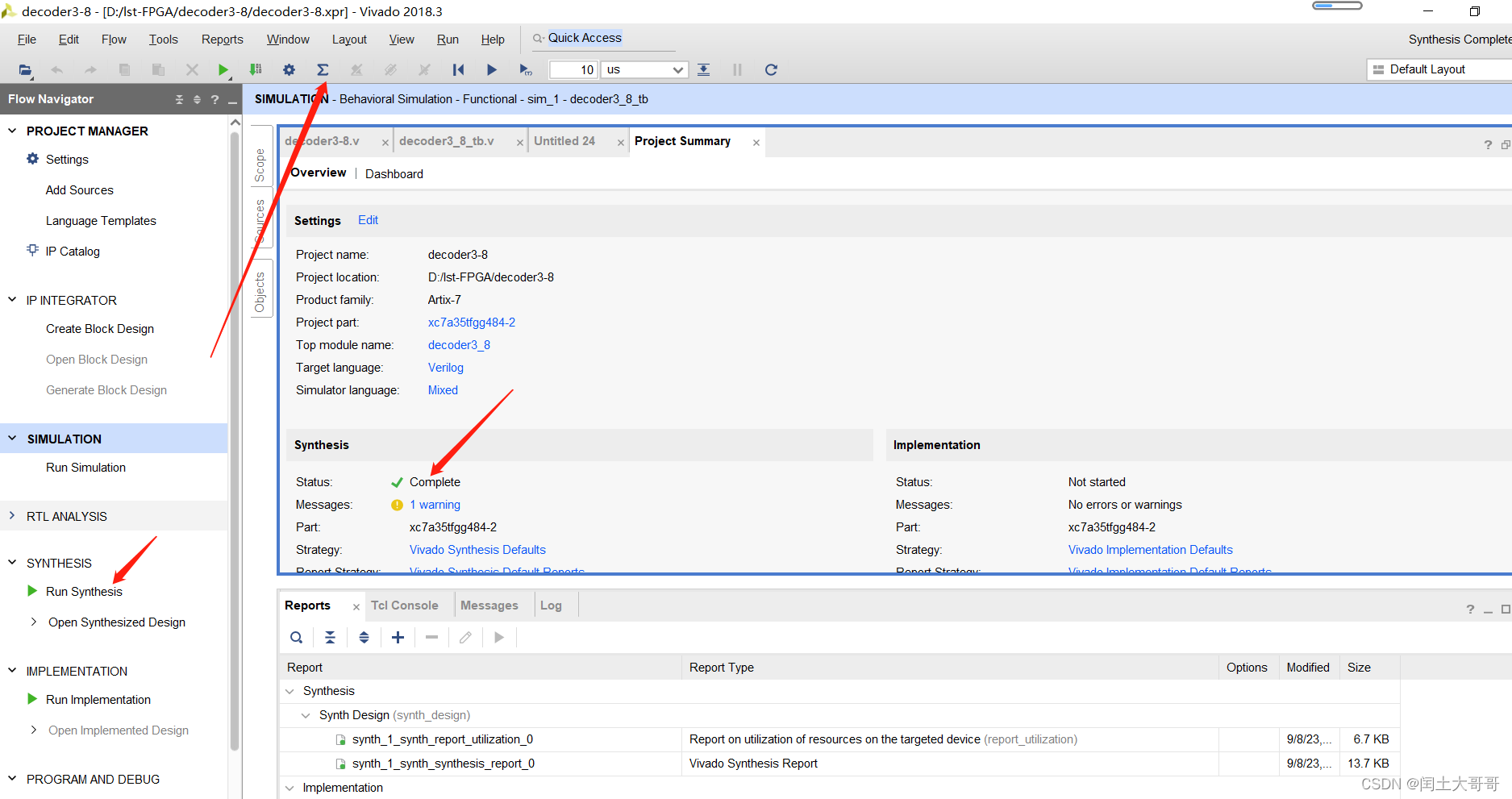

③分析和综合

没有报错,开始编写仿真源文件

3.设计仿真源文件

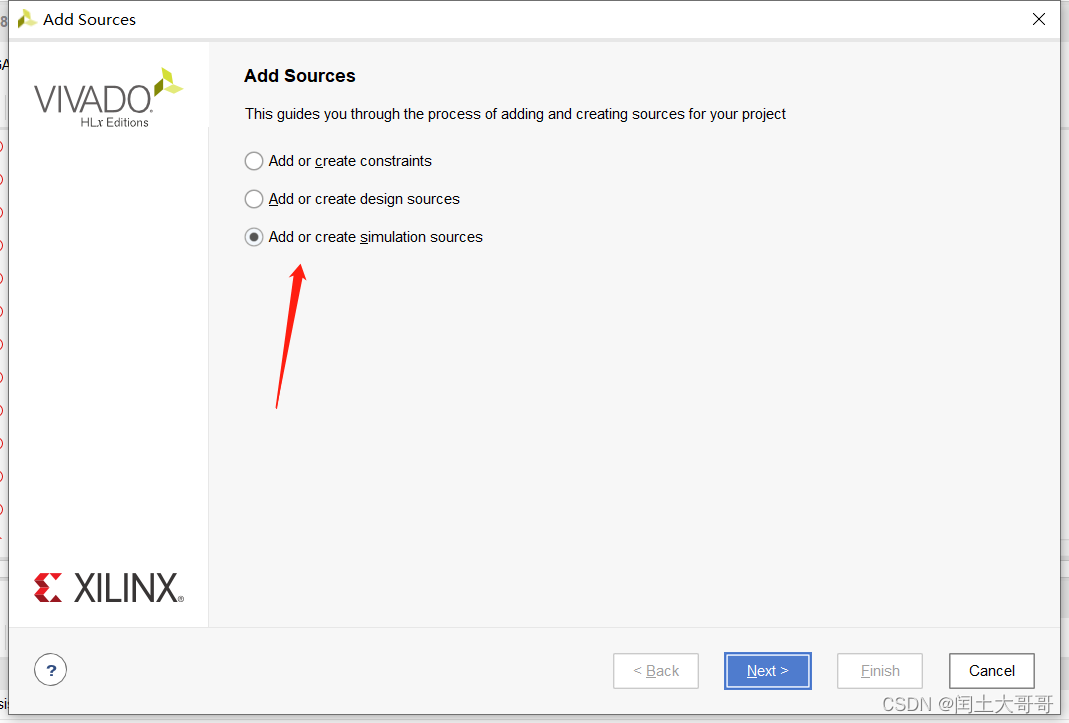

①新建仿真源文件

一路默认即可

②编译代码

首先编写时间尺度代码

`timescale 1ns/1ns

其次是例化

module decoder3_8_tb();

reg s_a;

reg s_b;

reg s_c;

wire [7:0]out;

decoder3_8 decoder3_8(

.a(s_a),

.b(s_b),

.c(s_c),

.out(out)

);

切记,再找接口的时候,变量前面要加个点,输入定义为reg型,输出定义为wire型

(3)变化高低电平

initial begin

s_a=0;s_b=0;s_c=0;

#200;

s_a=0;s_b=0;s_c=1;

#200;

s_a=0;s_b=1;s_c=0;

#200;

s_a=0;s_b=1;s_c=1;

#200;

s_a=1;s_b=0;s_c=0;

#200;

s_a=1;s_b=0;s_c=1;

#200;

s_a=1;s_b=1;s_c=0;

#200;

s_a=1;s_b=1;s_c=1;

#200;

$stop;//在simulation里面设置运行时间长一点,就不用按两次运行,然后用代码停止

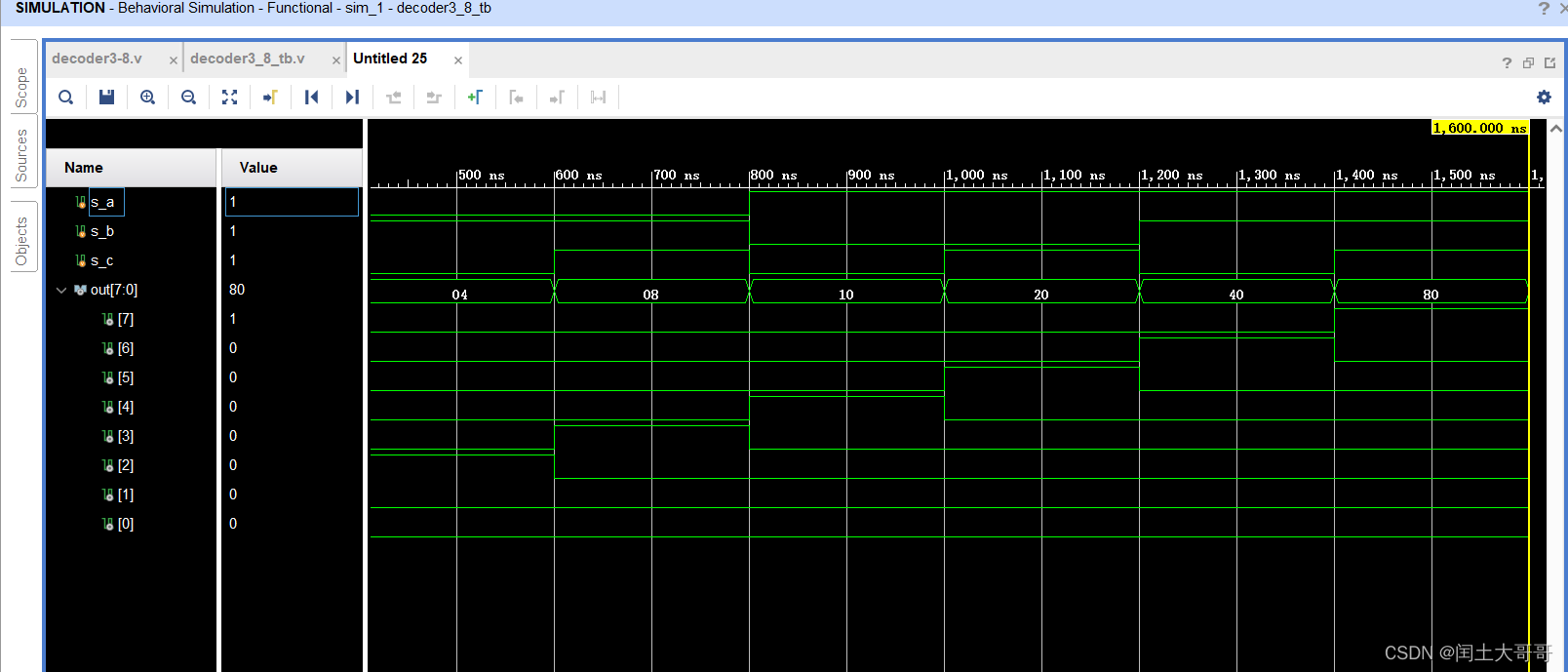

(4)代码整合并仿真

`timescale 1ns/1ns

module decoder3_8_tb();

reg s_a;

reg s_b;

reg s_c;

wire [7:0]out;

decoder3_8 decoder3_8(

.a(s_a),

.b(s_b),

.c(s_c),

.out(out)

);

initial begin

s_a=0;s_b=0;s_c=0;

#200;

s_a=0;s_b=0;s_c=1;

#200;

s_a=0;s_b=1;s_c=0;

#200;

s_a=0;s_b=1;s_c=1;

#200;

s_a=1;s_b=0;s_c=0;

#200;

s_a=1;s_b=0;s_c=1;

#200;

s_a=1;s_b=1;s_c=0;

#200;

s_a=1;s_b=1;s_c=1;

#200;

$stop;//在simulation里面设置运行时间长一点,就不用按两次运行,然后用代码停止

end

endmodule

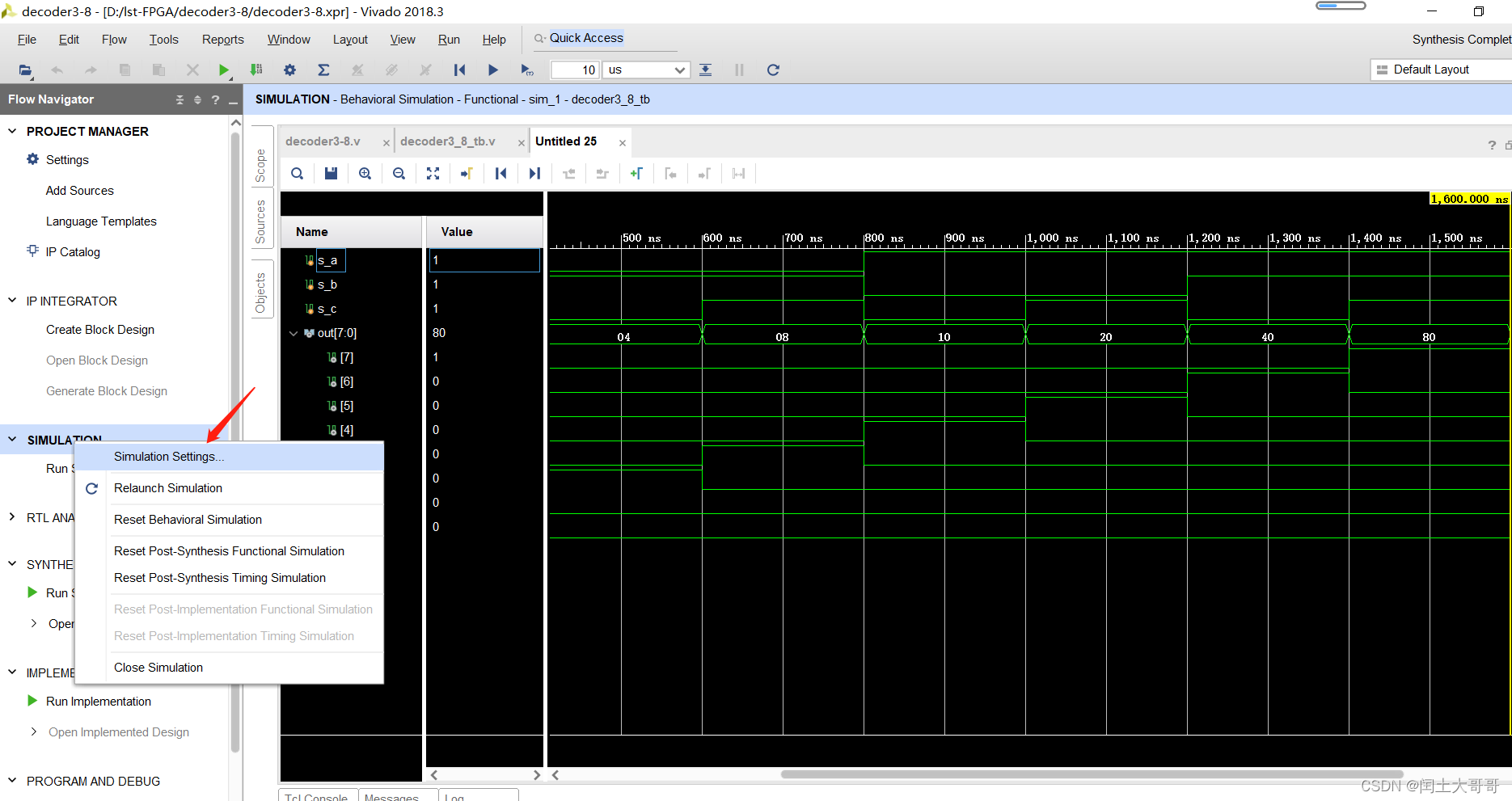

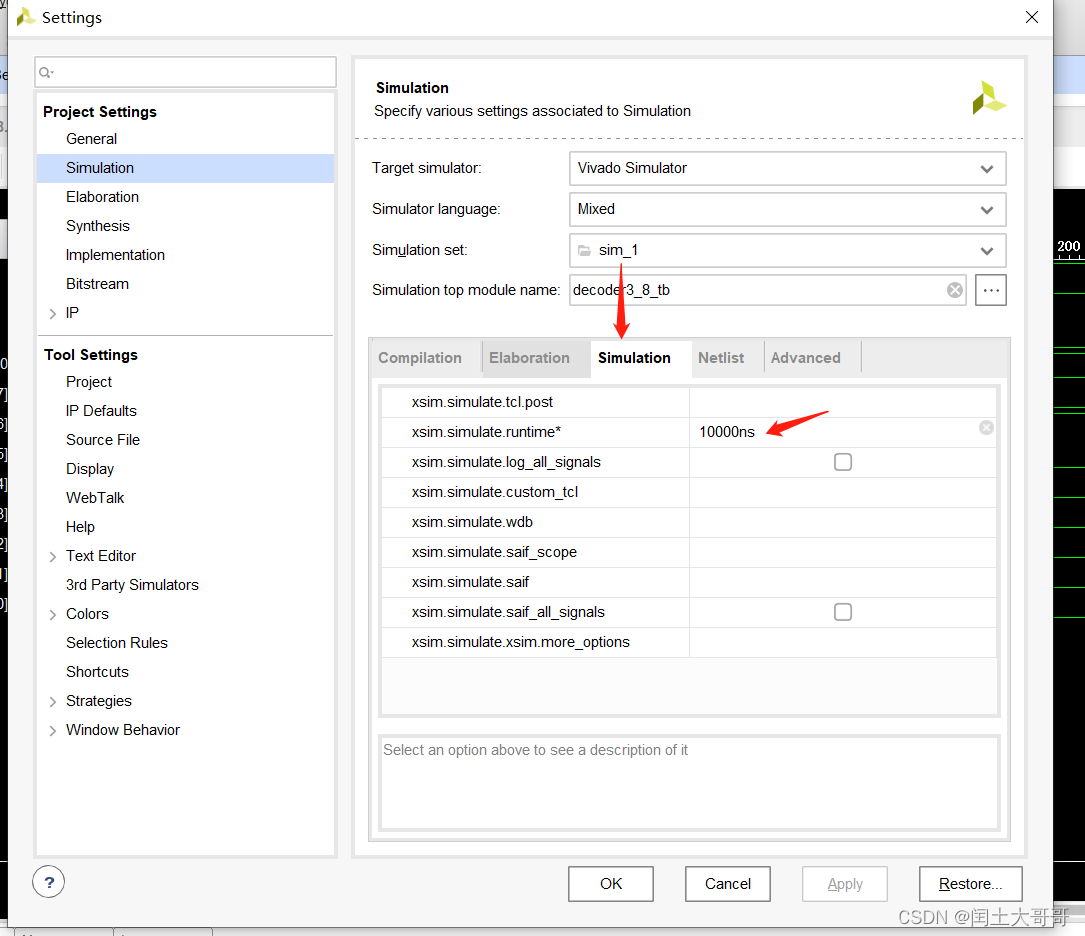

需要注意的是,做二选一多路器的时候也出现了运行一次只进行1000ns的情况,要想完全运行完一轮,需要按两次开始仿真。

这是由于vivado内部默认的就是一轮1000ns,我们可以重新设置一轮的时间,然后用stop来停止就行,具体如下:

自动停止代码如下:

$stop;//在simulation里面设置运行时间长一点,就不用按两次运行,然后用代码停止

总结

今天学习的是利用vivado编写一个简单的3-8译码器,并进行仿真。

新学的语法有

①always case语句,always块的输出必须是reg型

②如何在写变量的时候定义变量的位宽

③$stop;用于程序自动停止

④b代表二进制,d代表十进制,h代表十六进制

初步目标是跟着视频把基本操作过一遍,之后再统一学习verilog的语法。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!