Verilog Systemverilog define宏定义

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章前情预告

本篇文章介绍define宏定义,之前也学过,随着最近有更新的了解,记录下来想和大家分享,希望能帮助到大家!博客主要是从以下几个方面介绍,define是什么,用define宏定义的优点是什么,怎么用宏定义,宏定义使用的注意事项,宏定义的思想在其他方面的体现,宏定义的思想在生活中的联系,最后奉上写这篇博客的参考资料!

一、define是个啥?

define宏定义无论是在Verilog中还是Systemverilog中经常被用到,宏定义的格式是:

`define macro_name(formal_argu_list) macro_text

“‘define”是宏定义的标志,通知综合软件这是一个宏定义。请注意有开头符号“’”。

“macro_name”是宏定义的名称。

“macro_text”是宏定义被综合软件重新替代的内容。

“formal_argu_list”是宏定义可能的输入参数,里面可以有多个输入。在综合软件处理宏时,这些变量可以取代“macro_text”里对应的内容。当不需要参数时,可以省略这一项。

定义宏语句的最后是没有分号“;”的,这点我们要特别注意。如果不小心加了分号,那么这个分号会被综合软件视为“macro_text”的一部分参与替代工作。

二、为什么要使用define

define宏定义的本质就是用简短的字符代替一大段字符,可以起到减少代码量的作用,使代码看起来简洁,可以提高代码的移植性。

三、怎么使用define

说完什么是define与为什么要有这个东西,最重要的就是在实践中使用,不以应用为目的实践就是耍流氓!

例子1.define在Verilog中经常被用来定义变量的位宽:

`define BIT_WIDTH 8

reg [`BIT_WIDTH-1:0] bit_variable; //reg [7:0] bit_variable

在《SystemVerilog_3.1a》标准中,关于`define宏的描述如下所示:

例子2.define在Systemverilog中可以实现参数的传递,成为带参数的宏函数:

`define test_inst (A,B,C) \

.A``u_inst (A``inst), \

.B``u_inst (B``inst), \

.C``u_inst (C``inst)

.....

test_inst(a,b,c);

等价于:

.au_inst (ainst),

.bu_inst (binst),

.cu_inst (cinst)

注意事项:

1、

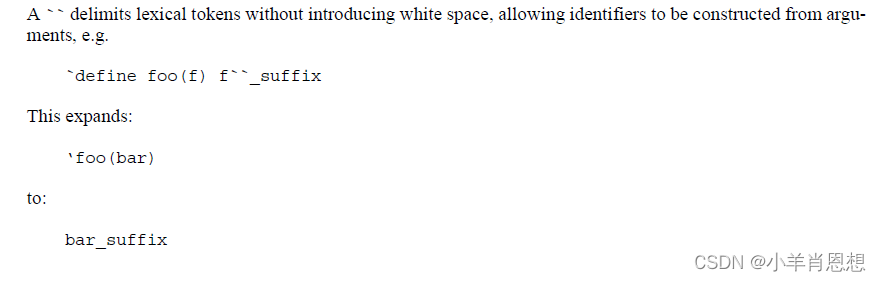

define在实现带参数的宏函数时,一定要加上``这个符号,综合软件只有在识别到这个符号时,才会将参数进行传递,这个符号相当于tcl脚本set a;中的set,Perl脚本中的$,只有出现这个关键符号软件才会进行变量替换;

2、

为了避免重复宏定义,可以使用下述方式进行定义:

`ifndef data_wdith

`define data_width

`endif

3、重要重要重要!

重要的事情说三遍,关于宏定义的有效范围,宏定义的有效范围从宏定义开始,对后续文件一直有效,直到另一个宏定义改变这个宏定义的值,所以这就要求按照一定的顺序进行文件的编译,例如:Verilog在module关键字之前一般都是include一些宏定义的文件,如果这些文件在endmodule后去包含,编译器就会因为找不到这些宏定义的替换内容而报错!

4、

宏定义本质上就是替换,编译不会对这个宏名称,做语法检查,只有当被替换的内容出错时,编译才会报错,所以在调用宏定义之前一定要告诉编译器宏定义的内容去哪里寻找,Verilog是通过include、incdir这个关键字去寻找,C语言调用子函数通过跳转地址,跳转到实际的子函数中去执行,一句话:如果替换,就得告诉编译器去哪里找!

四、define的横向拓展

define宏定义的本质就是替换,这种替换就是用更少的信息表示更多的信息,与之原理相同的还包括Systemverilog的interface,C语言的子函数;

五、define思想在生活中的体现!

有句话怎么讲的,”艺术来源于生活“,技术与生活也息息相关,define的思想个人感觉在生活中处处可见,比如你去买了苹果,你妈问你买的啥,你回答买的水果,你爸买的西瓜,你妈问你买的啥,你爸回答水果,都是一样的,好比水果这个宏定义在你那里被定义成了苹果,在你爸那里被定义成了西瓜,宏定义的名称不重要,重要的是定义的内容,一千个人眼里有一千个哈姆雷特,一千个人眼里有一千个宏定义内容!

六、结论

前面强调的按一定顺序编译的问题,Makefile可以实现确保编译的顺序问题,关于Makefile的描写下一篇文章见!

七、参考资料

参考资料1 :verilog 宏之define

参考资料2:Systemverilog 宏定义 define

八、交个朋友

博主写文章有很多不足之处,欢迎各位大佬多多评论留言批评指正!在博文中放置大量图片是因为思考快与慢中介绍了一个启动效应,希望大家在看到这些知识的时候还可以拥有乐趣,拥有视觉的冲击,也希望这个文章能够真正帮助到大家!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!