【xdma】 pcie.bar设置

2023-12-27 14:22:36

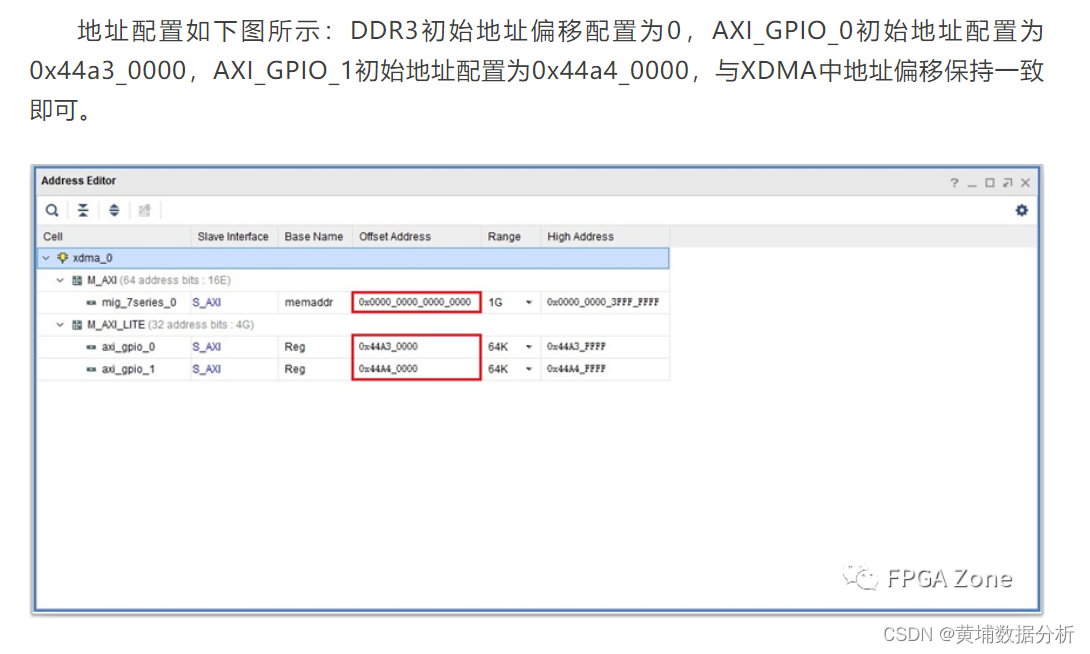

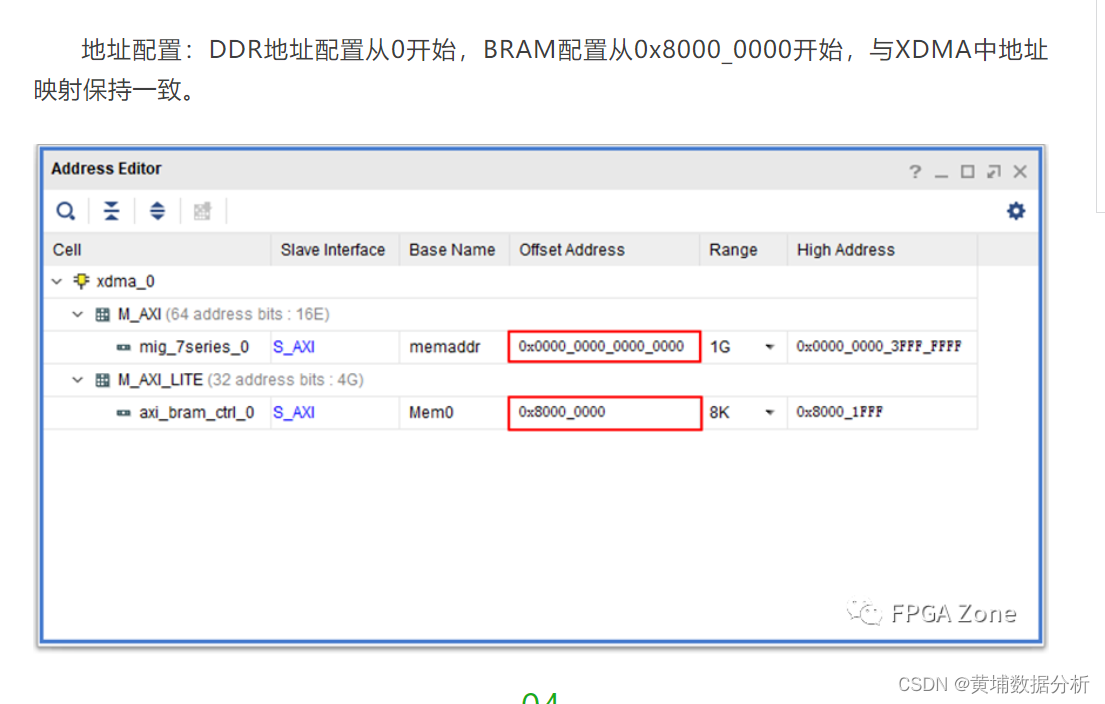

两者保持一致

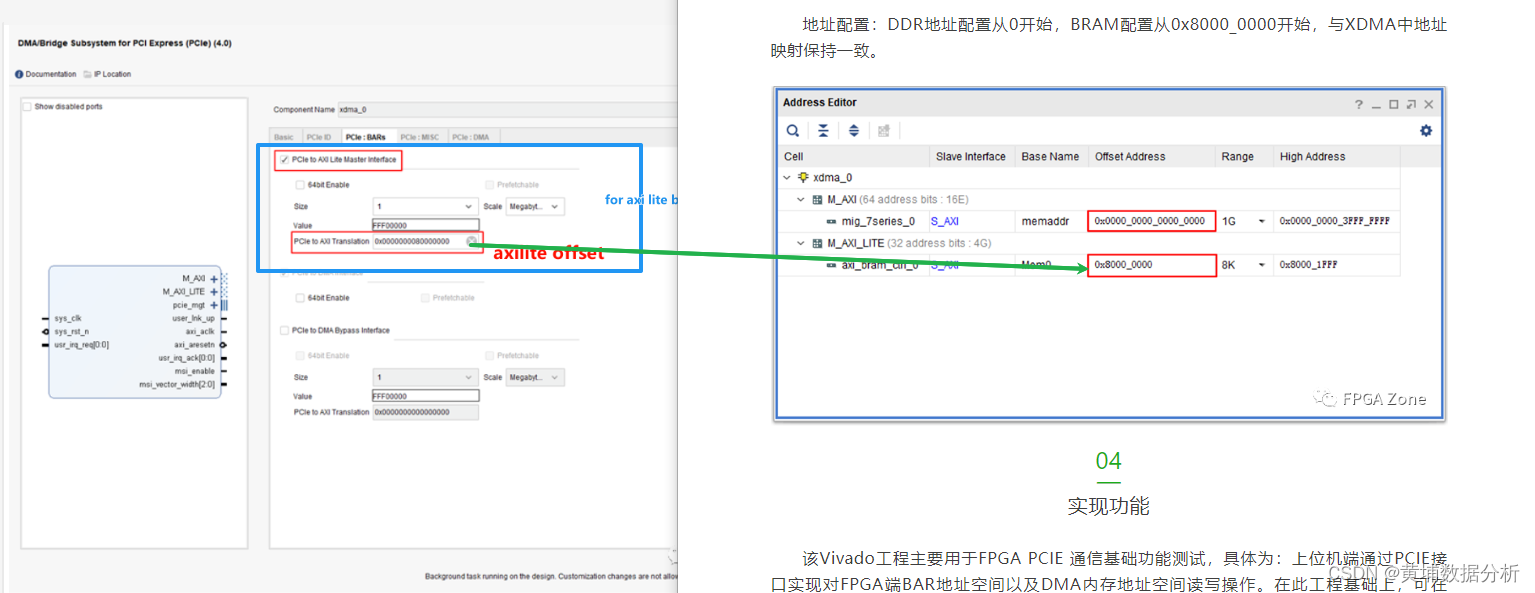

读写部分分为两种,一种是数据的读写,另一种是配置数据的读写,在数据读写部分,DMA通过MIG控制DDR完成数据读写。配置数据读写通过与BRAM通过AXI-lite总线连接完成,XDMA将PCIe配置信息存在BRAM,在进行配置信息读写时,将传入主机映射到用户逻辑的地址,然后与偏移地址处理(物理地址=段地址<<4+偏移地址),所以在bram设置时需要将其偏移地址设置的与主机地址映射的偏移地址相同。

对于DDR则不必,设置的话还减少了可使用的内存空间,只是一个袋子,写在哪里就从哪里读取即可,必须设置为0。

此处将配置信息存储到BRAM,通过AXI-lite总线读写Bram。

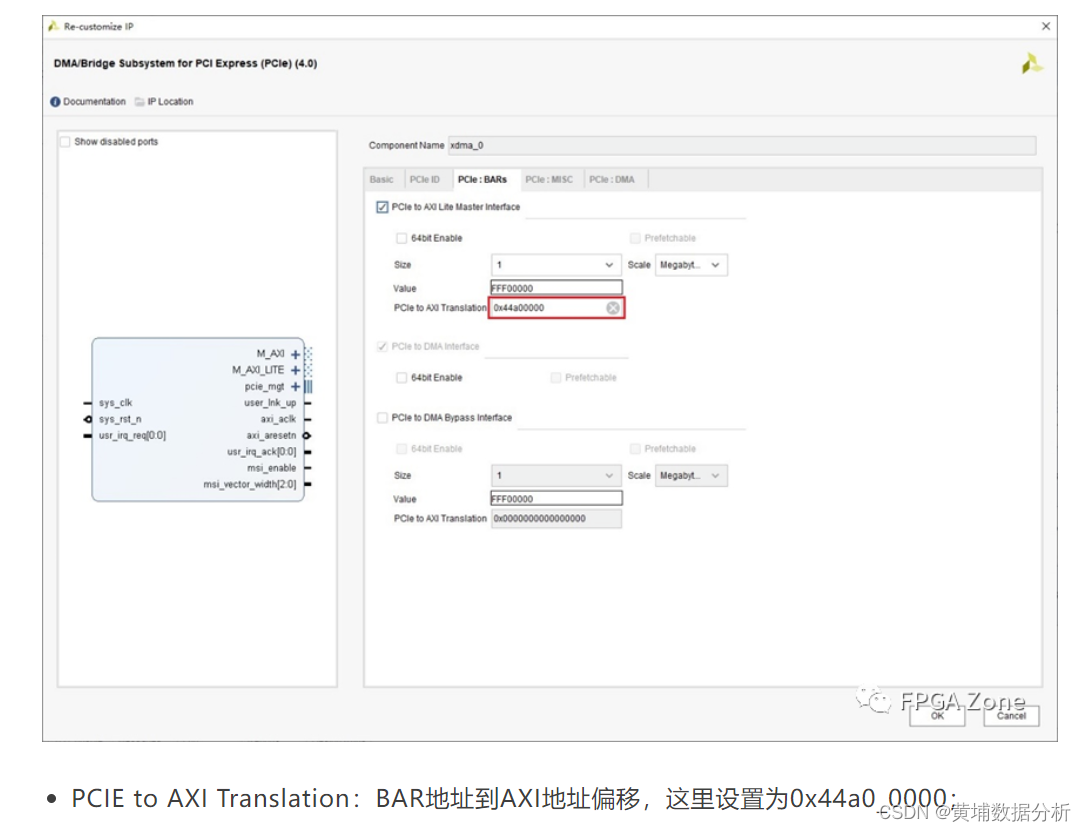

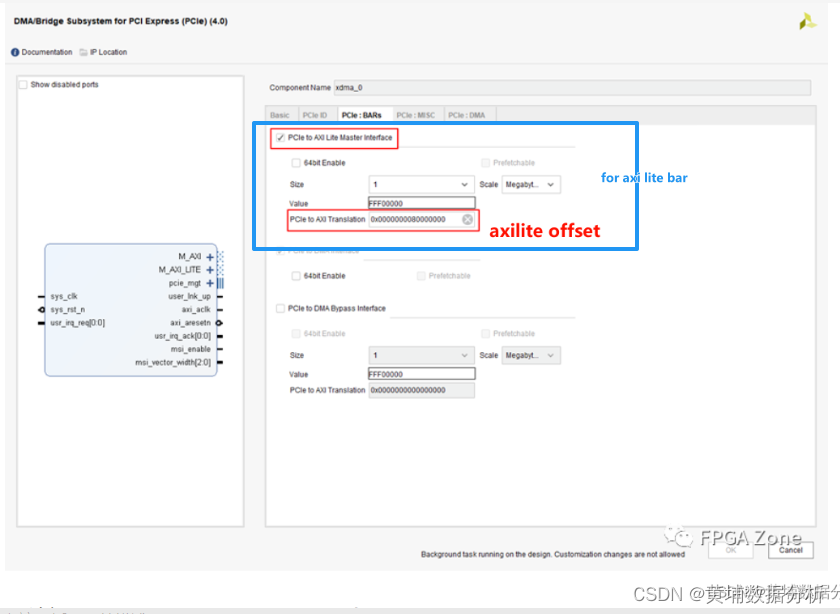

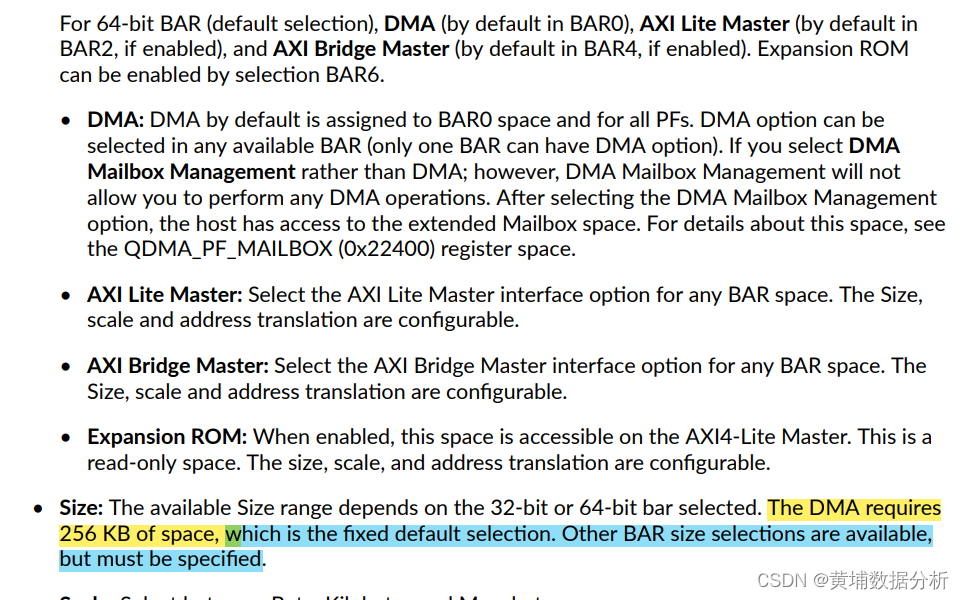

(1)、BAR为32bit,不使能64bit,prefetchable表示预读取,不使能。

(2)、映射空间选择1M,大小随意。

(3)、PCIe to AXI Translation:主机侧BAR地址与用户逻辑侧地址不同,通过设置转换地址实现BAR地址到AXI地址的转换。比如主机一侧BAR地址为0,则主机访问BAR地址0转换到AXI-Lite总线就是0x8000_0000.

PCIe to DMA Interface:数据传输宽度64bit,DMA控制器一般只支持数据8字节对齐的情况。

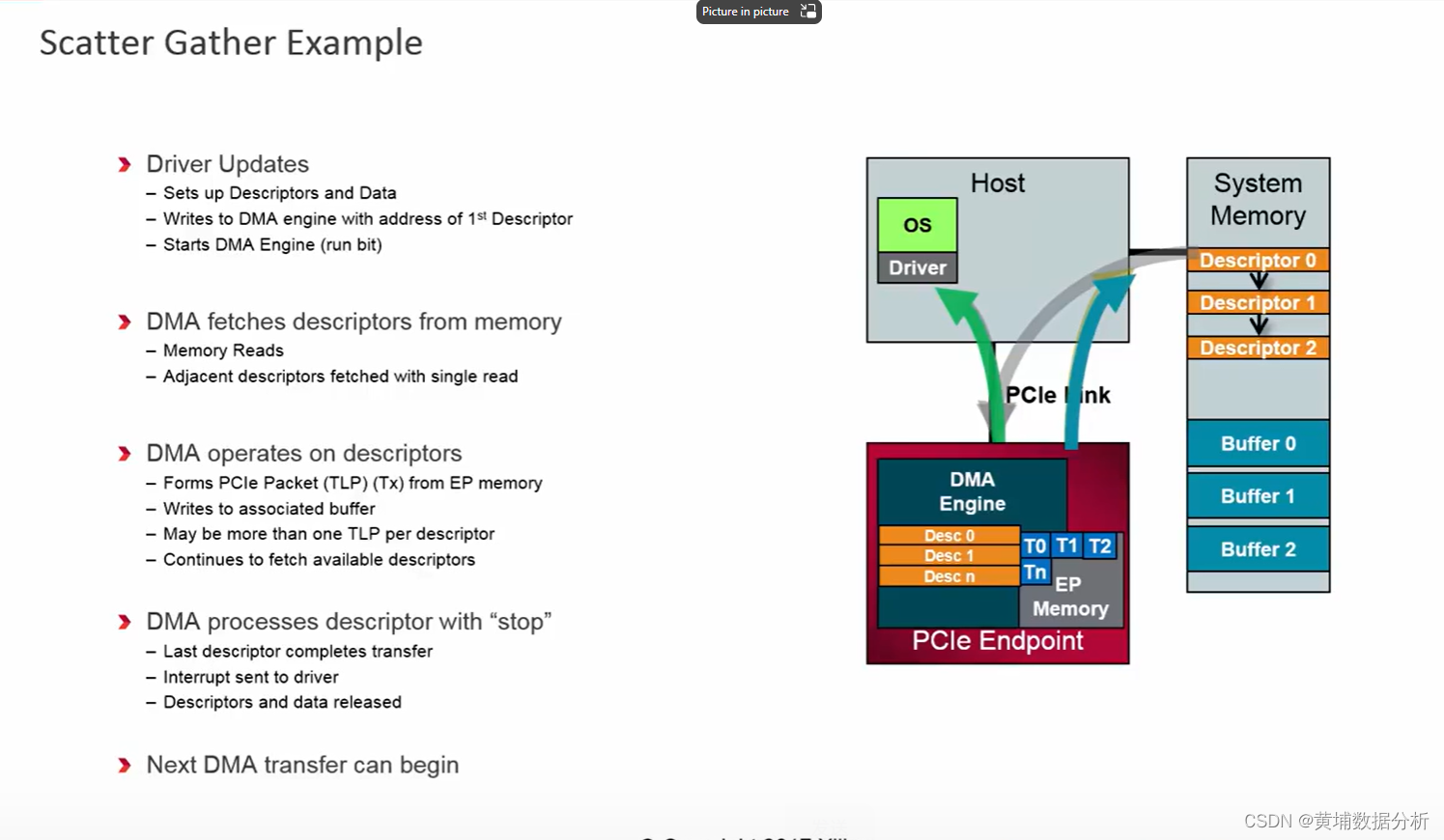

当数据从上位机通过PCIe接口发送到端点设备,XDMA内部自行解包对将数据与指令进行分析,得到读写操作的指令地址,并对DDR进行读写操作。操作的结果通过AXI接口返回XDMA,XDMA对数据进行组包,之后通过物理层发出,实现数据的DMA控制。

DMA的bar不需要映射ddr大小的空间

文章来源:https://blog.csdn.net/weixin_39060517/article/details/135237977

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!