数电笔记之寄存器

2023-12-14 04:34:56

数电

1 数字电路基础

1.2 二进制数据表达

1.2.1 二进制简介

1.2.2 用二进制表达文字

常用的中文字符集:GBK,UTF8

1.2.3 用二进制表达图片

图片像素化,像素数字化

1.2.4 用二进制表达声音

1.2.5 用二进制表达视频

1.3 数字电路

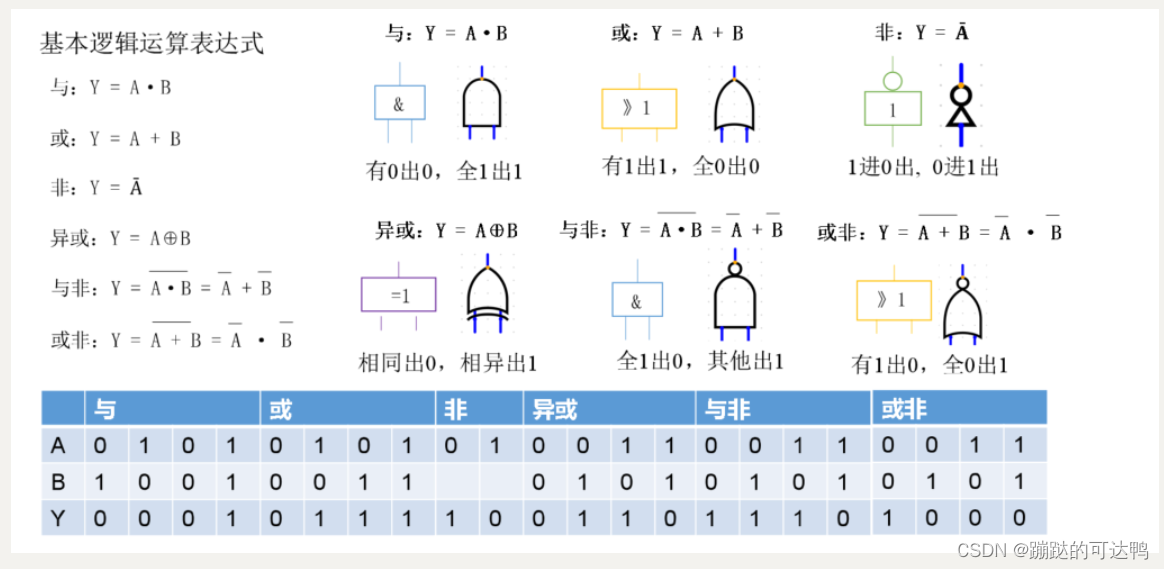

1.3.2 基础逻辑门电路

非门

与门

或门

异或门

与非门

或非门

异或非门

1.3.4 运算器

半加器

通过表格设计电路

| A | B | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

从表格可知S与A,B的关系是异或,C与A,B的关系是与。设计电路如图:

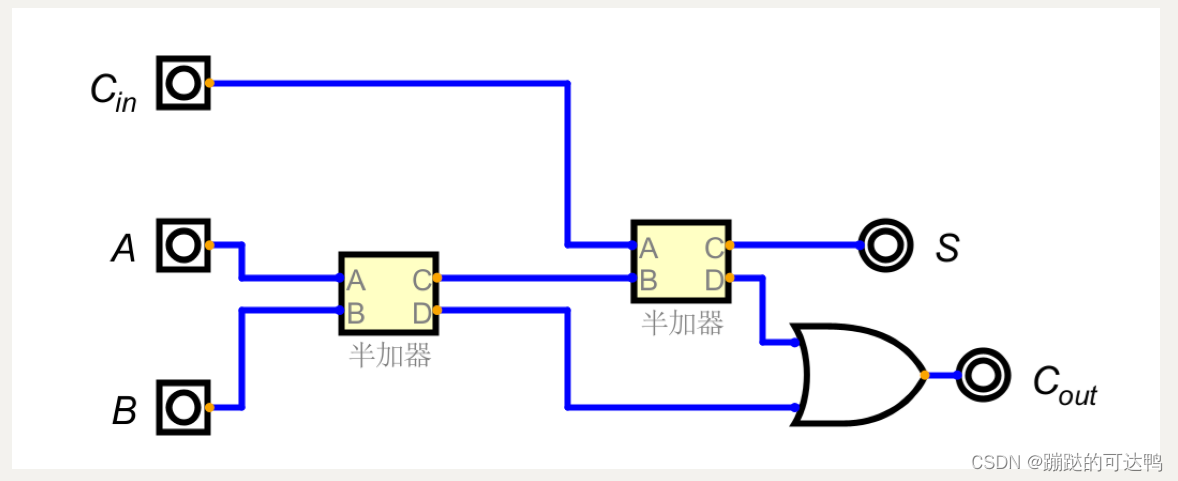

加法器

半加器只能处理两个数的运算,所以时机运算并不可用,加一位低位进位Cin,做成加法器。

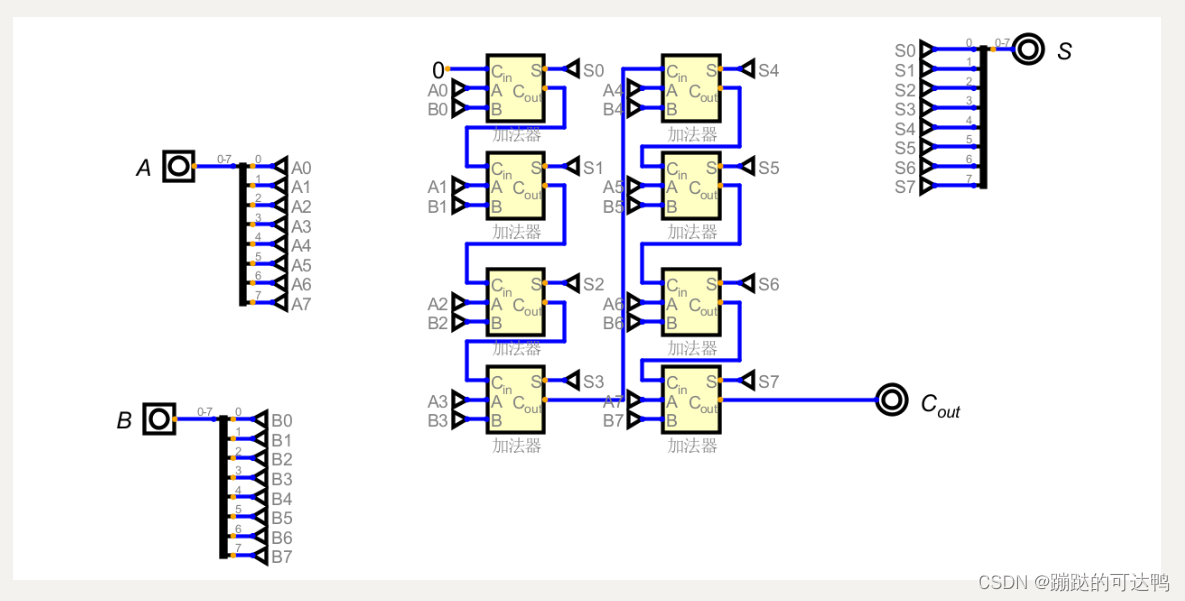

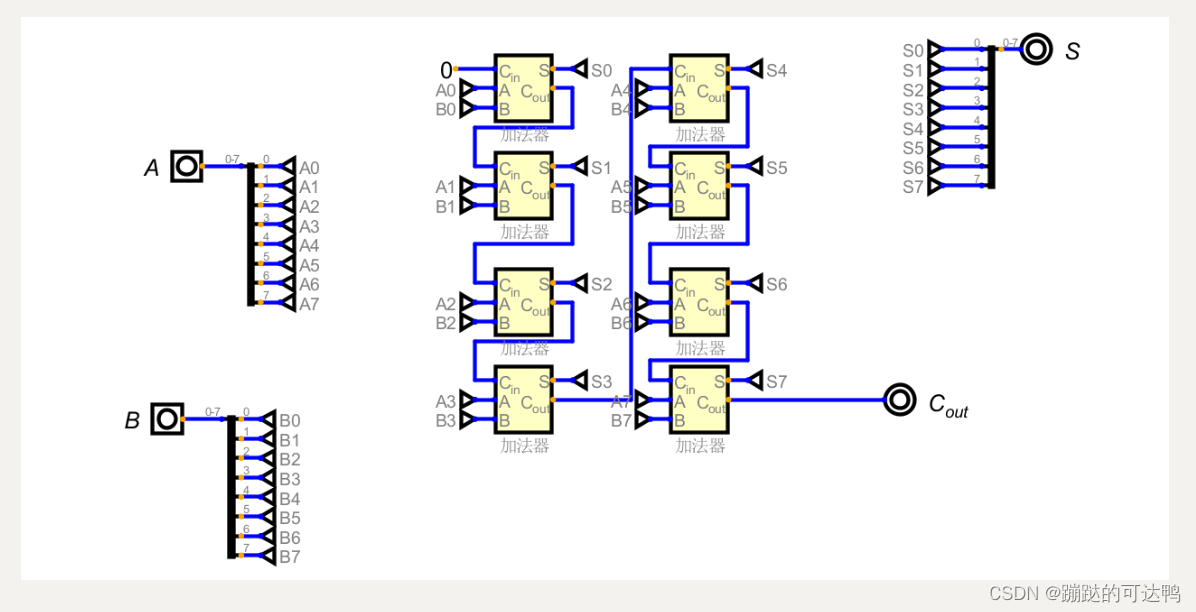

多位加法器

4位加法器就是4个加法器串联在一起。

1.3.5 锁存器和触发器

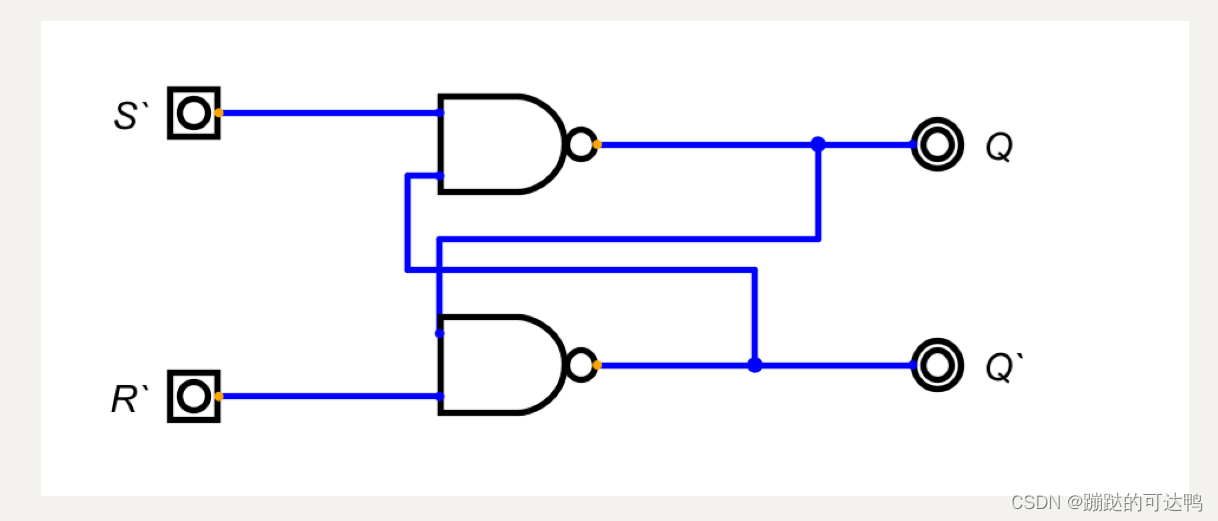

SR锁存器

| S`输入 | R`输入 | Q输出 | Q`输出 |

|---|---|---|---|

| 1 | 1 | 维持不变 | 维持不变 |

| 0 | 1 | 1 | |

| 1 | 0 | 0 | 1 |

| 0 | 0 | 1(无意义) | 1(无意义) |

电路结构图:

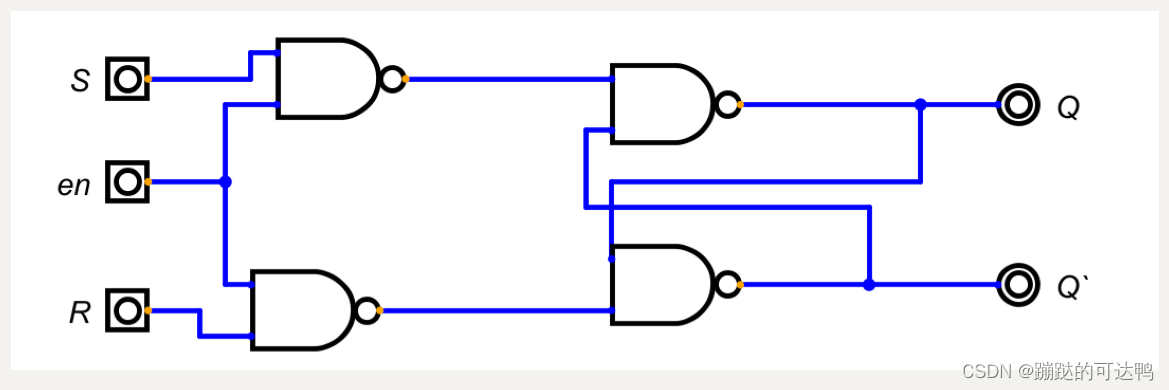

带en输入的D锁存器

SR锁存器的基础上,增加一个触发信号输入端。

工作原理:

en=0,输出保持不变

en=1,正常SR锁存器的功能

S与R同时为1便会出错。此时限制输入

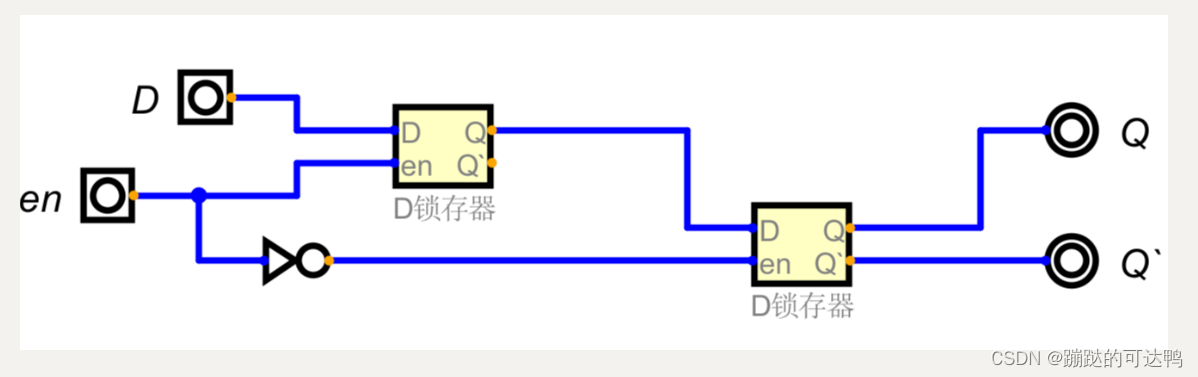

边沿触发的D触发器

为了得到更为稳定的输出Q,不希望en=1时,输出随着输入波动,而是只在1变成0的一瞬间,输入变化,其他时间都保持不变。

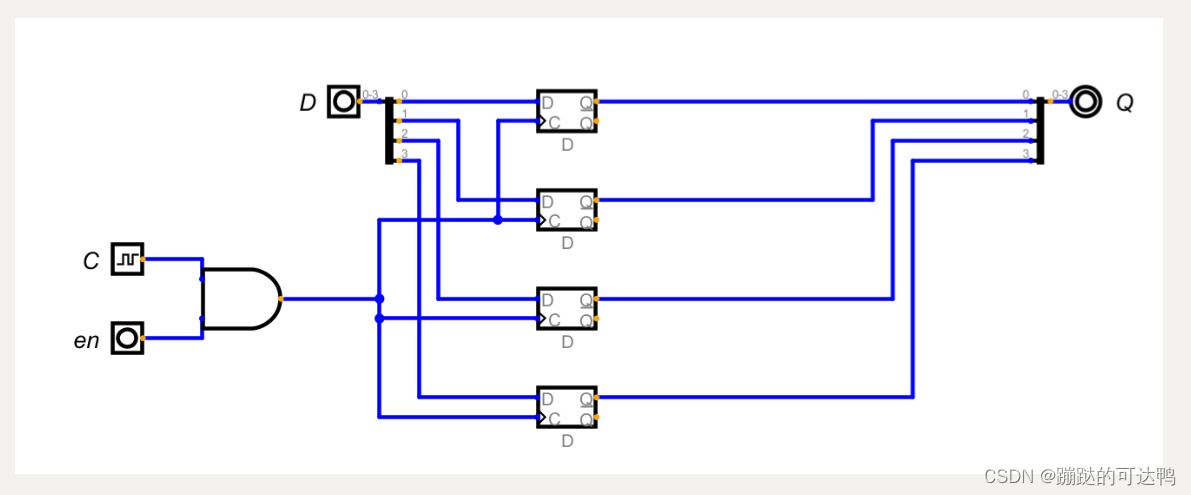

1.3.6 寄存器

多个D触发器并联实现寄存器。

文章来源:https://blog.csdn.net/qq_46115245/article/details/134817193

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!