I.MX RT1170双核学习(2):双核相互激活和启动流程

RT1170这个芯片带有双核:Cortex-M7和Corterx-M4,两个核都可以独立地运行,当然双核也可以同时运行。在上一篇文章中,介绍了一下在RT1170中消息模块MU的使用:双核通信之MU消息单元详解,因为这是双核之间用来通信的核心单元。那有了这个基础之后,这一篇文章就来学习一下在这个芯片中如何启动双核。

1 内存映射

首先我们来分别看一下CM7和CM4的芯片内置内存分配:

(1)CM7

| Start Address | End Address | Size | Description |

|---|---|---|---|

| 2038_0000 | 203F_FFFF | 512KB | OCRAM M7 (FlexRAM) |

| 2036_0000 | 2037_FFFF | 128KB | OCRAM M7 (FlexRAM ECC) |

| 2035_0000 | 2035_FFFF | 64KB | OCRAM2 ECC |

| 2034_0000 | 2034_FFFF | 64KB | OCRAM1 ECC |

| 202C_0000 | 2033_FFFF | 512KB | OCRAM2 |

| 2024_0000 | 202B_FFFF | 512KB | OCRAM1 |

| 2020_0000 | 2023_FFFF | 256KB | OCRAM M4 (LMEM 128KB SRAM_L + 128KB SRAM_U backdoor) |

| 2000_0000 | 2007_FFFF | 512KB | DTCM (FlexRAM) |

| 0000_0000 | 0007_FFFF | 512KB | ITCM (FlexRAM) |

上面0x20200000~0x2023FFFF的OCRAM M4是CM4 TCM的重映射地址,CM7可以通过这个别名区域访问CM4 TCM。

- 当CM4关闭电源时,CM7不能访问这块内存,否则结果是不可预测的。

- CM7通过重映射地址访问这块内存时,速度不及CM4中直接访问这块内存

(2)CM4

| Start address | End address | Size | Description |

|---|---|---|---|

| 2038_0000 | 203F_FFFF | 512KB | OCRAM M7 (FlexRAM) |

| 2036_0000 | 2037_FFFF | 128KB | OCRAM M7 (FlexRAM ECC) |

| 2035_0000 | 2035_FFFF | 64KB | OCRAM2 ECC |

| 2034_0000 | 2034_FFFF | 64KB | OCRAM1 ECC |

| 202C_0000 | 2033_FFFF | 512KB | OCRAM2 |

| 2024_0000 | 202B_FFFF | 512KB | OCRAM1 |

| 2000_0000 | 2001_FFFF | 128KB | System TCM (LMEM RAM_U) |

| 1FFE_0000 | 1FFF_FFFF | 128KB | Code TCM (LMEM RAM_L) |

对于这里的OCRAM M7 (FlexRAM)和OCRAM M7 (FlexRAM ECC),虽然这里写的是M7的内存,但是经过我的测试,M4是可以访问和修改这块内存的。

(3)共享内存区域

这里M7和CM4可以共同访问一些内存:

| RAM | Access address for CM7 | Access address for CM4 | Size |

|---|---|---|---|

| OCRAM M4 | 0x2020_0000 | 0x1FFE_0000 | 128KB |

| OCRAM M4 | 0x2022_0000 | 0x2000_0000 | 128 KB |

| OCRAM M7 | 0x2038_0000 | Same as CM7 | 128KB |

| OCRAM M7 ECC | 0x2036_0000 | Same as CM7 | 128KB |

| OCRAM1 | 0x2024_0000 | Same as CM7 | 512 KB |

| OCRAM2 | 0x202C_0000 | Same as CM7 | 512 KB |

| OCRAM1_ECC | 0x2034_0000 | Same as CM7 | 64 KB |

| OCRAM2_ECC | 0x2035_0000 | Same as CM7 | 64 KB |

- 当然FlexSPI1和FlexSPI2接的Flash、SEMC接的SDRAM所映射的内存在双核间也是共享的。

2 双核启动

对于RT1170的双核来说,它们有一个主从关系(默认是CM7为主核,CM4为从核)。上电后将启动主核,然后由主核在代码中激活并启动从核。

2.1 CM7作为主核

默认情况下,CM7为主核。在CM7上电后需要激活CM4核。当然我们还需要准备好CM4核的代码,这就有两种情况:

1、CM4代码在NOR上XIP执行:需要提前将CM4的程序放在NOR的指定内存位置即可(编译的时候程序也要链接到这个位置)。

2、CM4代码在内置SRAM中执行:

此时CM7中的程序需要将CM4的程序拷贝到CM4的ITCM中。

- CM4的程序可以保存在SD卡、EMMC、U盘等存储介质中

- 这里CM7就可以通过CM4 TCM的重映射地址

0x20200000进行拷贝

接下来就是启动CM4核,有两个步骤:

(1)设置CM4的向量表地址

RT芯片提供了寄存器来(IOMUXC_LPSR_GPR的GPR0和GPR1)设置CM4程序的vector table的地址,正确地设置才能成功激活从核。

我们需要填充CM4_INIT_VTOR_HIGH和CM4_INIT_VTOR_LOW为CM4的向量表地址。

(2)激活M4核

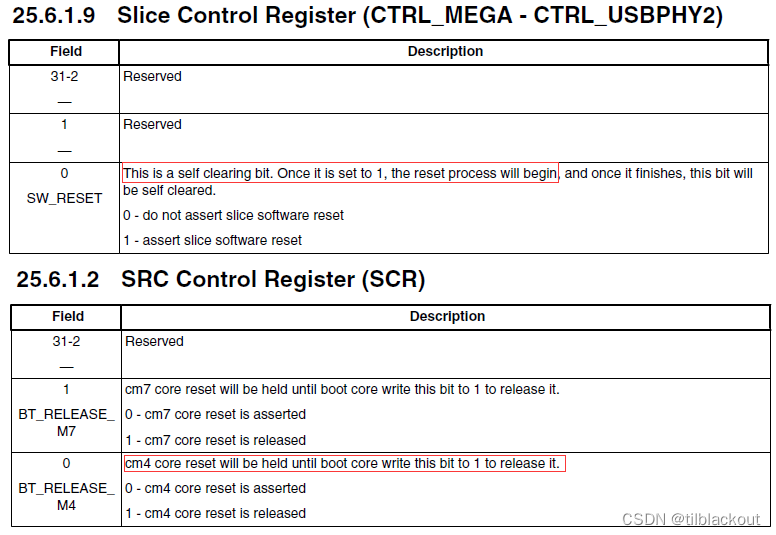

需要置以下两个寄存器的位:

(1)Slice Control Register中的偏移在284h的CTRL_M4CORE寄存器

置bit0为1,可以给CM4进行软件复位

(2)SRC Control Register

CM4会一直保持在复位状态,我们需要置这个寄存器的bit0为1来解除CM4的复位状态。

现在CM4核就成功启动了。

2.2 CM4作为主核

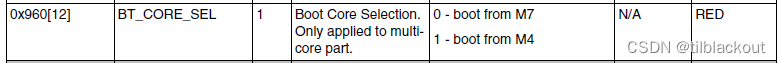

在RT1170中,默认CM7为主核,如果需要设置CM4为主核的话,需要烧写0x960处熔丝的第12位为1。

同样地,如果CM7的程序需要在RAM中运行,需要CM4的程序来拷贝CM7的程序到RAM中。

接下来也是设置向量表和启动CM7核:

1、向量表:IOMUXC_LPSR_GPR的GPR26寄存器

2、复位CM7核:Slice Control Register中的偏移在2A4h的CTRL_M7CORE寄存器

2、启动CM7核:SRC Control Register的bit1

这里就不详细介绍了,因为这种方法需要烧写熔丝,也很少有人用到。

3 总结

本文介绍了CM7和CM4相互激活的基本设置,在SDK中,有一个MCMGR(Multicore Manager)实现了多核之间的管理操作,除了实现本文所述的设置外,还有双核之间状态的同步。下一节就来剖析MCMGR中的源码实现。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!