关于差分晶振的LVDS、LVPECL、HCSL、CML模式介绍及其相互转换

差分晶振一般用在高速数据传输场合,常见的有LVDS、LVPECL、HCSL、CML等多种模式。这些差分技术都有差分信号抗干扰性及抑制EMI的优点,但在性能、功耗和应用场景上有很大的区别。下图列举了最常用的几种差分信号技术和它们的主要参数。

LVDS信号的摆幅低,为±350mv, 对应功耗很低。但速率可达3.125Gbps。总的来说电路简单、功耗和噪声低等优点,使LVDS成为几十Mbps及至3Gbps应用的首选。

LVPECL信号的摆幅为±800mv或更高,所以其功耗是大于LVDS信号的。但同样也具有更高的驱动能力,可应用于10Gbps的高速数据传输。

CML(Current Mode Logic)信号主要靠电流驱动,它的输入和输出是匹配好的,从而减少了外围器件,使用时直接连接就可以,是高速数据接口形式中最简单的一种。如XAUI、10G XFI接口均采用CML电平。

LVDS、LVPECL、CML比较

三种电平都是高速设计中常用的电平,但各有特色:

驱动模式:都属于电流驱动

外部端接:

CML最简单,一般无需外部端接,直接连接即可;

LVDS次之,需在接收端增加一个100Ω的终结电阻(内置的不需要);

LVPECL最复杂,其输出端需偏置到VCC-2V,输入端需偏置到VCC-1.3V。

功耗:LVDS差分对摆幅最小,因此功耗也最小,在相同工作速率下,功耗不到LVPECL的三分之一;CML和LVPECL差分对摆幅相对较大,且内部三极管工作于非饱和状态,功耗较大,基于结构上的差异,CML的功耗低于LVPECL。

工作速率:由于CML和LVPECL内部三极管工作于非饱和状态,逻辑翻转速率高,能支持更高的数据速率;同时,由于LVDS差分对的输入摆幅较小(LVDS为100mV,LVPECL为310mV,CML为400mV;输出摆幅:LVDS为350mV,LVPECL为800mV,CML为800mV),噪声容限较小,不利于高速传输。

耦合方式:都支持直流耦合和交流耦合

下面讲一讲各信号模式之间的转换:

LVPECL到CML的转换

如图1所示,在LVPECL驱动器输出端向GND处放置一个150Ω的电阻对于开路发射极提供直流偏置以及到GND的直流电流路径至关重要。为了将800mV LVPECL摆幅衰减到400mV的CML摆幅,需在150Ω电阻之后放置一个50Ω的衰减电阻(RA),以衰减LVPECL摆幅电平的一半。另外,必须确认CML接收器输入内部的自偏置。如果CML输入端的自偏置不存在,则必须在PCB上放置50Ω的端接电阻到VCC,用于CML偏置和传输线端接。?

?图1.LVPECL到CML的转换

LVPECL到LVDS的转换

在LVPECL驱动器输出端向GND放置一个150Ω电阻,对于开路发射极提供直流偏置以及到GND的直流电流路径至关重要(图2)。为了将800mV LVPECL摆幅衰减到325 mV LVDS摆幅,必须在150Ω电阻器之后放置一个70Ω的衰减电阻。应在LVDS接收器前面放置一个10nF交流耦合电容,以阻止来自LVPECL驱动器的直流电平。LVDS输入需要重新偏置,可以通过向GND放置8.7KΩ电阻连接到3.3V和5KΩ电阻到GND来实现LVDS接收器输入共模的1.2V直流电平。如果LVDS接收器差分输入引脚上已经存在有100Ω电阻,则不需要外部100Ω电阻。

图2.LVPECL到LVDS的转换

LVPECL到HCSL的转换

如图3所示,在LVPECL驱动器输出端向GND放置一个150Ω电阻对于开路发射极提供直流偏置以及到GND的直流电流路径至关重要。为了将800mV的LVPECL摆幅衰减到700mV的HCSL摆幅时,必须在150Ω电阻之后放置一个衰减电阻(RA =8Ω)。应在HCSL接收器前面放置一个10nF交流耦合电容,以阻止来自LVPECL驱动器的直流电平。放置交流耦合电容后,HCSL输入需要重新偏置,可以通过将470Ω电阻连接3.3V和56Ω电阻到GND上来实现HCSL接收机输入共模的350 mV直流电平。

图3.LVPECL到HCSL的转换

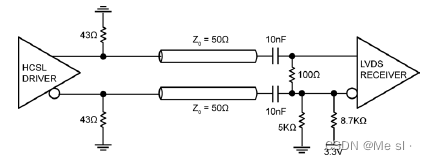

HCSL到LVDS的转换

在图4中,每个HCSL输出引脚在0和14mA之间切换。当一个输出引脚为低电平(0)时,另一个为高电平(驱动14mA)。HCSL驱动器的等效负载电阻为48Ω,与50Ω并联,相当于23.11Ω。LVDS输入的摆幅为14mAx23.11Ω= 323mV。应在LVDS接收器前放置一个10nF交流耦合电容,以阻止来自HCSL驱动器的直流电平。放置交流耦合电容后,LVDS输入需要重新偏置,可以通过将一个8.7KΩ电阻连接到3.3V和5KΩ电阻连接到GND来实现LVDS接收器输入共模的1.2V 直流电平。如果LVDS接收器差分输入引脚上已经存在有100Ω电阻,则不需要外部100Ω电阻。

?图4.HCSL到LVDS的转换

HCSL到CML的转换

在图5中,每个HCSL输出引脚在0和14mA之间切换, 当一个输出引脚为低电平(0)时,另一个为高电平(驱动14mA)。HCSL驱动器的等效负载电阻为68Ω,与50Ω电阻并联,相当于28.81Ω。CML输入的摆幅为14mAx28.81Ω=403mV。应在CML接收器前面放置一个10nF交流耦合电容,以阻止来自HCSL驱动器的直流电平。另外,必须确认CML接收器输入内部的自偏置。如果没有CML输入端的自偏置,则必须在CML偏置和传输线端接的PCB上放置一个50Ω的端接电阻到VCC。

?图5HCSL到CML的转换

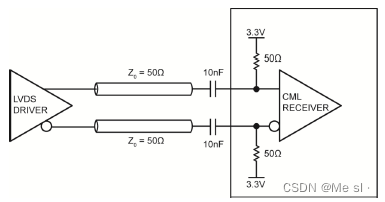

LVDS到CML的转换

LVDS输出通过100Ω电阻终端驱动±3.5mA电流,在CML接收器前面产生350mV摆幅电平(图6)。因为CML的标准摆幅是400mV,所以CML接收器能够接收350mV摆幅电平。此外,还必须确认CML接收器输入内部的自偏置。如果CML输入端的自偏置不存在,则必须在PCB上放置一个50Ω的电阻到VCC,用于CML偏置和传输线端接。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!