基本的逻辑门

前言

本篇文章介绍基本的逻辑门,然后给出C语言描述

逻辑门是在集成电路上的基本组件。简单的逻辑门可由晶体管组成。这些晶体管的组合可以使代表两种信号的高低电平在通过它们之后产生高电平或者低电平的信号。高、低电平可以分别代表逻辑上的“真”与“假”或二进制当中的1和0,从而实现逻辑运算。

本文介绍的内容列表如下:

- CMOS晶体管

- 非门

- 与门

- 或门

- 与非门

- 或非门

- 异或门

CMOS晶体管

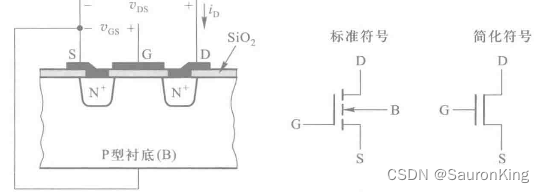

N型增强型晶体管

N型增强型晶体管是由P型半导体衬底,制作两个高摻杂浓度的N型区, 形成CMOS管的源极S(Source)和漏极D(Drain),然后在源极S和漏极D之间添加一个栅极G,通常用多晶硅制作,栅极和衬底之间添加一层二氧化硅绝缘层,绝缘层一般非常薄,在0.1微米之内

- 如果栅极G不导通,由于P型衬底和N型区域之间有PN结,整个电路不导通

- 如果栅极G导通,并且连接到正极,这时栅极G与P型衬底之间形成了电场,P型衬底连接的是源极S,也就是负极,栅极为正极,这样,P型衬底中的电子会向栅极靠近,在两个N型半导体之间形成通路,电路导通。

总结:通过栅极的导通能够控制源极S和漏极D的导通,这样,CMOS管就可以作为开关使用了。

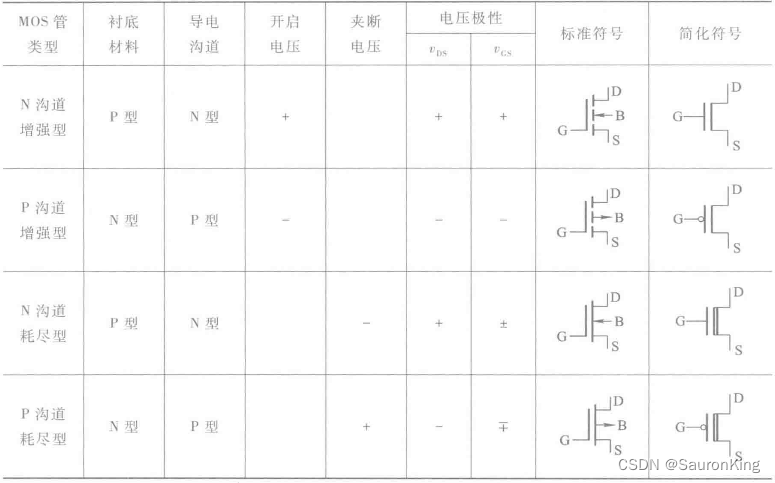

P型增强型晶体管

P型增强型晶体管与N型增强型晶体管结构正好相反,是由N型半导体作为衬底,导电沟道为P型半导体,这种晶体管的特点是

- 栅极接入的是负极

- 为了形成电场,N型衬底为正极,也就是源极S为正极

N型耗尽型晶体管

这种类型的晶体管结构与N型增强型晶体管一样,不过在栅极下的二氧化硅绝缘层添加了正离子。也就是自带电场,这样,栅极不导通或者连接正极的时候晶体管都是导通的,栅极连接负极并且达到一定值以后,晶体管断开。这个值叫做夹断电压

P型耗尽型晶体管

结构与P型增强型晶体管一致,特点与N型耗尽型晶体管相似,栅极不导通或者连接负极的时候晶体管都是导通的,栅极连接正极并且达到一定值以后,晶体管断开。

下图是四种晶体管的比较

其中,

v

D

S

v_{DS}

vDS?为漏极到原极的电压

v

G

S

v_{GS}

vGS?为栅极到原极的电压

D:漏极

S:原极

G:栅极

不同类型的晶体管的自由组合就可以形成各种门。

非门

非门又叫反相器,是指输入的信号状态与输出的信号状态相反

非门用下面的符号表示

非门可以通过一个N型增强型晶体管和一个P型增强型晶体管连接实现

非门的输入输出逻辑关系如下:

输入

输出

0

1

1

0

\begin{array}{|c|c|} \hline 输入&输出\\ \hline 0&1\\ \hline 1&0\\ \hline \end{array}

输入01?输出10??

与门

与门是指当输入的两个信号都为高电平时输出的信号才为高电平

与门用下面的符号表示

与门可以用两个CMPOS晶体管来实现

与门的输入输出逻辑关系如下:

输入

A

输入

B

输出

0

0

0

0

1

0

1

0

0

1

1

1

\begin{array}{|c|c|c|} \hline 输入A&输入B&输出\\ \hline 0&0&0\\ \hline 0&1&0\\ \hline 1&0&0\\ \hline 1&1&1\\ \hline \end{array}

输入A0011?输入B0101?输出0001??

或门

或门是指当输入的两个信号任意一个为高电平时输出的信号为高电平

或门用下面的符号表示

或门可以用两个CMOS晶体管来实现

或门的输入输出逻辑关系如下:

输入

A

输入

B

输出

0

0

0

0

1

1

1

0

1

1

1

1

\begin{array}{|c|c|c|} \hline 输入A&输入B&输出\\ \hline 0&0&0\\ \hline 0&1&1\\ \hline 1&0&1\\ \hline 1&1&1\\ \hline \end{array}

输入A0011?输入B0101?输出0111??

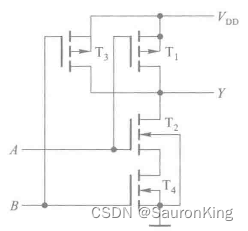

与非门

与非门用下面的符号表示

与非门可以使用两个并联的P沟道增强型MOS管

T

1

T_1

T1?、

T

3

T_3

T3?和两个串联的N沟道增强型MOS管

T

2

T_2

T2?、

T

4

T_4

T4?组成,总共需要4个晶体管

与非门的输入输出逻辑关系如下:

输入

A

输入

B

输出

0

0

1

0

1

1

1

0

1

1

1

0

\begin{array}{|c|c|c|} \hline 输入A&输入B&输出\\ \hline 0&0&1\\ \hline 0&1&1\\ \hline 1&0&1\\ \hline 1&1&0\\ \hline \end{array}

输入A0011?输入B0101?输出1110??

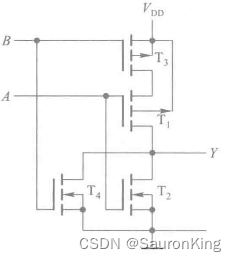

或非门

或非门用下面的符号表示

或非门可以使用两个串联的P沟道增强型MOS管

T

1

T_1

T1?、

T

3

T_3

T3?和两个并联的N沟道增强型MOS管

T

2

T_2

T2?、

T

4

T_4

T4?组成,总共需要4个晶体管

或非门的输入输出逻辑关系如下:

输入

A

输入

B

输出

0

0

1

0

1

0

1

0

0

1

1

0

\begin{array}{|c|c|c|} \hline 输入A&输入B&输出\\ \hline 0&0&1\\ \hline 0&1&0\\ \hline 1&0&0\\ \hline 1&1&0\\ \hline \end{array}

输入A0011?输入B0101?输出1000??

异或门

异或门用下面的符号表示

异或门可以使用一个或门,一个与非门进行与门操作,共需要8个晶体管

或非门的输入输出逻辑关系如下:

输入

A

输入

B

输出

0

0

0

0

1

1

1

0

1

1

1

0

\begin{array}{|c|c|c|} \hline 输入A&输入B&输出\\ \hline 0&0&0\\ \hline 0&1&1\\ \hline 1&0&1\\ \hline 1&1&0\\ \hline \end{array}

输入A0011?输入B0101?输出0110??

下面,给出基本逻辑门的C语言实现

// 虽然参数采用的是int类型,但是在模拟运行时,只能是0或者1

/**

* 与门

*/

int and_gate(int in_1,int in_2)

{

return in_1 & in_2;

}

/**

* 或门

*/

int or_gate(int in_1,int in_2)

{

return in_1 | in_2;

}

/**

* 非门

*/

int not_gate(int in_1)

{

return !in_1;

}

/**void

* 或非门

*/

int not_or_gate(int in_1,int in_2)

{

return !(in_1 | in_2);

}

/**

* 与非门

*/

int not_and_gate(int in_1,int in_2)

{

return !(in_1 & in_2);

}

/**

* 异或门

*/

int xor_gate(int in_1,int in_2)

{

int or_val = or_gate(in_1, in_2);

int not_and_val = not_and_gate(in_1, in_2);

return or_val & not_and_val;

}

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!