AWR2243级联(TI文档)

摘要

????????本应用报告描述了TI的级联毫米波雷达系统。该解决方案基于TI的AWR2243雷达芯片。使用20 GHz的本振输入和输出路径,这些芯片中的几个级联在一起并同步工作。每个AWR2243芯片最多支持4个接收天线和3个发射天线。级联多个这样的芯片允许雷达系统使用更多的接收和发射天线,从而与基于单个AWR2243雷达芯片的系统相比,提高了目标探测和分辨率。本应用报告说明了2个和4个AWR2243芯片的级联。这种级联雷达解决方案旨在支持自适应巡航控制、碰撞警告、紧急制动以及半自动和全自动驾驶等汽车应用。本文档中描述的系统已经在毫米波级联成像雷达射频评估模块中进行了评估。

1 级联AWR2243系统

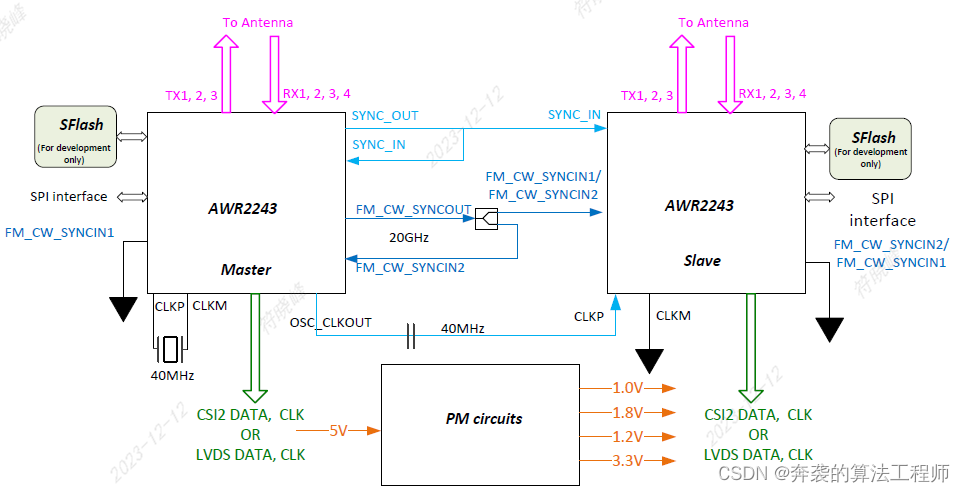

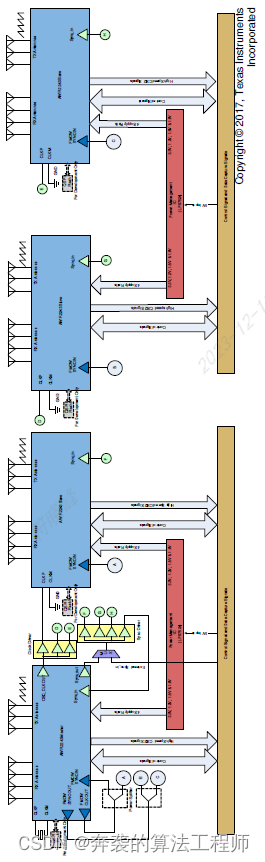

????????多个AWR2243芯片可以级联在PCB上,以提高目标检测和分辨率。本节以两芯片级联和四芯片级联系统为例进行说明。重点关注连接AWR2243芯片之间需要共享的各种信号。在级联系统中的多个AWR2243芯片中,一个被称为主芯片,其他被称为从芯片。为了使整个级联系统作为一个单一的雷达系统运行,主芯片被指定产生一个公共的本振(LO)信号(19 GHz至20.25 GHz),在整个级联系统中的所有发射器和接收器之间共享。主芯片还通过生成数字同步信号并与从芯片共享此同步信号来控制所有芯片的雷达chirp/帧时序。主芯片还使用一个40 MHz的晶体,并产生一个40 MHz的振荡器时钟(OSC_CLKOUT),并与从芯片(作为CLKP)共享,从而消除了对从芯片上额外晶体的需要,并确保整个系统从单个时钟源运行。

?????? 主芯片能够通过两个不同的延迟匹配放大器在两个不同的输出引脚上提供共享本振。这可以在一个四芯片级联系统中使用,仅使用无源分路器向主芯片和三个从芯片提供本振信号。这消除了对PCB上额外的、昂贵的有源元件的需求。主芯片使用OSC_CLKOUT引脚与系统中的从芯片共享40 MHz时钟源。在双设备系统的情况下,这可以通过设备之间的无源走线来完成。在超过2个设备的情况下,建议使用时钟扇出缓冲器来管理负载和信号完整性问题。类似地,DIG_SYNC通过板上与延迟匹配的缓冲区从主芯片传送到从芯片,然后传回自身。

????????除了这些连接,在下面的图表中说明,并在后面的章节中进一步阐述,级联系统还具有电源管理芯片 (PMIC)(每个PMIC最多可以处理两个AWR2243芯片),可选的QSPI闪存(仅用于初始软件开发目的)和毫米波天线连接到每个AWR2243芯片。

图1 一个两片级联系统

图2 一个四片级联系统

2 AWR2243芯片的同步

????????在级联系统中,有一个主芯片和一个或多个从芯片。这些级联设备通过以下接口进行同步:

?????????20 GHz (FMCW) 射频本振同步

?????????数字帧时序同步

?????????40 MHz(系统)参考时钟同步

????????20 GHz (FMCW) 射频本振由主芯片产生,并分配给从芯片和主芯片。相关信号/引脚在本文档中称为FM_CW_SYNCx/CLKx或20GHz本振。

????????在基于软件消息的帧触发的情况下,帧时序同步由主芯片控制,或者在基于硬件的帧触发的情况下,由主芯片处理器控制。相关信号/引脚在本文中称为SYNC_IN/OUT或DIG_SYNC_IN/OUT。

????????40MHz系统时钟可以由主芯片或外部供应产生。相关引脚为OSC_CLKOUT、CLKP和CLKM。

????????关于同步的详细描述将在以下章节中给出。

2.1 20GHz(FMCW)射频本振同步

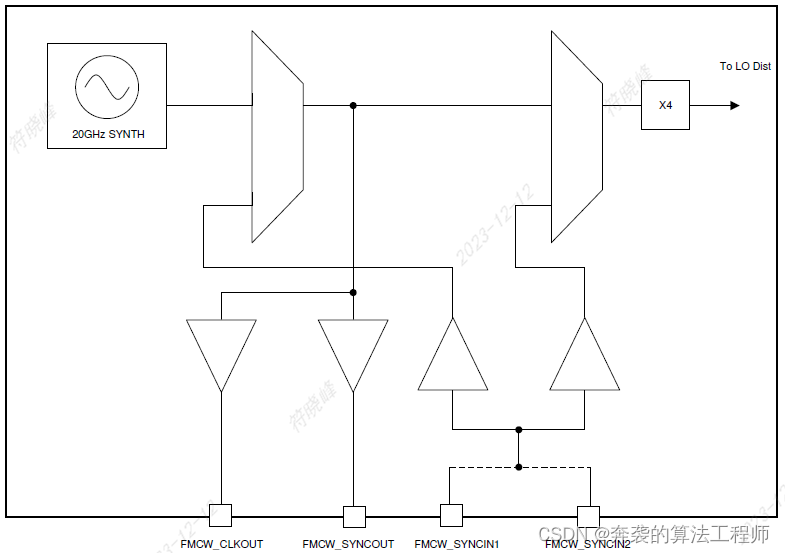

????????图3显示了AWR2243芯片的20GHz部分。

图3 芯片中的20 GHz多路复用选项

????????所有AWR芯片都应该同步其射频本振频率。AWR2243合成器产生的本振介于19 GHz和20.25 GHz之间,具体取决于编程的chirp射频输出频率。该本振频率在每个芯片中乘以4,生成76-81 GHz频段的射频。20 GHz的本振携带chirp调制。

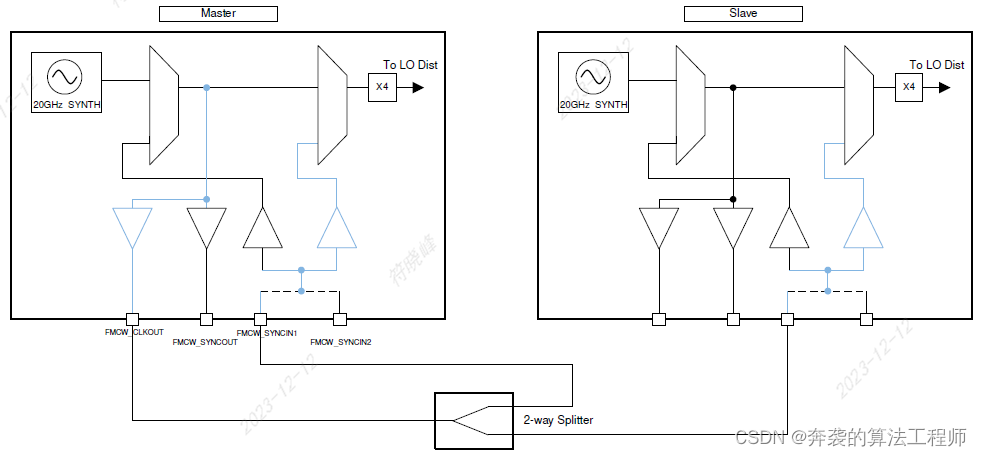

????????AWR2243支持星型本振分配拓扑。

????????在这种星形分配拓扑中,主本振在PCB上划分,并以星形方式馈送到从芯片和主芯片。在PCB上路由本振分配网络,以便为所有本振走线产生相同的延迟。这将导致所有从芯片和主芯片以相同的延迟接收本振。主芯片从本振分配器接收到它自己的本振,这样它也可以与从芯片延迟匹配。

图4 2片星型拓扑中本振分配的例子

2.2 数字帧同步

????????在级联的系统中,有必要在所有芯片之间同步RX ADC采样窗口。帧同步,在本节中描述,确保来自所有芯片的ADC样本的一致性和横跨组成芯片的chirp时序信号的校准。

????????注意,本节中的“帧(触发)”指的是帧(如AWR_FRAME_CONF_SB中定义的)和触发(如AWR_ADVANCED_FRAME_CONF_SB中定义的)。

2.2.1 在AWR2243中的帧(触发)和chirp时序

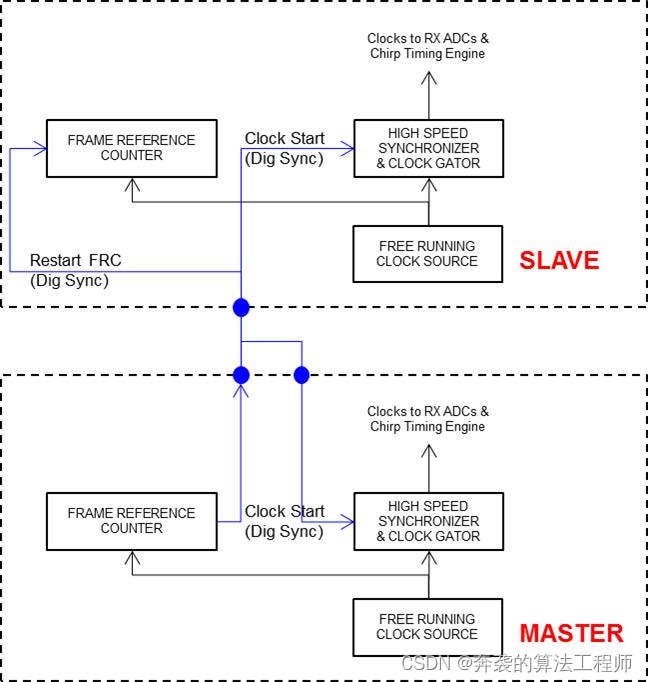

????????AWR2243设备包括一个帧参考计数器(FRC),它保持帧(触发)之间的时序。它生成一个数字同步(在图5中标记为“Dig Sync”)信号,也称为帧(触发)启动信号,该信号基于软件消息部分中描述的API消息给出的帧(突发)时序参数。处理器固件也依赖于FRC来安排校准、监控和设置功能触发。

????????AWR2243器件还包括一个高速同步器和时钟发生器,它启动高速时钟到RX ADC和chirp时序引擎与Dig Sync。Chirp时序引擎在每帧(触发)内的多个chirp期间和跨多个chirp保持时序,并考虑合成器斜坡(ramp)和RX ADC有效数据拾取的生成,等等。在每一帧(触发)结束时,时钟由处理器停止。这在单芯片使用示例的时序和框图中进行了说明。

图5 AWR2243中的帧(触发)时序和时钟生成

2.2.2 级联系统中的帧(触发)和chirp时序

????????在级联系统中,各组成芯片的FRC和chirp时序引擎是同步工作的。主芯片FRC产生Dig Sync信号。Dig Sync从主芯片路由出去,给到从芯片,再回到主芯片,以匹配主芯片和从芯片之间的偏离。如图7所示(2个芯片级联示例),Dig Sync被同步并用于将时钟解耦到主和从芯片中的所有RX ADC和chirp时序引擎,从而确保芯片之间的时序校准。它还确保主芯片和从芯片的处理器固件运行(在5到10毫秒的不确定性内)。Dig Sync信号的PCB布线应该延迟匹配,以便在主芯片和从芯片之间实现最佳校准。

图6 在2片级联示例的帧(触发)时序生成

2.2.3 数字同步时序的芯片间不平衡

????????理想情况下,到达所有芯片中相关电路的DIG_SYNC_IN(如图6中的Dig Sync所示)在延迟上是平衡的,从而实现chirp的完美时序同步。但实际上,在级联系统中,不同的AWR2243器件之间存在延迟不平衡。这种延迟不平衡大部分是由于AWR2243器件之间的制造工艺差异造成的。一些延迟不平衡是由于设备之间的温度差异造成的。此外,对于DIG_SYNC_IN脉冲的每次出现,在每个设备的同步器电路中存在一个时钟不确定性。表1总结了这些不平衡。

表1 DIG_SYNC_IN不平衡总结

| DIG_SYNC_IN Inter-Chip Imbalance Type | Total Inter-Chip Imbalance Magnitude |

| Imbalances due to chip process + voltage differences in a given cascade board | Up to 4 ns approximately |

| Imbalances due to chip temperature differences in a given cascade board (up to 40°C) | Up to 0.6 ns approximately |

| Imbalances due to synchronization uncertainty | Either 0 or 0.55 ns (1) |

????????(1)对于DIG_SYNC_IN脉冲的每次出现,这是可变的。提供的数字是假设ADC在常规模式下工作。在低功耗操作下,由于ADC时钟频率是常规模式的一半,这些数字应该翻倍。

2.3 40MHz(系统)参考时钟同步

????????系统的主参考时钟为40MHz时钟。通常主芯片生成这个时钟并分配给从芯片。另外,外部源可以同时向主芯片和从芯片提供时钟。在这个时钟上没有相位/延迟匹配要求。当40MHz时钟外部馈电时,相位噪声要求非常重要。

3 连接

3.1 20GHz本振引脚连接

????????表2显示了当本振反馈到同一芯片时,主芯片上20 GHz本振同步中使用的推荐引脚组合。

表2 在20GHz本振使用推荐引脚组合

| Combination | Master LO Output | Master LO Input | Ground |

| 1 | FM_CW_SYNCOUT [D1] | FM_CW_SYNCIN2 [D15] | FM_CW_SYNCIN1 [B1] |

| 2 | FM_CW_CLKOUT [B15] | FM_CW_SYNCIN1 [B1] | FM_CW_SYNCIN2 [D15] |

????????20GHz路由的一般指南:

?????????保持本振路由距离尽可能小。

?????????本振输入接口:有2个本振输入接口。它们被标记为FM_CW_SYNCIN1和FM_CW_SYNCIN2。提供这两个端口是为了帮助PCB上的本振分配路由。一次只能使用一个输入端口。未使用的端口必须直接在BGA侧短接接地。

?????????本振输出端口:有2个本振输出端口。可以使用任意一个端口,也可以同时使用两个端口。未使用的本振输出端口应在BGA 板上浮动。

3.2 DIG_SYNC连接

?????? 主芯片使用SYNC_OUT [P11]引脚产生同步信号。SYNC_OUT输入到从芯片SYNC_IN [N10]。当两个以上芯片级联时,建议使用时钟缓冲器分发SYNC_OUT信号。其中一个缓冲器输出反馈到主芯片进行延迟匹配。

3.3 40MHz(系统)参考时钟连接

?????? 在主芯片为其他从芯片提供参考时钟的情况下,使用主芯片的OSC_CLKOUT [A14]引脚。OSC_CLKOUT馈入从芯片的CLKP [E14]引脚。OSC_CLKOUT信号是一个大约1.3 V到地的方波输出。它可以直流解耦或交流耦合到从芯片的CLKP引脚。CLKP的最大输入电平在直流解耦时为1.8 V,在交流耦合时为1.2 Vpp。

????????当两个以上芯片级联时,建议使用时钟扇出缓冲器为从芯片生成时钟。

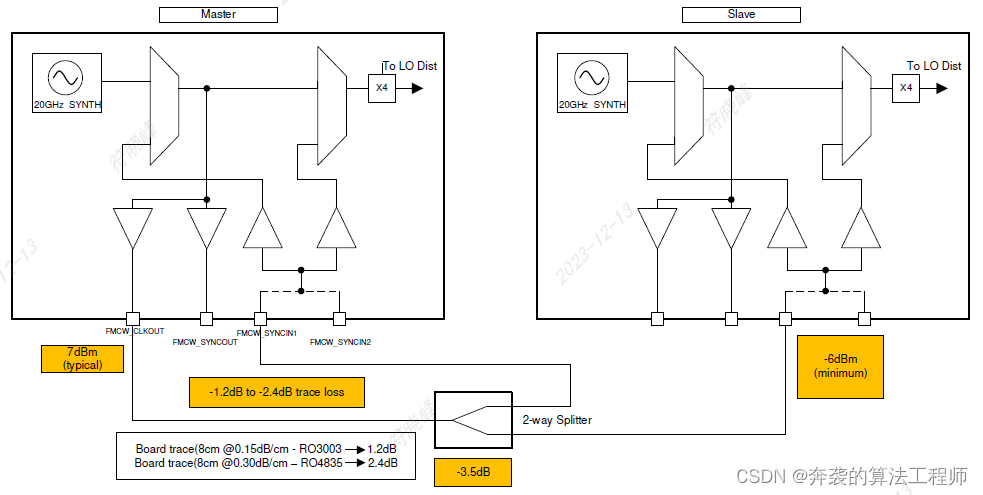

4 20GHz本振同步链路预算

????????下面给出的是20 GHz 本振分配的典型链路预算。假设有两种类型的板损:

?????????罗杰斯RO3003与轧制铜

?????????罗杰斯RO4835 LoPro。

????????假设20 GHz走线的长度为8cm。

????????更多信息,请看《AWR2243 Single-Chip 76- to 81-GHz FMCW Transceiver Data Sheet》,射频指标表,面向所有本振输入和输出指标。

图7 20GHz本振链路预算

5 软件消息

????????级联系统中涉及的AWR2243设备可以通过软件API消息进行控制,这是本节的重点。接口控制文档(ICD)[1]包含AWR2243支持的API消息的详细信息。此外,应用报告[2],TI雷达器件中的编程chirp参数解释了单芯片环境下的典型软件配置。其中提供的信息在级联芯片系统中也是有效的。本节主要提供适用于级联芯片系统的增量信息,并简要重复应用报告[2]中涵盖的一些重要信息。

5.1 设备配置

?????? 级联芯片系统中的AWR2243器件需要配置为MULTICHIP_MASTER或MULTICHIP_SLAVE。这可以通过消息AWR_CHAN_CONF_SET_SB完成。请注意,该消息允许SINGLECHIP选项,通常仅适用于单芯片系统。

?????? 只有一个AWR2243设备应该配置为MULTICHIP_MASTER。该AWR2243器件是级联芯片系统中的主芯片,产生FMCW本振并传送给其他MULTICHIP_SLAVE器件。

?????? 通常,MULTICHIP_MASTER的DIG_SYNC_OUT引脚连接到级联芯片系统中所有AWR2243器件的DIG_SYNC_IN引脚。这使得chirp的时序在AWR2243器件之间是同步的。

5.2 帧配置

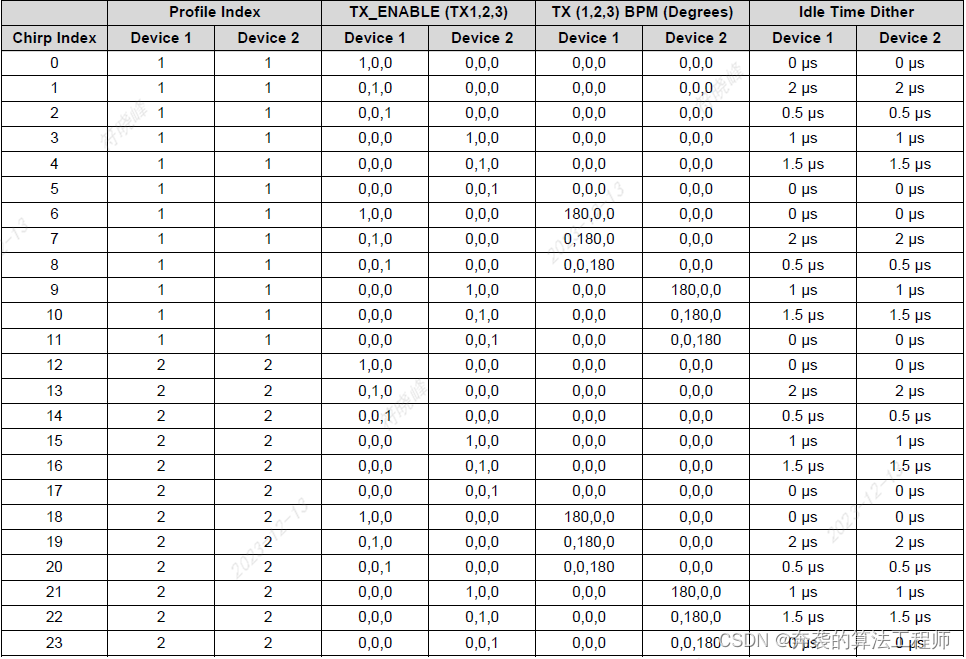

????????与FMCW chirp配置相关的重要参数在应用报告[2]中的可配置chirp RAM和chirp配置文件一节中进行了解释。这些包括FMCW chirp的启动频率,斜率,持续时间,RX增益,采样率,发射机输出功率和相移。使用消息AWR_PROFILE_CONF_SET_SB(属性配置)、AWR_CHIRP_CONF_SET_SB(chirp配置)和AWR_FRAME_CONF_SET_SB(帧配置)将这些参数编程到设备中。

????????属性配置消息为雷达前端最多四个属性编程参数,这些参数在帧期间是静态的。帧配置消息定义构成帧的一组chirp的结构和顺序,以及帧重复率和请求的帧数。chirp本身是使用chirp配置消息定义的,该定义包括每个啁啾与一个已定义的配置文件、要启用的TX通道和TX相位的关联。此外,chirp配置消息允许一些参数的增量但独立的chirp浮动,即使这些chirp与相同的配置文件相关联。可浮动参数包括空闲时间、FMCW启动频率和FMCW斜率。

????????有些参数需要在级联系统中的所有AWR2243设备上进行相似的配置,而其他参数可能不同。它们在第5.2.1节中有详细说明。

5.2.1 跨AWR2243设备的类似配置

????????通过配置文件配置消息,期望所有时序和频率参数的配置与级联芯片系统中的所有AWR2243器件完全相似。时序参数是指:空闲时间,斜坡结束时间,RX ADC采样率,采样开始时间和每个chirp的ADC采样数。频率参数为:起始频率和FMCW斜率。此外,通过帧配置消息传递的时序参数也需要在设备之间匹配。这些包括帧周期和要生成的帧数。

????????通常,通过chirp配置消息配置的时序参数的增量浮动预计在AWR2243设备上也是相似的。此外,请注意,频率浮动参数在从芯片中没有意义,因为只有主芯片根据频率参数生成本振信号。

????????跨AWR2243器件的时序参数的相似性确保MULTICHIP_SLAVES在完成全部或部分在内部帧时序可能参与的任何校准或监控后,及时为每帧做好准备。鉴于可能存在RF子系统可能具有RF频率相关性能,AWR2243器件之间频率参数的相似性确保了实际chirp期间校准结果的有效性。

5.2.2 AWR2243设备间不一致配置

?????? TX通道启动,在相同的chirp期间,通过chirp配置消息给出的BPM配置可能在AWR2243设备之间有所不同。如果启用了每个chirp相移,则TX相移设置也是如此。通过跨AWR2243设备的不一致属性配置消息,RX增益和TX功率等参数的变化也是可以接受的。

5.3 帧触发

????????可以使用帧触发消息AWR_FRAME_TRIG_MSG触发帧。

????????帧配置消息,在前面的章节中简要介绍,允许配置帧被直接触发使用帧触发消息(SWTRIGGER模式)或通过硬件引脚上的高脉冲,称为SYNC_IN或DIG_SYNC,随后接收帧触发消息(HWTRIGGER模式)。SWTRIGGER模式的触发不确定性为几十微秒(帧重复率没有不确定性)。HWTRIGGER模式的触发不确定性要低得多,这将在后面的章节中详细介绍。

????????在级联芯片系统中,通常将MULTICHIP_SLAVE设备配置为HWTRIGGER模式,并由MULTICHIP_MASTER设备触发。MULTICHIP_MASTER设备通常以SWTRIGGER模式触发。

????????通常,主机处理器需要向从设备发出帧触发消息,使它们准备好接收来自主设备的DIG_SYNC_IN。接收到确认后,主机处理器可以向主设备发出帧触发消息。这开始了一系列帧(与帧配置消息中编程的一样多),并且对于每个这样的帧,主设备在其DIG_SYNC_OUT引脚上产生高脉冲,该引脚通过DIG_SYNC_IN引脚导致所有芯片同步启动chirp时序、传输和接收。

5.4 示例使用

????????在两个芯片级联系统中配置到AWR2243器件的重要参数列在这里,以说明使用可能性。虽然这里只显示了两个设备,但是可以将示例扩展到更多设备(其中一个是主芯片,其他设备是从芯片)。

表3 通道配置消息

| Parameter | Device 1 | Device 2 |

| Cascade Configuration | MULTICHIP_MASTER | MULTICHIP_SLAVE |

表4 属性配置消息

| Parameter | Device 1 | Device 2 |

| Profile 1 Start Frequency | 77 GHz | 77 GHz |

| Profile 1 FMCW Slope | 30 MHz/μs | 30 MHz/μs |

| Profile 1 Idle Time | 10 μs | 10 μs |

| Profile 1 Ramp End Time | 30us | 30us |

| Profile 1 Sampling Rate, no. of samples | 5 MSPS, 128 | 5 MSPS, 128 |

| Profile 1 TX power (backoff) | 0 dB | 2 dB |

| Profile 2 Start Frequency | 78 GHz | 78 GHz |

| Profile 2 FMCW Slope | 60 MHz/μs | 60 MHz/μs |

| Profile 2 Idle Time | 15 μs | 15 μs |

| Profile 2 Ramp End Time | 60us | 60us |

| Profile 2 Sampling Rate, no. of samples | 5 MSPS, 256 | 5 MSPS, 256 |

| Profile 2 TX power (backoff) | 0 dB | 2 dB |

表5 chirp配置消息

备注:时序浮动参数芯片间不同但各设备相似

表6 帧配置消息

| Parameter | Device 1 | Device 2 |

| Start Chirp Index | 0 | 0 |

| End Chirp Index | 23 | 23 |

| Number of loops | 8 | 8 |

| Frame Periodicity | 50ms | 50ms |

| Number of Frames | 100 | 100 |

| Trigger Mode | SWTRIG | HWTRIG |

????????帧触发消息的顺序如下:

????????1. 向设备2发出帧触发消息(如果存在更多从设备,则向其他从设备发出)

????????2. 接收来自设备2(和其他从属设备)的确认

????????3. 发送帧触发消息到设备1(主)

????????这样,从级联系统中的所有AWR2243设备串联生成所需的帧数。

5.5 其他使用

????????虽然只详细解释了一些用法,但可能有微小的变化。这里简要介绍一下。

????????在HWTRIGGER模式下可以触发所有的AWR2243设备(包括主芯片)。为此,主机需要生成周期合适的DIG_SYNC_IN脉冲,并馈送到所有芯片(包括主芯片)的DIG_SYNC_IN引脚。

????????上面的大部分注释都是使用基本框架配置消息(即AWR_FRAME_CONF_SB)编写的,为了便于解释。可以使用AWR_ADVANCED_FRAME_CONF_SB来实现更高级的chirp或帧结构。在这种情况下,DIG_SYNC_IN脉冲出现在每个触发(或子帧或帧-待定)的开始。如果这种高级帧配置与主机的SWTRIGGER一起使用,那么主机需要相应地生成脉冲。

6 AWR2243级联系统优势

?????? 本应用报告中介绍的AWR2243级联解决方案具有许多关键优势。

????????AWR2243在本振路径上集成了20 GHz PA(功率放大器)和LNA(低噪声放大器),从而无需在PCB传输线使用分立PA和LNA。每个AWR2243器件为每个本振输出路径集成单独的20 GHz PA(一个PA用于FMCW_CLKOUT,另一个用于FMCW_SYNCOUT),并为FMCW_SYNCIN1/2 本振输入路径的每个内部分支集成单独的LNA。通过使用位于BGA两侧的多个FMCW_CLKOUT/SYNCOUT 本振输出端口和FMCW_SYNCIN1/2 本振输入端口,可以最大限度地减少PCB上的20 GHz 本振路由。此外,对板载本振路由的频率进行了优化选择。在板上路由20GHz本振而不是80GHz毫米波信号可以最大限度地减少板上路由损耗、噪声和成本。

????????虽然阐述了只有几个拓扑的两芯片和四芯片级联,不过这些例子可以扩展到使用四个以上芯片的级联系统。总体而言,这里解释的特性使设计和制造具有低成本、尺寸和功耗的高性能雷达系统成为可能。

7 参考资料

1. AWR2243 Interface Control Document (ICD)

2. Texas Instruments: Programming Chirp Parameters in TI Radar Devices

3. Texas Instruments: AWR2243 Single-Chip 76- to 81-GHz FMCW Transceiver Data Sheet

4. MMWCAS-RF-EVM product page

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!