JESD204B协议、仿真

JESD204B协议

1、什么是JESD204B

JESD204B是一种针对ADC、DAC设计的传输接口协议。包括协议四层,分别为:物理层、链路层、传输层、应用层。

物理层:约束接口规范(SEDES CML),串化,线速率等。

链路层:并行数据组帧(添加控制位 约束位),8B/10B编码,链路建立

传输层:链路建立后,传输ADC的数据,以半字节为单位。

应用层:用户解析ADC数据并使用

SERDES:串行器/解串器。它是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,提升信号的传输速度,从而大大降低通信成本。

CML:电流驱动的电平标准。

JESD204B与TTL,CMOS,LVDS等接口标准的区别:TTL,CMOS,LVDS都是物理层的电平标准,JESD204B在物理层上是SERDES接口,CML电平标准

2、ADC接口发展历史

从COMS ->LVDS ->JESD204B。

1)CMOS:如AD7606B(速度250k),CMOS单端,有16个数据引脚,D0-D15,熟读是几十M,跑到百兆的话信号不好。

2)LVDS:低压差分接口,优点是抗干扰强,底摆伏,速度快,但是需要的引脚多,存在信道偏移。如AD9230,速度为1.923G,数据通过差分引脚输出,FPGA中可以使用原语IBUFGS差分转单端信号。需要使用比较多的引脚,如16位的ADC,采样速率为500M,线速率为16*500=8000M=8G,8000M / 1923M=4.160,可以计算出需要使用5根线,加上是差分信号,需要10根线。(所谓的信道偏移,ADC通过引脚输入FPGA的数据不能同时到达,需要以最慢的那个为标准)

3)JESD204B:速度快,使用SERDES接口,CML标准,不存在信道偏移,引脚少,支持多片同步。

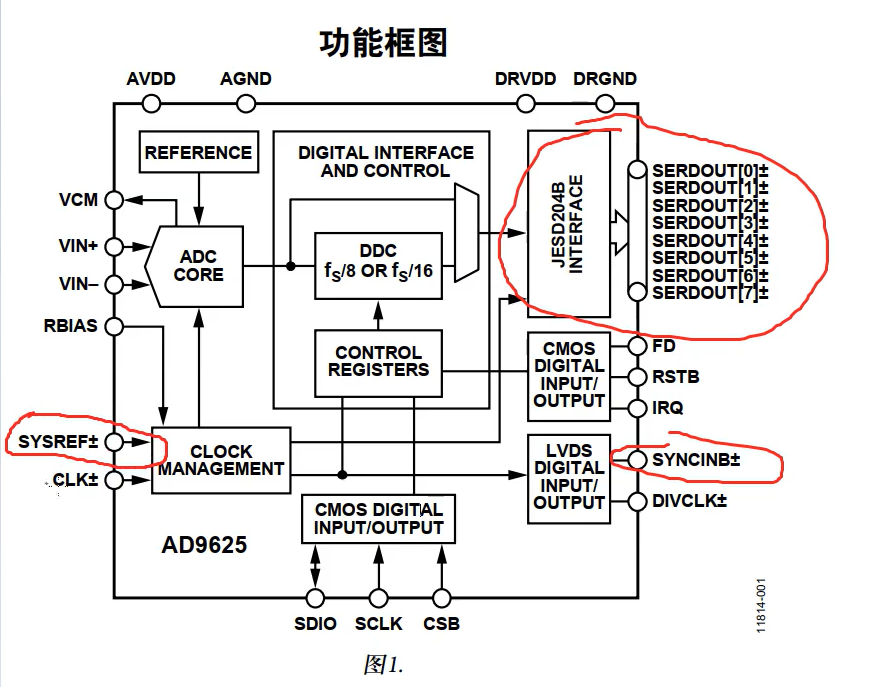

3、JESD204B接口信号

1)SEDOUT1~N:数据线

2)SYSREF:确定性延时多帧时钟

3)SYNC:同步信号

4、M,N,N’,F,K是什么意思

M:204B接口中转换器的数量,双通道(数据)ADC就是M=2,两个单通道(数据)ADC也是M=2.连接几个204B接口。

N:ADC的分辨率,12bit =ADC,N=12;16bit ADC ,N=16;

N’:以半字节为单位(4bit)的分辨率,如12bit 的ADC ,N’=12bit / 4=3;常用的有14bit、16bit,此时的N’=4,14bit也是用16bit来传输,空出来的2bit使用CS、T补位,CS是控制位,T是结束位;

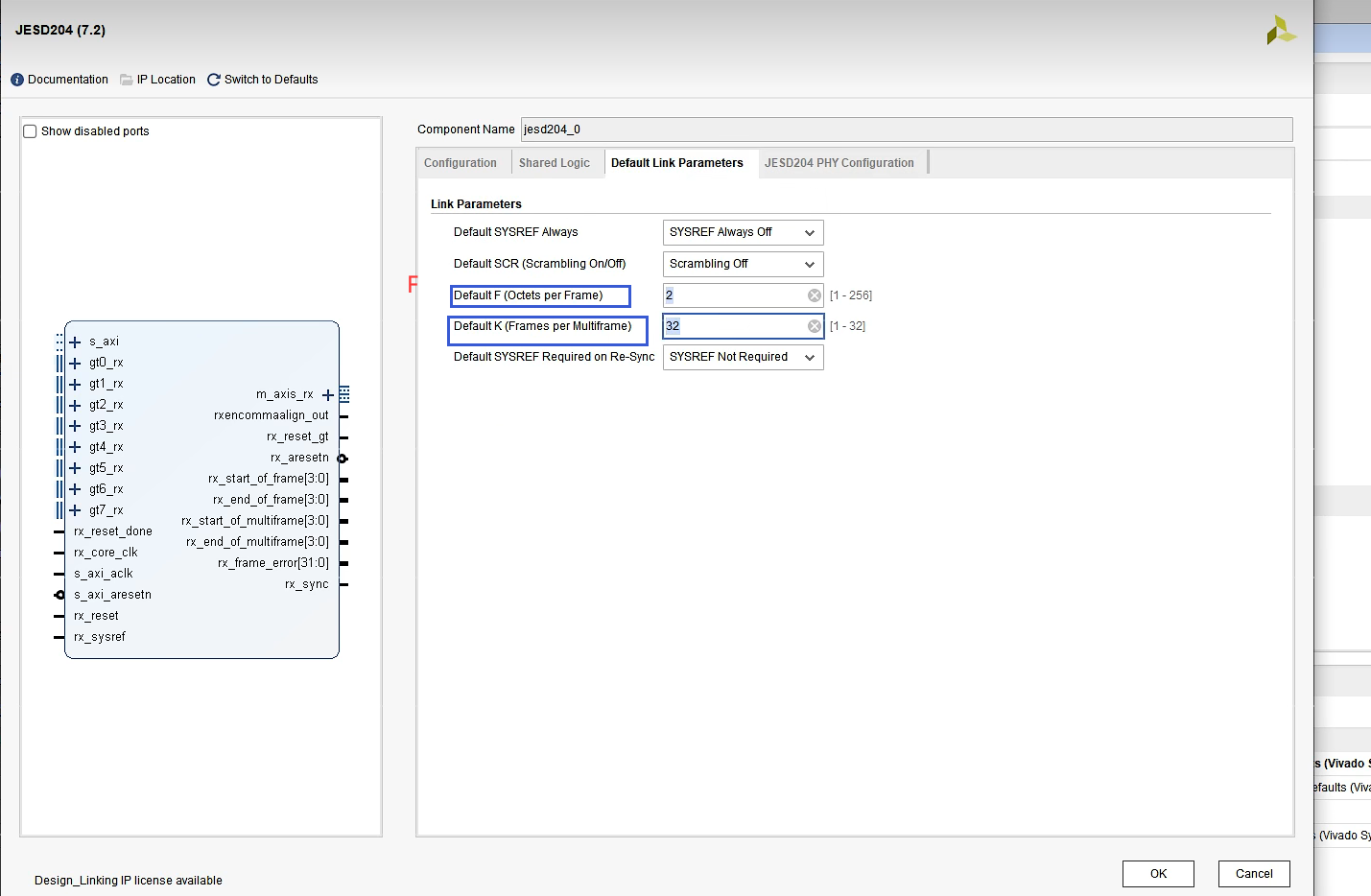

F:每一帧中的字节数

K:多帧中包含多少个帧

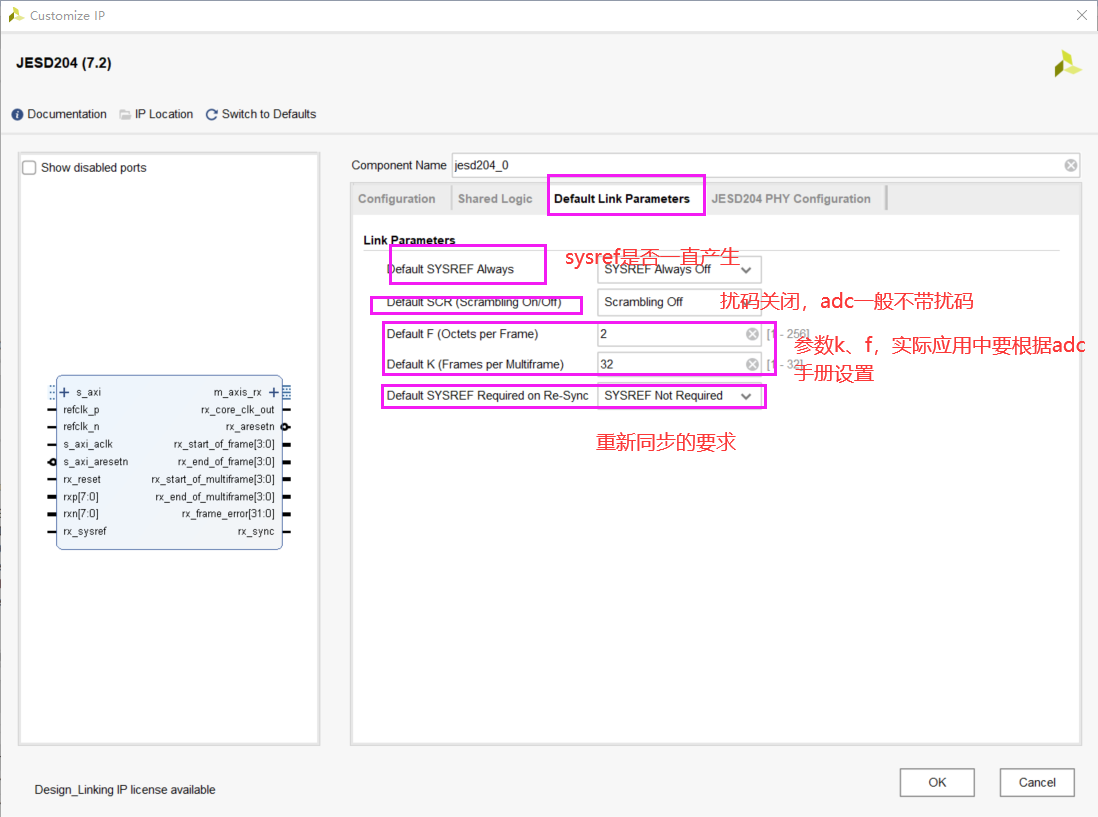

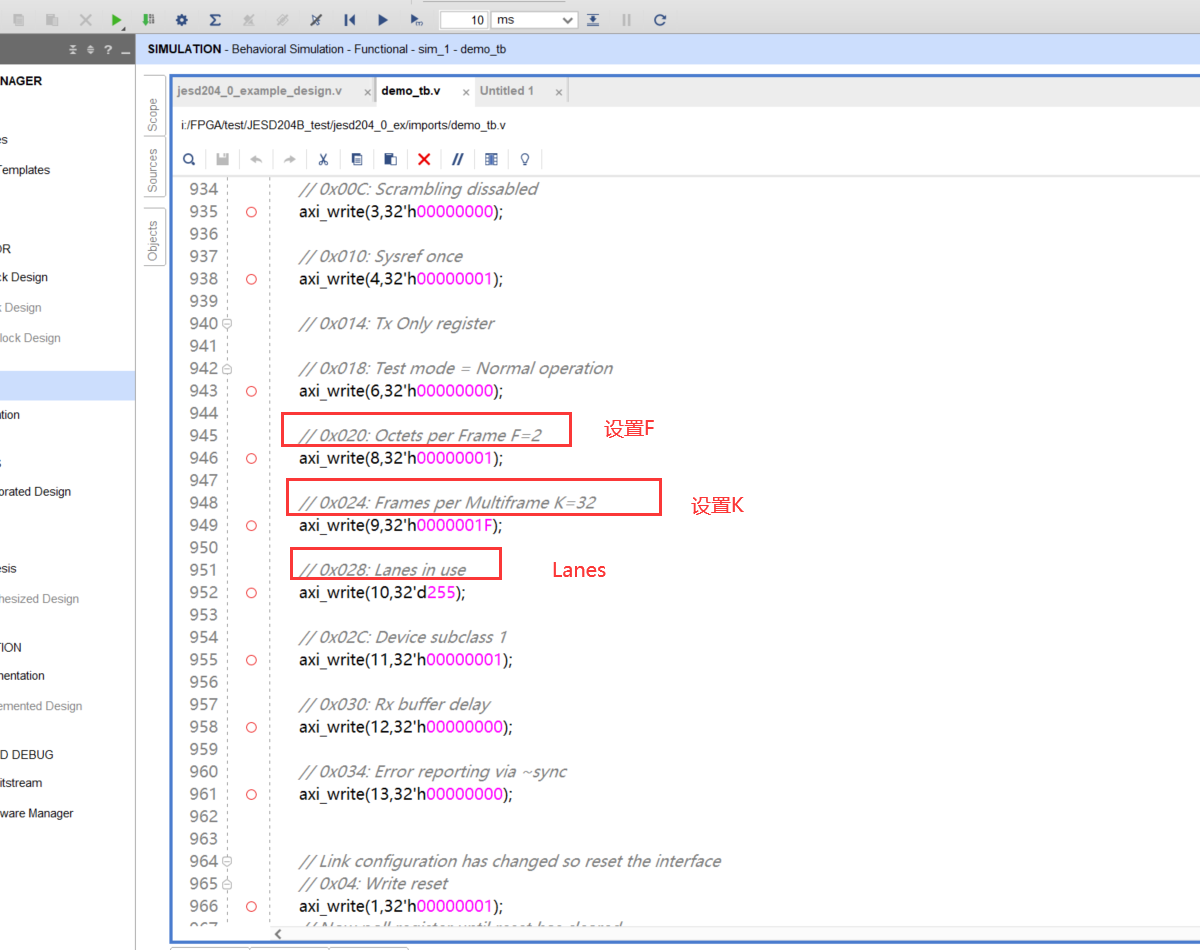

下图就是配置IP过程的F和K参数:

5、基础知识

1)确定性延时:需要关注信道偏移的问题。从发送机发送数据快开始到接收器释放数据BUF时的这一段时间是确定的。

2) 8B/10B直流平衡:解决码元跳变问题,8B代表8bit,将8bit扩展为10bit,保证这个字节中0和1的数量是相等的。因此直流分量是0,所以在高速接口中都是交流耦合的。

3)CDR:时钟复位技术

4)GT收发器:xilinx器件的IP核

5)接收机缓冲区:接收器释放数据BUF-RDB(RX-delay-buf)

6)Lane:数据线

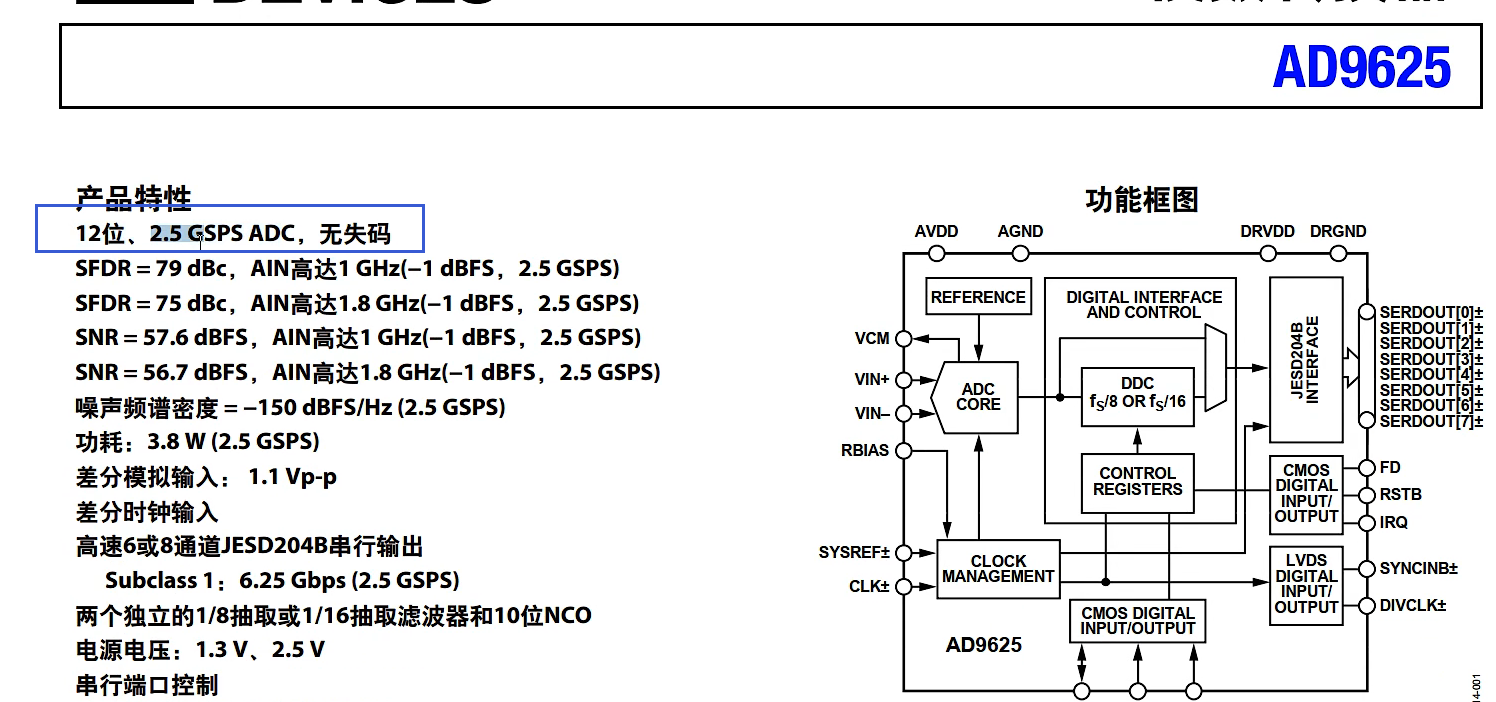

7)线速率:举例子AD9625,有8根数据线,12bit(12bit是以半字节为单位),采样速率为2.5G ,12bit时N’可以是3也可以是4,假设N’=4,那就是16bit ,总的线速率为16bit *2.5G/(0.8)=50G,每一根数据线的速率 50G/8根 = 6.25G,下图中subclass的值为6.25G刚好对得上。解码的时候会消耗2bit的效率,8/10=0.8,这就是0.8的由来。

7)时钟速率计算

线速率/40=6.25G/40=156.25 MHZ

8)LMFC:多帧时钟计数器:JESD204B以多帧为基础进行传输,在传输多帧期间,这个LMFC的计数器会进行累加,累加的范围为0到(F * K)/ 4- 1;这个计数器是用于同步发送器和接收器,当接收器接收到每根线路上的数据之后释放buf。通过SYNC信号进行同步

9)RBD:RX BUF DATA,全部接收完数据,释放buf

6、JESD204B协议时序解读

链路层分为3个阶段:

1)代码组同步CGS

a)接收到SYNC拉高之后,开始连续向接收机发送K码

b)校准LMFC计数器,和数据边界对齐

c)LMFC0 ~ ( F*K-1 )

d)保证链路参数是正确的,可以正常的传输数据;

2) 初始化通道对齐ILAS

a)主要是发ADC中的配置信息反馈给FPGA

b)由4个多帧组成,多帧开始符\R\,多帧结束符是\A\,其中配置信息包含在第二帧,1、3、4帧其中数据都不需要关心,自增信息。

3) 用户数据

这个阶段就是根据ADC手册进行接收ADC数据,并使用。

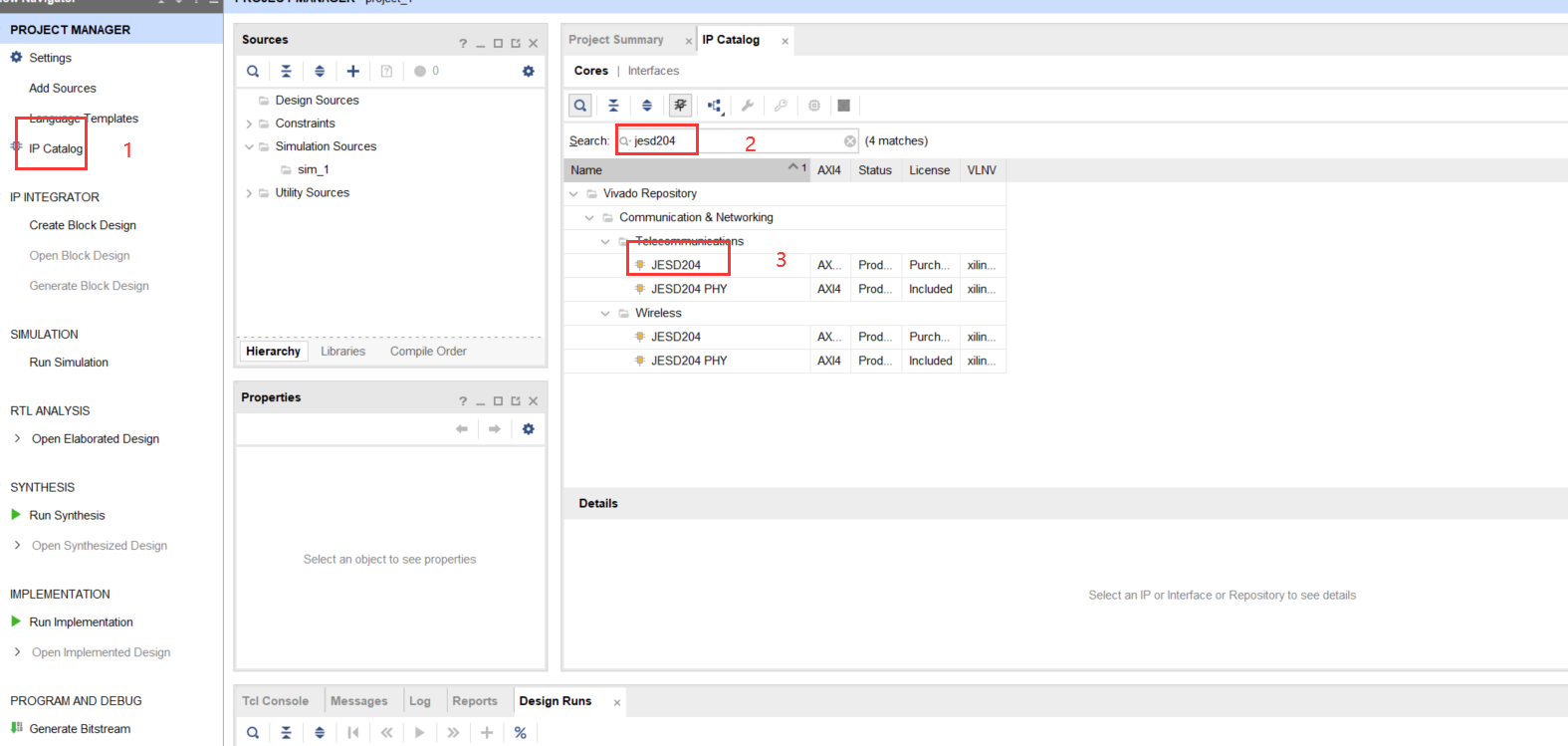

7、JESD204B IP核仿真步骤

建立工程后,按照下面图引出IP核

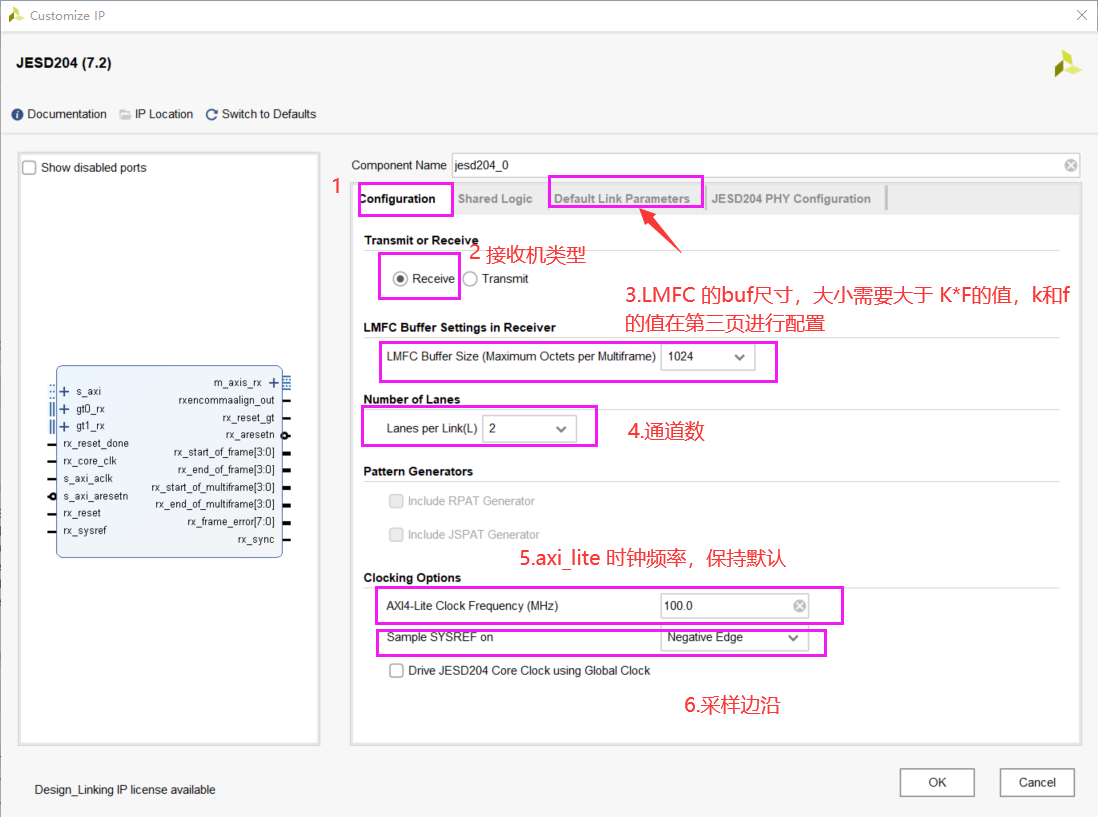

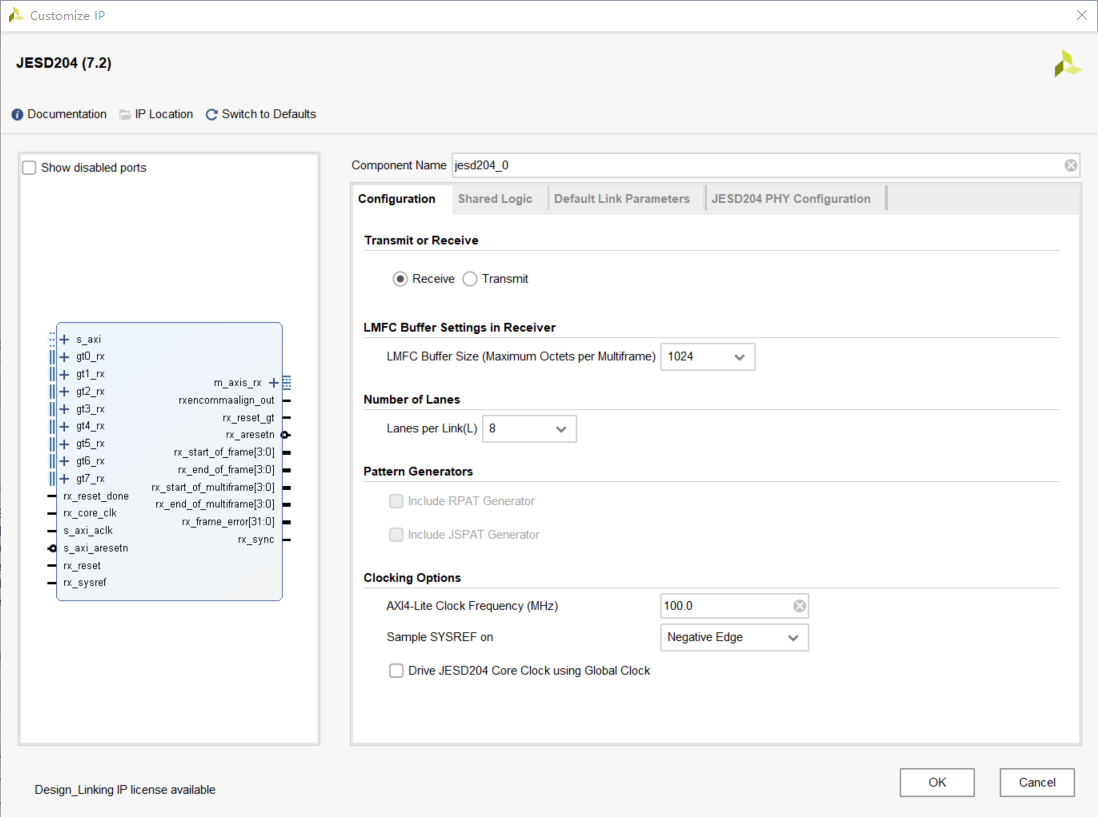

配置IP核:

1)

第一页配置后的参数:

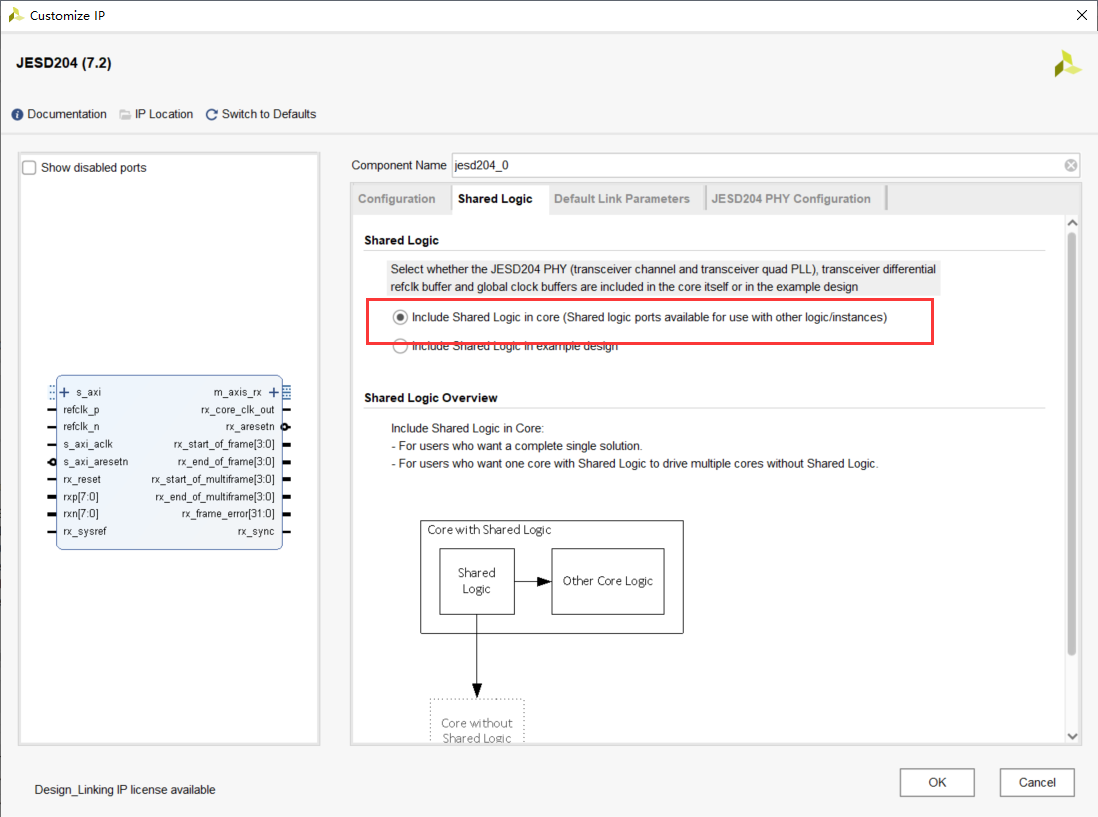

2)第二页配置

3)第三页配置

4)第四页配置:

点击ok,这就配置完毕,接着右键ip核,加入官方的示例代码

然后就会加载响应的文件,vivado会自动开启一个新的窗口

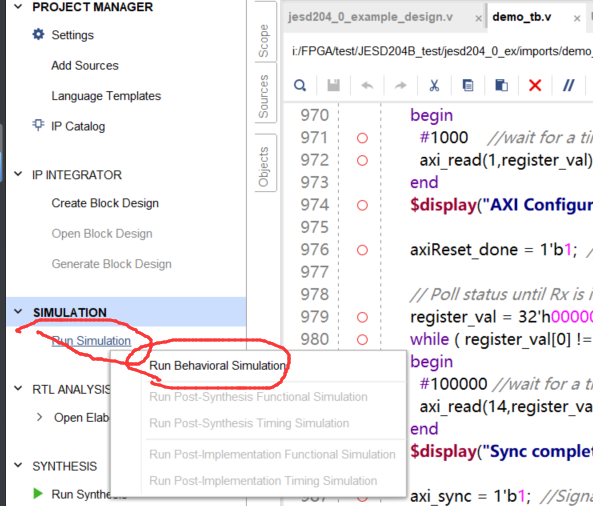

点击运行仿真:

8、部分代码解析,波形查看

1)读版本号

对应波形的位置

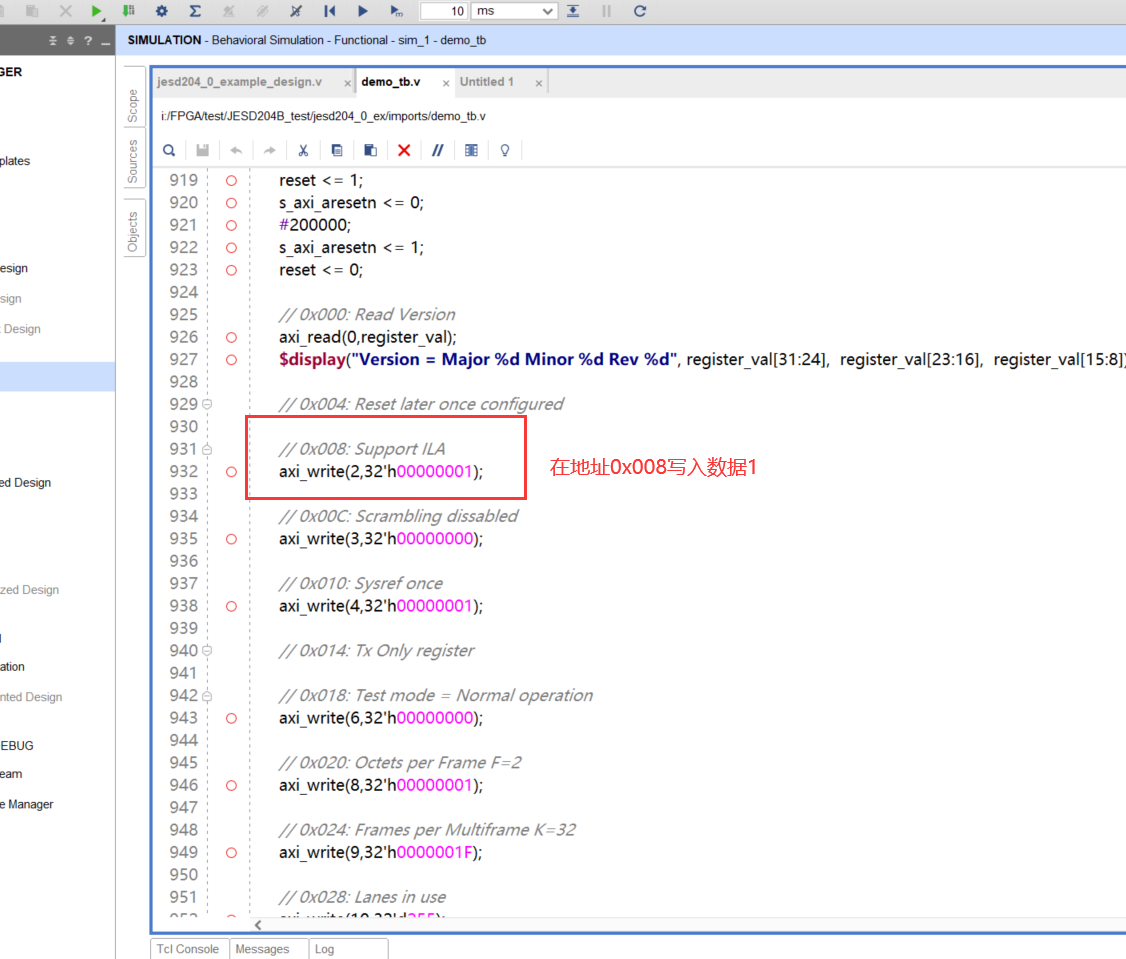

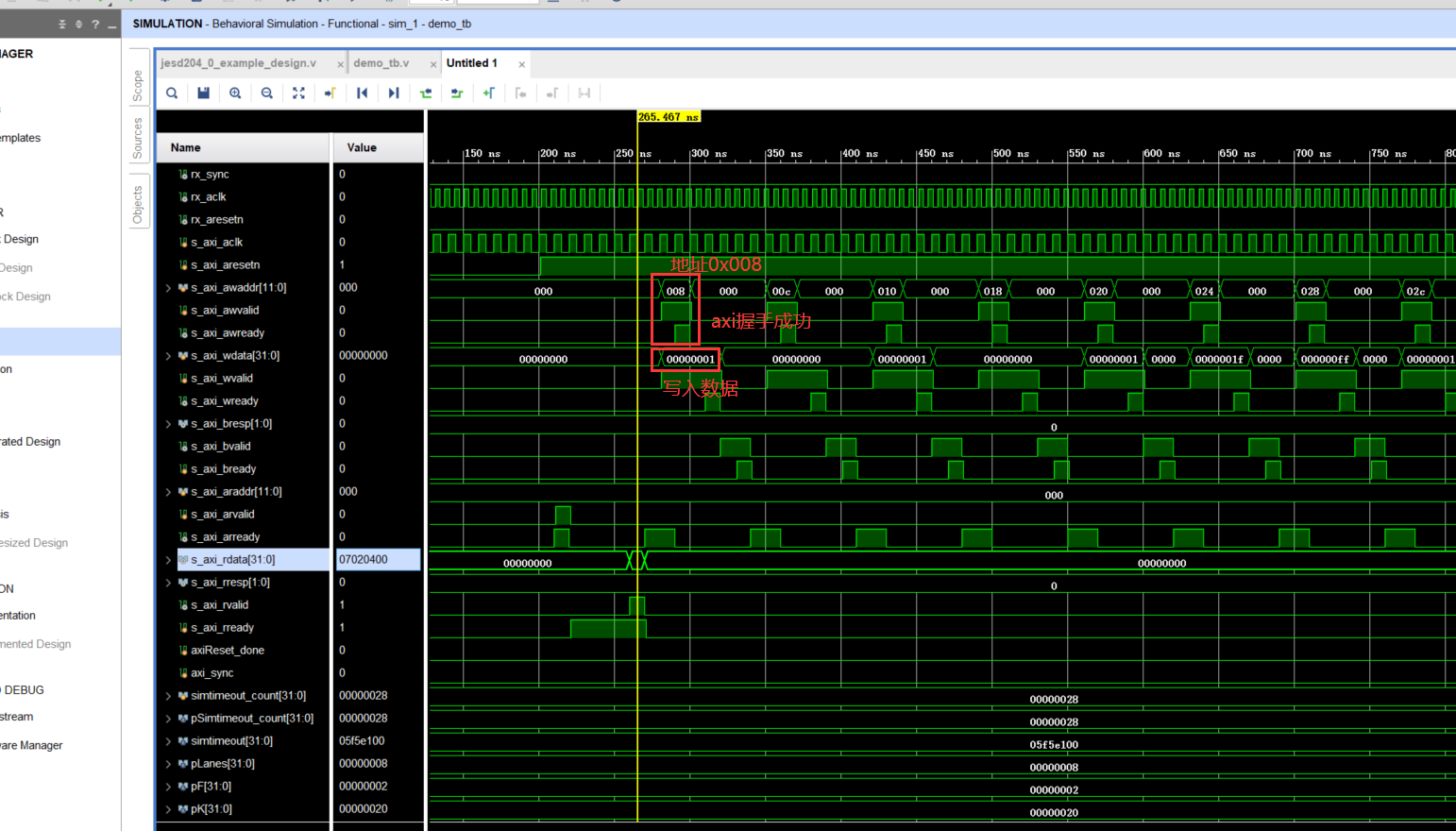

2)下一个操作:在地址0x008处写1

对应波形的位置

3)下面的代码,设置相应的寄存器,寄存器的配置需要查看芯片手册:

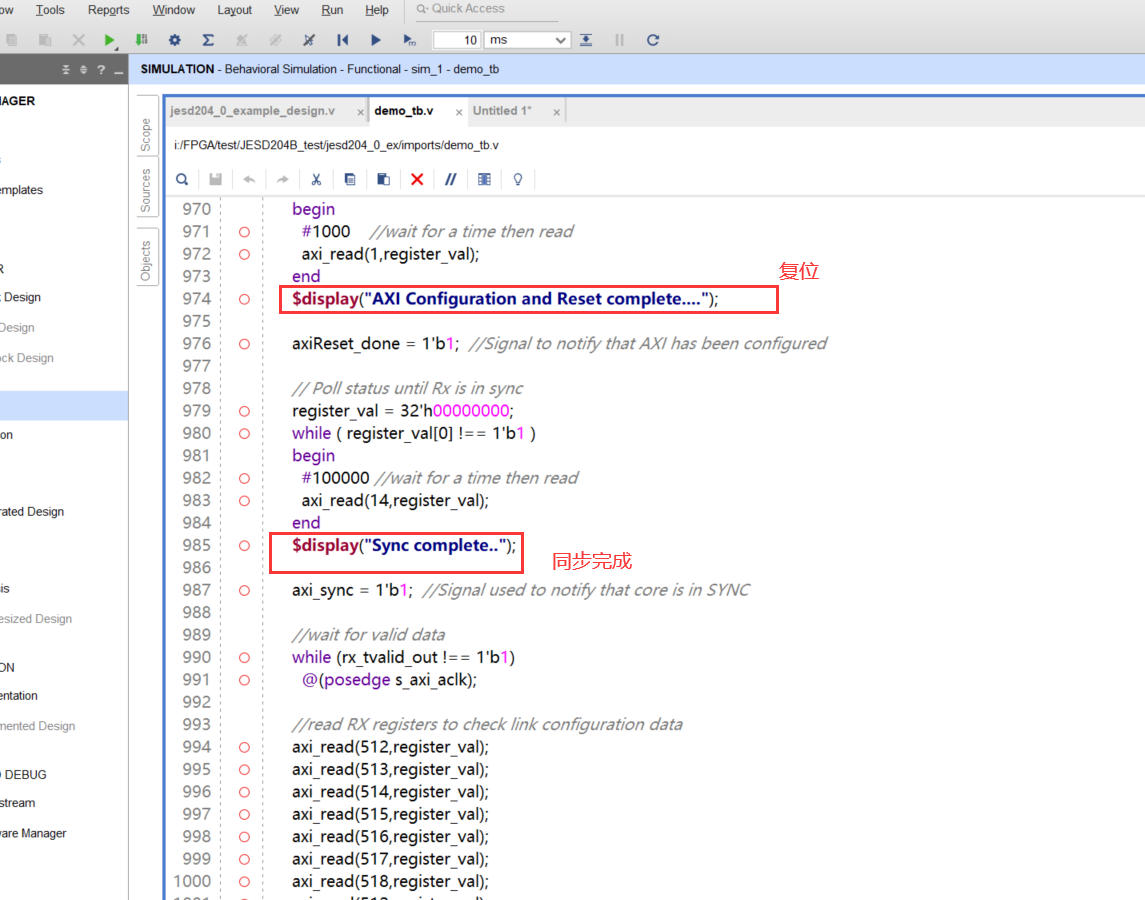

4)同步信号:

同步完成对应的波形位置:

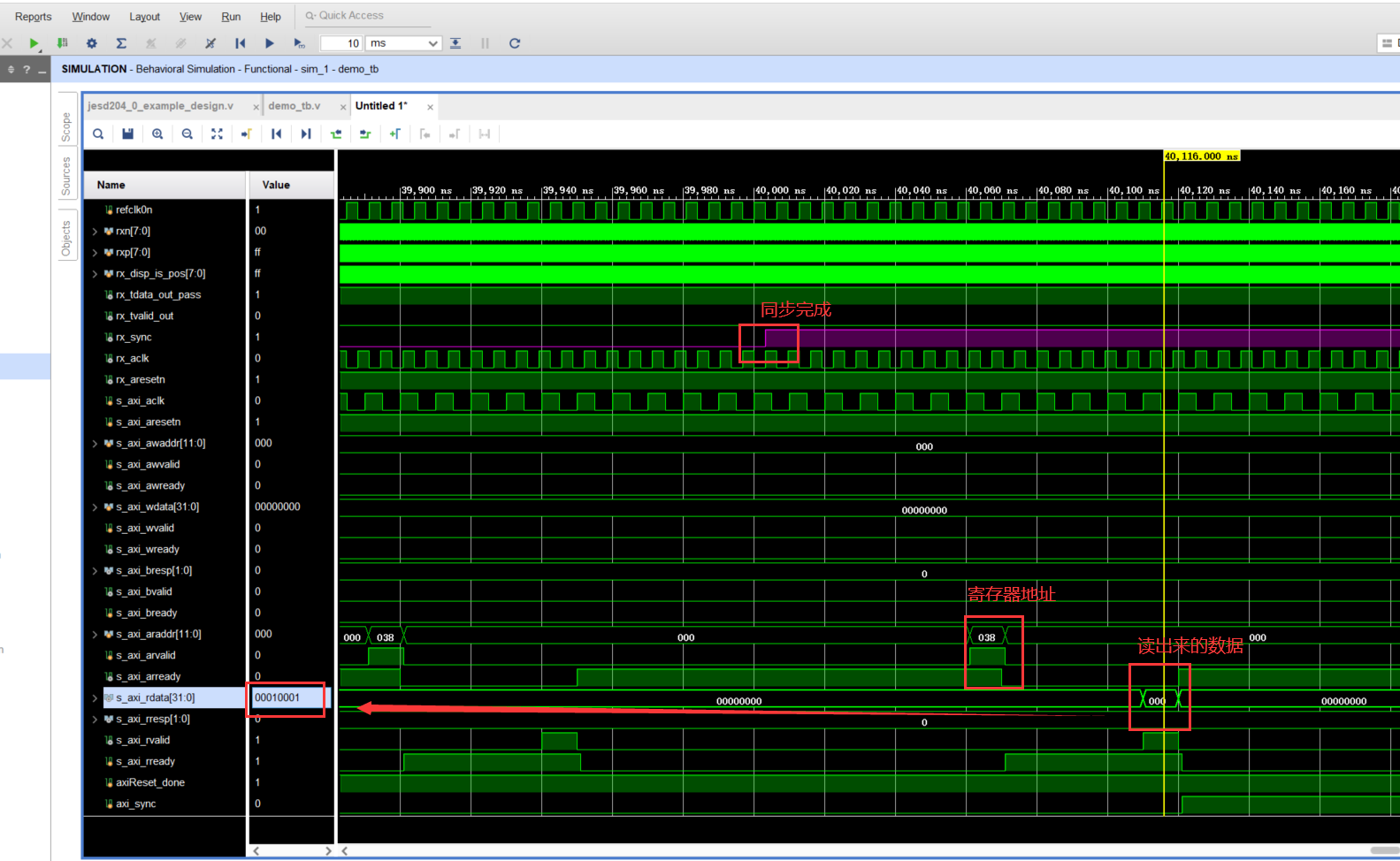

5)同步完成之后读十六进制地址为38的寄存器的数据

对应的波形,读到00010001这个数值之后代表同步完成了,sync信号确实是拉高了

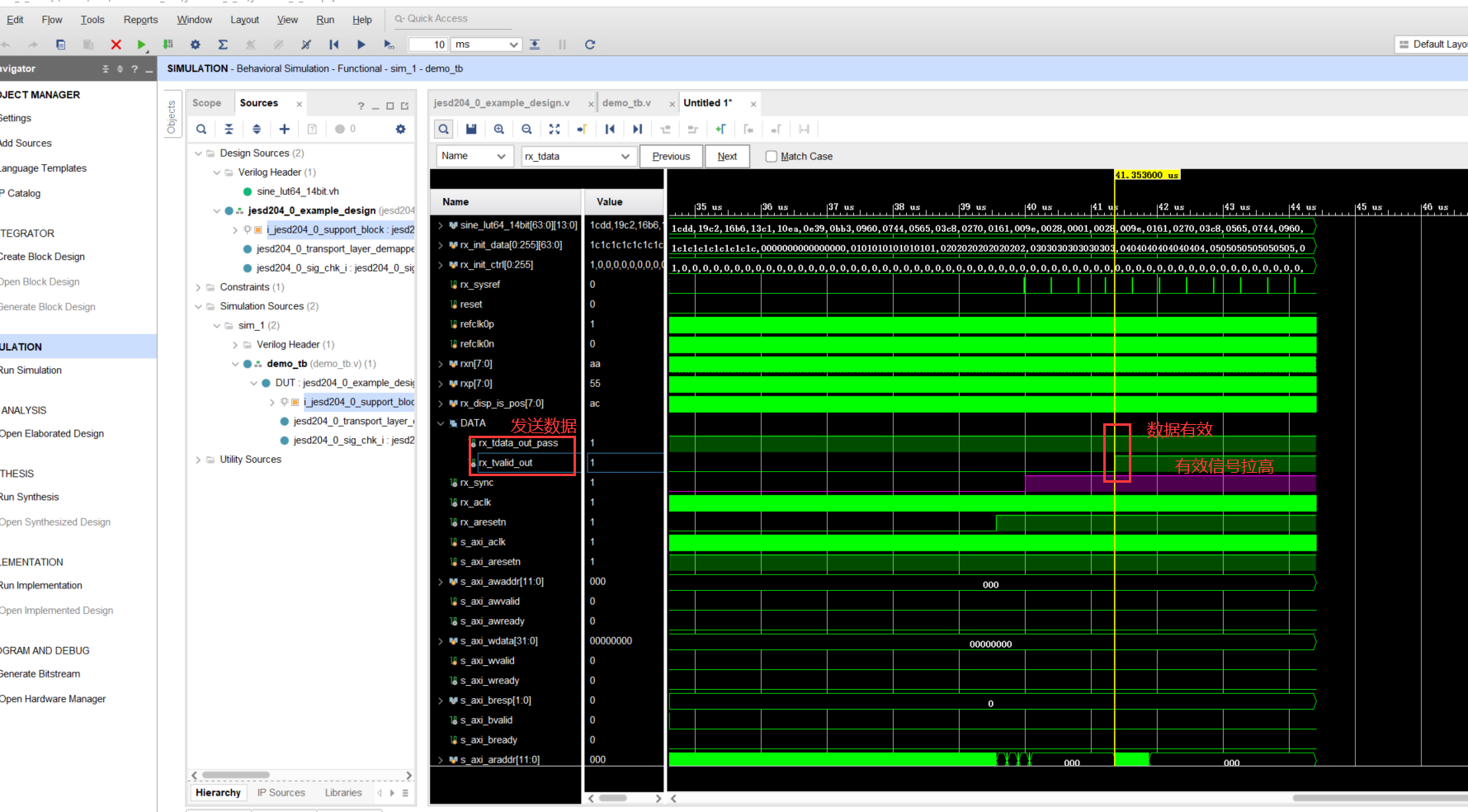

6)最终得到的ADC数据

--晓凡 2023年12月27于武汉书

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!