数字集成系统设计——设计约束

2024-01-02 12:57:17

目录

?

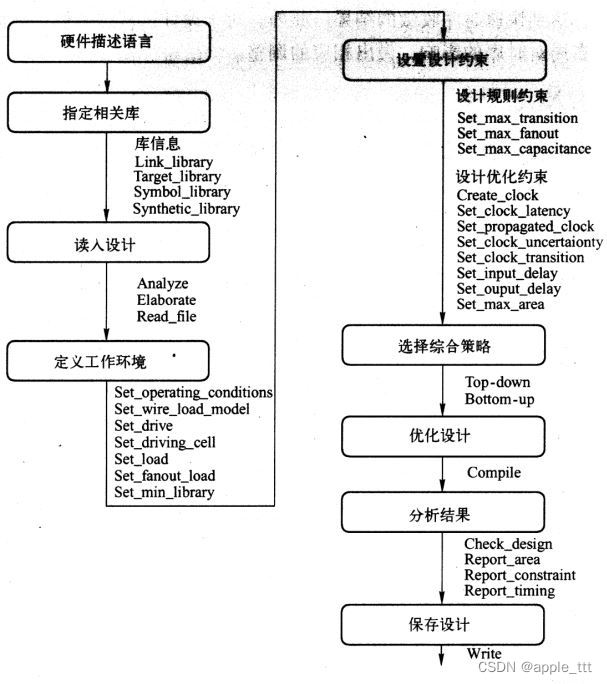

一、综合流程

? ? ? ? 设计约束是综合过程中的一个步骤,我们先介绍一下一个完整的综合流程来帮助大家更好地理解设计约束。

1.1 硬件描述语言

????????Verilog或VHDL描述的 RTL代码

1.2 指定相关库

????????基于特定工艺的单元库,需指出无需综合的单元(RAM、ROM、I/O等)和多单元组合,以及生成电原理图的单元图形化信息

1.3 读入设计?

????????分析、细化和读入RTL代码或网表、预编译设计等

1.4 定义工作环境

????????设置环境条件(工艺离散、工作电压、工作温度)、线负载模型、驱动强度、负载电容值、扇出值等

1.5 设置设计约束

1.5.1 设计约束规则

????????设置延迟、扇出、负载电容等的最大值

1.5.2 设计优化约束

????????设置时钟参数、输入输出延迟和最大允许面积等

1.6 选择综合策略

- Top-down将各层次模块同时综合,编译时间长,适合小规模设计,整体优化程度高;

- Bottom-up对各个子模块分别综合后再整合,适合大规模设计,编译速度快,可复用性强,但整体优化程度相对低

1.7 优化设计

????????对初步综合结果依据不同的优化策略进行优化(初始编译可设为低,最终设计可设为高)

?

1.8 分析结果

????????检查并报告综合结果(含面积、约束和时序)

?

1.9 保存设计

????????形成输出网表文件

?

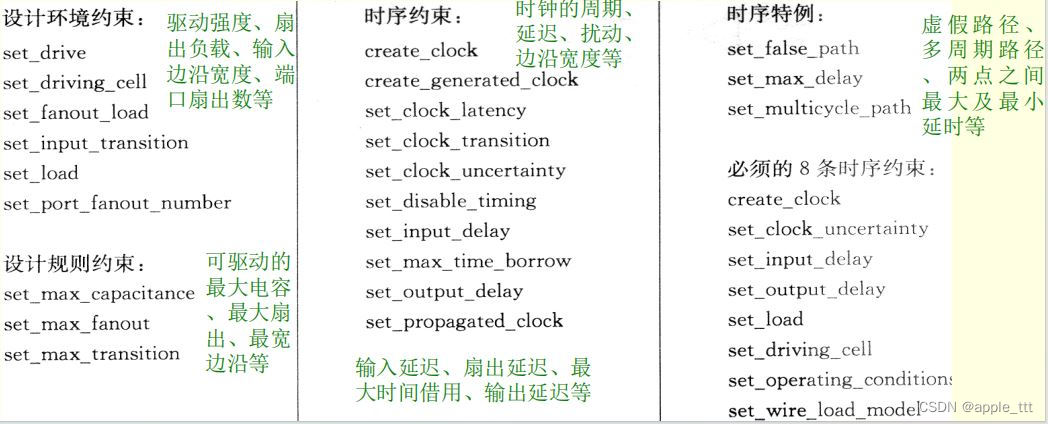

二、什么是设计约束

- 在逻辑综合、静态时序分析等时,需首先给出芯片或电路单元设计必须遵循的约束条件,称之为设计约束(design constraint)。

- 设计约束通常包括环境约束、设计规则约束和时序约束等

- DC中使用的设计约束被称为SDC(Synopsys Design Constraints),其脚本用?TCL(Tool Command Language )语言编写

- 更严格的约束有利于提高综合与分析的速度,而更宽松的约束则会得到更能满足客户要求的结果

三、时钟的定义

????????时钟周期通常根据系统工作时钟需求而定,在此基础上加10%裕量。时钟延时、抖动、边沿可根据系统需求而定,设得越小更容易实现时序收敛,但可能与真实情况差异越大。

?

四、端口特性与环境条件的定义?

五、工作条件的定义 ?

- 基于速度的工作条件:BC(Best Case)/TYP(Typical)/WC(Worst Case),最快速度(低温、高电压、强晶体管)/平均速度/最慢速度(高温、低电压、弱晶体管)

- 工作温度范围:COM(Commercial,0~+40℃)/IND(Industrial,-40~+70℃ )/MIL?(Military,-55~+125℃),商业/工业用/军用

- FET晶体管的驱动强度:Min/Typ/Max,最低强度(最长延时、最慢速度)/典型强度(中等延时)/最高强度(最短延时、最快速度)

- P沟道FET和N沟道FET的相对驱动强度:SNSP/SNWP/WNP等,如SNWP表示强N弱P,故驱动到0要比驱动到1快得多

- 综合条件表征:从最快到最慢条件的顺序一般是BCMIL→BCIND→BCCOM→TYP→ WCCOM→WCIND→WCMIL

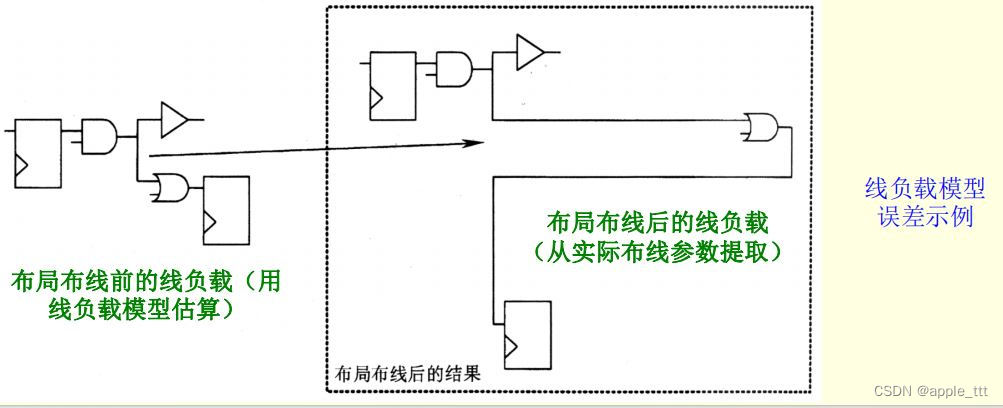

六、线负载模型

- 互连延迟对时序有重要影响,但逻辑综合时无布局布线信息,无法真实而精确地得到它,故常采用线负载模型(WLM,Wire Load Model)来估算之

- 线负载模型根据功能模块的规模、驱动逻辑门数目(扇出)以及相互间连线的统计估算值来估计连线的延时,在0.18μm以上工艺还是相当准确的,但在更小尺寸的工艺下,误差变得越来越大

- 通常库内有多种线负载模型(如set_wire_load_model – name MEDIum中的MEDIum),用于模拟不同规模模块内的线负载情况

?

文章来源:https://blog.csdn.net/apple_53311083/article/details/135297924

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!