复旦微裸机SD卡移植

Demo下的FatFs整个拷贝至BSP->librc下,不要和FSBL下的混了!!!!!

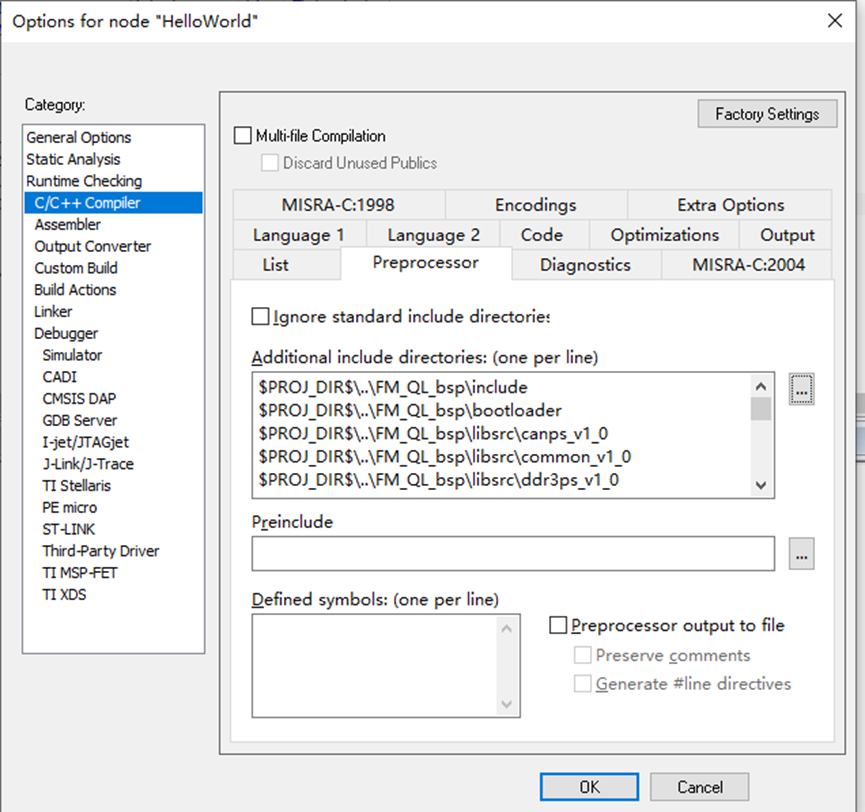

将头文件添加到编译环境

sdmmcps_v1_0整个替换

BootLoader下cache.c和cache.h替换

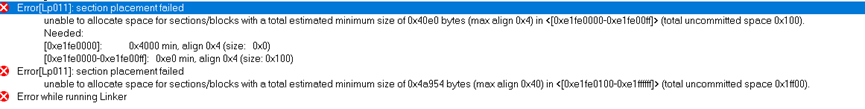

编译报错如下:

报错如下,因为片内ram满了,需要跑到ddr上

更改icf脚本

/*###ICF### Section handled by ICF editor, don't touch! ****/

/*-Editor annotation file-*/

/* IcfEditorFile="$TOOLKIT_DIR$\config\ide\IcfEditor\a_v1_0.xml" */

/*-Memory Regions-*/

/* ddr: first 1MB is uncacheable */

define symbol __AXI_DDR_START = 0x00200000;

define symbol __AXI_DDR_END = 0x3FFFFFFF;

define symbol __ICFEDIT_region_RAM_start__ = __AXI_DDR_START;

define symbol __ICFEDIT_region_RAM_end__ = __AXI_DDR_END;

/*-Sizes-*/

define symbol __ICFEDIT_size_mmutbl__ = 0x4000;

define symbol __ICFEDIT_size_vectors__ = 0x100;

define symbol __ICFEDIT_size_cstack__ = 0x40000;

define symbol __ICFEDIT_size_irqstack__ = 0x200;

define symbol __ICFEDIT_size_fiqstack__ = 0x200;

define symbol __ICFEDIT_size_abtstack__ = 0x60;

define symbol __ICFEDIT_size_undstack__ = 0x40;

define symbol __ICFEDIT_size_heap__ = 0x8000000;

/*-Exports-*/

export symbol __ICFEDIT_region_RAM_start__;

export symbol __ICFEDIT_region_RAM_end__;

export symbol __ICFEDIT_size_vectors__;

export symbol __ICFEDIT_size_cstack__;

export symbol __ICFEDIT_size_irqstack__;

export symbol __ICFEDIT_size_fiqstack__;

export symbol __ICFEDIT_size_heap__;

/**** End of ICF editor section. ###ICF###*/

define memory mem with size = 4G;

define region MMU_TBL_region = mem:[from __ICFEDIT_region_RAM_start__ size __ICFEDIT_size_mmutbl__];

define region VEC_region = mem:[from __ICFEDIT_region_RAM_start__+__ICFEDIT_size_mmutbl__ size __ICFEDIT_size_vectors__];

define region RAM_region = mem:[from __ICFEDIT_region_RAM_start__+__ICFEDIT_size_mmutbl__+__ICFEDIT_size_vectors__ to __ICFEDIT_region_RAM_end__];

define block CSTACK with alignment = 8, size = __ICFEDIT_size_cstack__ { };

define block IRQ_STACK with alignment = 8, size = __ICFEDIT_size_irqstack__ { };

define block FIQ_STACK with alignment = 8, size = __ICFEDIT_size_fiqstack__ { };

define block ABT_STACK with alignment = 8, size = __ICFEDIT_size_abtstack__ { };

define block UND_STACK with alignment = 8, size = __ICFEDIT_size_undstack__ { };

define block HEAP with alignment = 8, size = __ICFEDIT_size_heap__ { };

initialize by copy with packing=none { readwrite };

do not initialize { readonly section .noinit };

place in MMU_TBL_region { section .mmu_tbl };

place in VEC_region { section .vectors };

place in RAM_region { readonly };

place in RAM_region { section .cstartup };

place in RAM_region { readwrite, block IRQ_STACK, block FIQ_STACK, block ABT_STACK, block UND_STACK, block CSTACK, block HEAP };

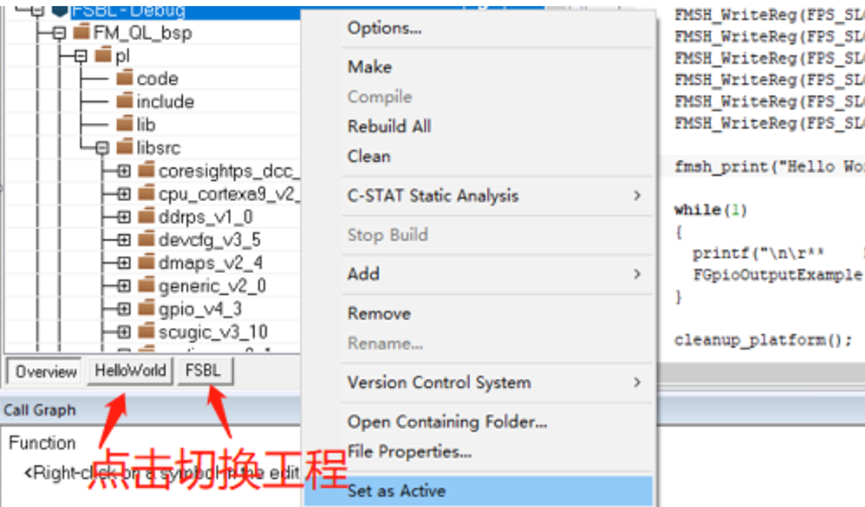

硬件导出fsbl和移植的工程文件,可以直接点击下面的工程标签切换

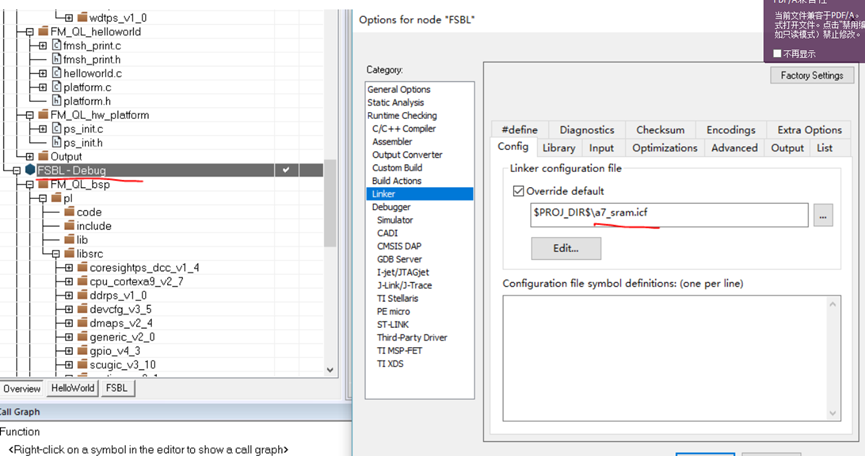

切换工程之后,配置一下对应的工程。同样右键点击 fsbl 工程,选择第一个 options,可以查看 fsbl 的 linker 的选型,

a7_sram.icf 表示是放到片内 OCM 里的

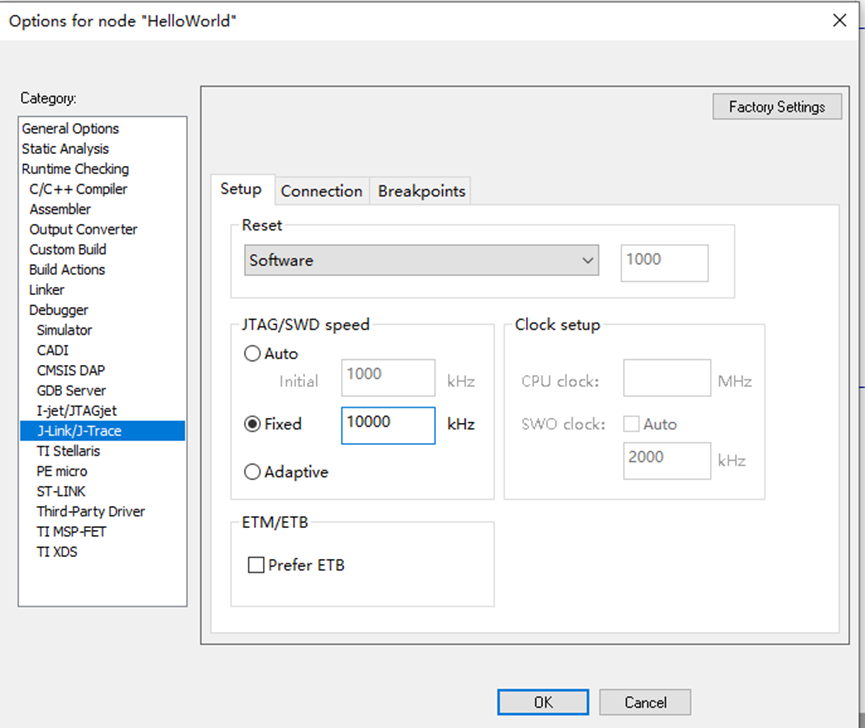

我们在 hello 工程上,点击右键之后选中 options,查看 linker 的 icf 文件,用a7_ahbsram.icf文件

改完链接脚本,还需要把 hello 工程里的 ps_init 屏蔽掉(platform.c中Status = ps_init();注释掉),不要再初始化 DDR 了,这里是因为 IAR 没有 ps_init.tcl 脚本来初始化外设包括 DDR,都是硬编码到应用程序的 main 入口处的 init_platorm 函数里了,所以必须手动屏蔽 DDR 初始化

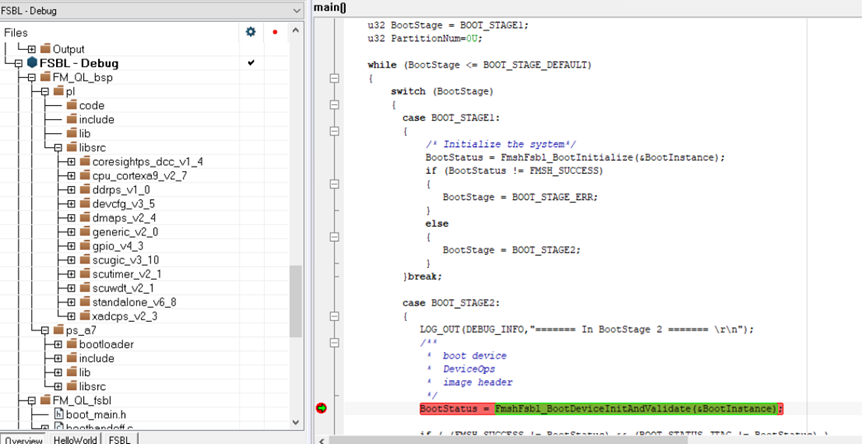

设置 fsbl 工程为 active(直接点击到 fsbl 工程就不需要这个操作),下载运行fsbl,在下图位置打上断点,断点只要在执行 ps_init 之后都可以。

运行到断点处,关闭 fsbl 调试界面:

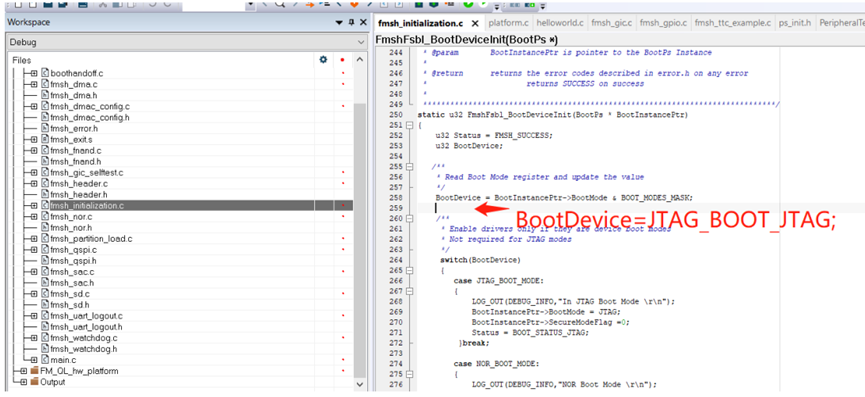

退出调试界面后面, 特别注意的是 IAR 打断点退出 debug 还会继续往前运行的,这个是 IAR 的 bug, 在线调试的话,如果硬件板子不好修改 boot mode 的跳线的话,即 MIO5 从高变低(qspi falsh 启动模式切到 jtag 启动模式)可以直接把用来初始化 DDR的 fsbl 的强制修改为 jtag 启动,这样的话这个 fsbl 也就不会去 qspi 加载后续镜像了,特别是可以避免 qspi 里的程序有问题会导致 cpu 挂死等问题导致 jlink 断链

退出调试,切换到helloworld工程再次调试即可

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!