verilog基础,连续赋值之组合逻辑-高级篇

总线:把同类线捆绑在一起形成总线,比如ADC,DAC的数据输出等。这里容易与通讯的总线相混淆。

总线的组合逻辑操作与基本逻辑操作基本一致,但是还是有一些区别,总线的组合逻辑是单值运算。他任然能够实现基本逻辑运算。

(1)总线拼接

(2)总线拆分

1. 总线与门

2.总线与非门

3.总线或门

4.总线或非门

5.总线异或门

6.总线同或门

verilog实现逻辑操作的算符如下

// The forllowing operators can be used on a bussed signal where all bits in the bus

// are used to perform the operation and a single bit output is resolved.

//

// & .... AND all bits together to make single bit output

// ~& ... NAND all bits together to make single bit output

// | .... OR all bits together to make single bit output

// ~| ... NOR all bits together to make single bit output

// ^ .... XOR all bits together to make single bit output

// ~^ ... XNOR all bits together to make single bit output

(1)总线拼接

通过bit的拼接形成总线,通过拼接算符{}来实现,坐标时高位,右边是低位。

代码

module assign1(

input a5,

input a1,

input a2,

input a3,

input a4,

output [1:0] y1,

output [3:0] y2,

output [5:0] y3

);

assign y1 = {a2,a1};

assign y2 = {a4,a3,a2,a1};

assign y3 = {a5,y2};

endmodule

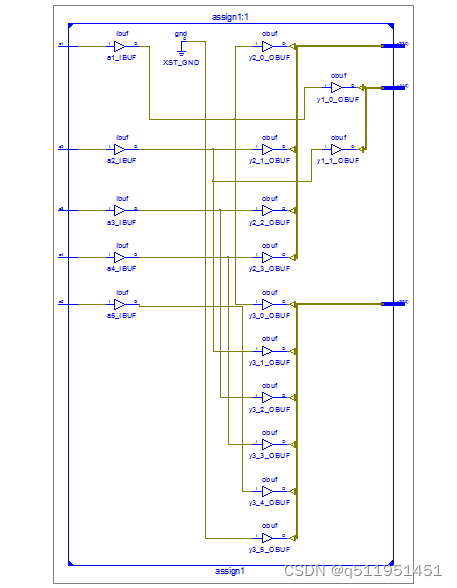

RTL结构图,总图可知,总线

技术原理图

(2)总线拆分

代码,拆分组装是经常遇到的,具体实现如下,这个比较灵活,它的本质就是线的重新排列,不需要消耗资源。

// 15 总线拆分

module assign1(

input [15:0]a,

output y1,

output [3:0] y2,

output [5:0] y3,

output [15:0] y4

);

assign y1 = a[2]; // 取出某一位

assign y2 = a[4:1]; // 取出部分为

assign y3 = {a[4:0],a[9]}; // 取出部分为

assign y4 = a; // 全拷贝

endmodule

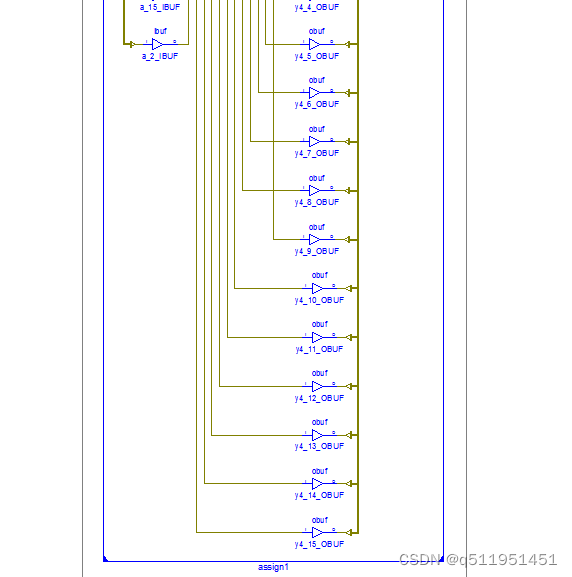

RTL结构图,这里没有内部了

技术原理图

1. 总线与门

总线的输入不在是单值,二十多值输入,可以看成式一个一维向量(vector)。以下定义了长度为2的总线a1,长度为4的a2以及长度为5的a3。并进行总线与操作。

module assign1(

input[1:0] a1,

input[3:0] a2,

input[4:0] a3,

output y1,

output y2,

output y3

);

assign y1 = &a1;

assign y2 = &a2;

assign y3 = &a3;

endmodule

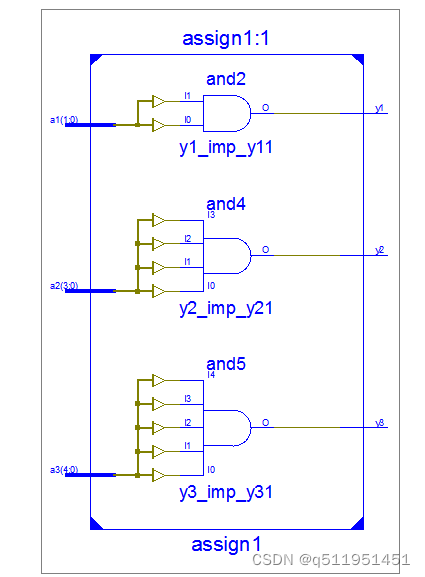

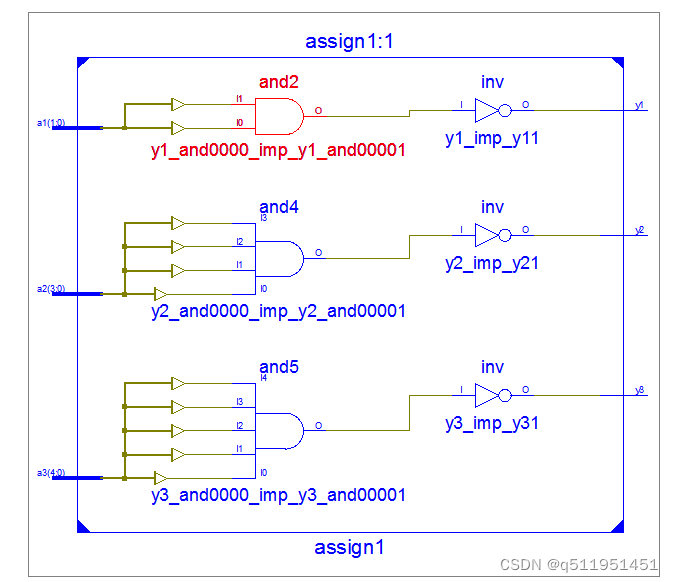

RTL结构图,总线与操作就是对总线上的各个位bit进行与运算。

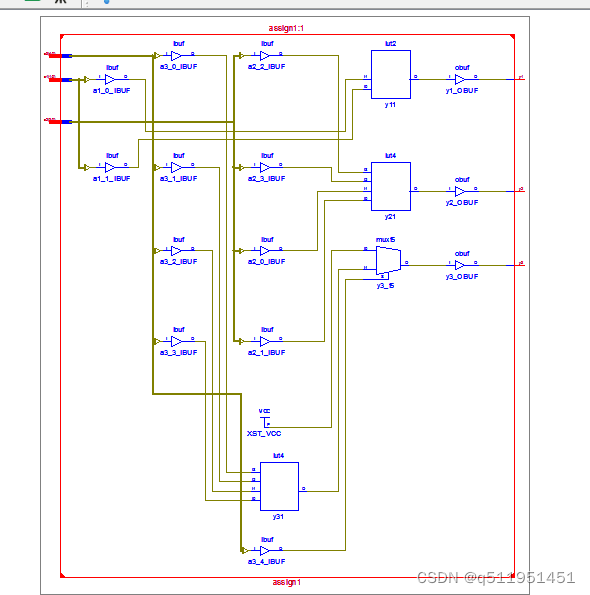

技术原理图,与逻辑运算依然可以通过lut查找表来实现,其中5输入与操作可以通过一个Lut+一个mux选择器来实现。

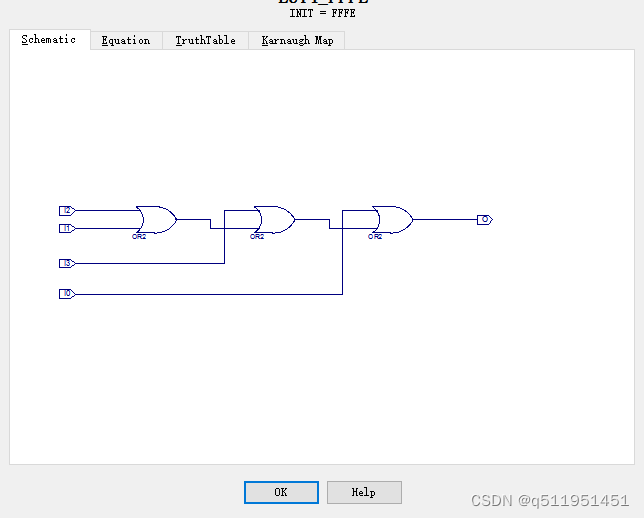

打开lut查找表,lut实现的功能就是与操作

2. 总线与非门

代码

module assign1(

input[1:0] a1,

input[3:0] a2,

input[4:0] a3,

output y1,

output y2,

output y3

);

assign y1 = ~&a1;

assign y2 = ~&a2;

assign y3 = ~&a3;

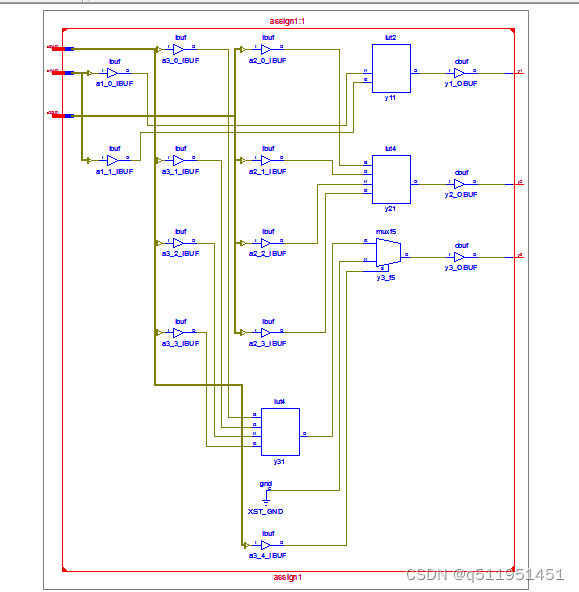

endmoduleRTL结构图,总线与非门就是在总线与门的基础上增加了一个反相器实现。

技术原理图,技术原理图也是在与门的基础上增加以及反相器实现。

3.总线或门

代码

module assign1(

input[1:0] a1,

input[3:0] a2,

input[4:0] a3,

output y1,

output y2,

output y3

);

assign y1 = |a1;

assign y2 = |a2;

assign y3 = |a3;

endmodule

RTL结构图,总线或门就是对总线上的各个位bit进行或运算。

技术原理图,依然是采用Lut查找表实现或运算。

4.总线或非门

代码

module assign1(

input[1:0] a1,

input[3:0] a2,

input[4:0] a3,

output y1,

output y2,

output y3

);

assign y1 = ~|a1;

assign y2 = ~|a2;

assign y3 = ~|a3;

endmoduleRTL结构图,在总线或门的基础上增加了一个反相器。

技术原理图,组合逻辑依然是使用Lut查找表实现。

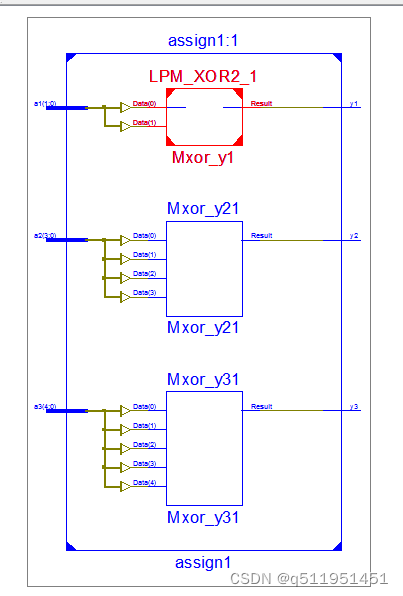

5.总线异或门

代码

module assign1(

input[1:0] a1,

input[3:0] a2,

input[4:0] a3,

output y1,

output y2,

output y3

);

assign y1 = ^a1;

assign y2 = ^a2;

assign y3 = ^a3;

endmodule

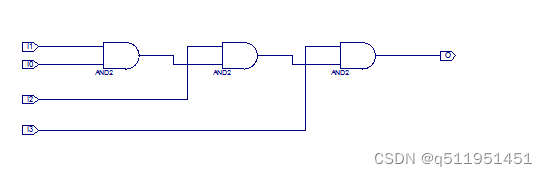

RTL结构图,看上去很很陌生,其实就是对各个位进行异或操作。

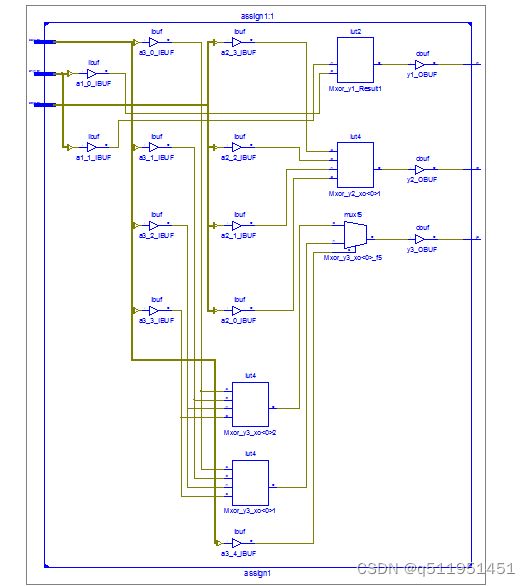

技术原理图,总而言之就是对各个位进行异或操作,使用Lut查找表来实现。具体功能可以进行测试。总线异或操作实际上就是数1个的奇偶位,如果为奇数输出1,否则为0。

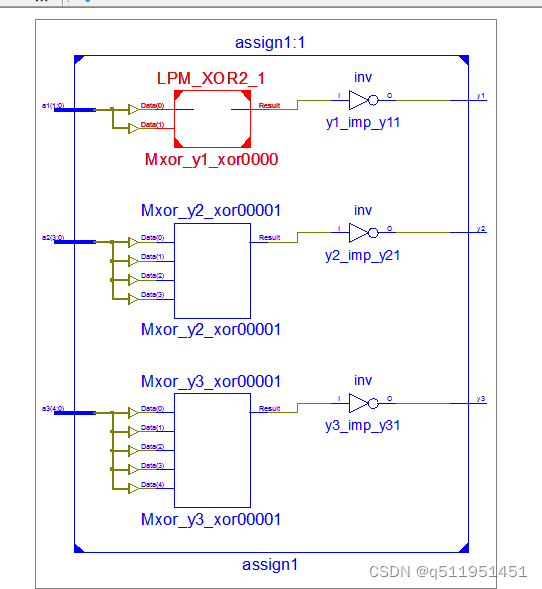

6.总线同或门

module assign1(

input[1:0] a1,

input[3:0] a2,

input[4:0] a3,

output y1,

output y2,

output y3

);

assign y1 = ~^a1;

assign y2 = ~^a2;

assign y3 = ~^a3;

endmodule

RTL结构图,在总线异或门之后增加一个反相器实现

技术原理图

总结

1. 总线逻辑运算是单值运算,他对各个位进行同一操作。

2.总线操作用法单一,但是简洁,在特定场合可以降低代码冗余量。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!