西南科技大学数字电子技术实验七(4行串行累加器设计及FPGA实现)预习报告

2023-12-14 11:41:44

一、计算/设计过程

说明:本实验是验证性实验,计算预测验证结果。是设计性实验一定要从系统指标计算出元件参数过程,越详细越好。用公式输入法完成相关公式内容,不得贴手写图片。(注意:从抽象公式直接得出结果,不得分,页数可根据内容调整)

(1)激励表

| 现态 | 输入 | 次态 | 输出 | 双稳输入 | ||

| Qn | E | F | Qn+1 | S | J | K |

| 0 | 0 | 0 | 0 | 0 | 0 | x |

| 0 | 0 | 1 | 0 | 1 | 0 | x |

| 0 | 1 | 0 | 0 | 1 | 0 | x |

| 0 | 1 | 1 | 1 | 0 | 1 | x |

| 1 | 0 | 0 | 0 | 1 | x | 1 |

| 1 | 0 | 1 | 1 | 0 | x | 0 |

| 1 | 1 | 0 | 1 | 0 | x | 0 |

| 1 | 1 | 1 | 1 | 1 | x | 0 |

?

?

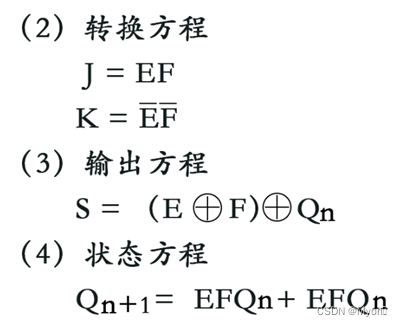

设计思路:根据书上的提示,设计出三个组合电路的原理图,然后将其组合起来,根据四位

右移寄存器的特点,和输出结果与输入结果的激励方程,可以设计出相应的转换

方程和输出方程,最终将其组合起来。

二、画出并填写实验指导书上的预表

无

三、画出并填写实验指导书上的虚表

无

四、粘贴原理仿真、工程仿真截图

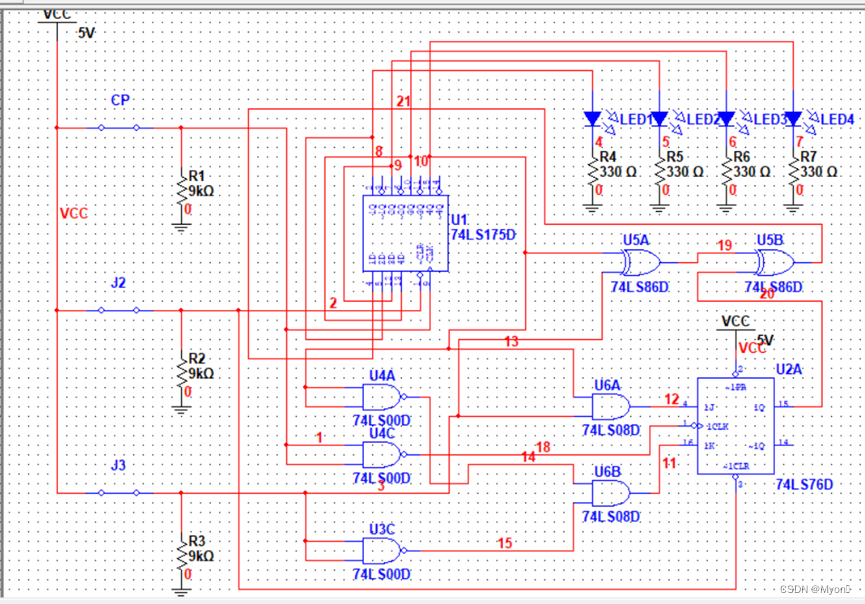

原理仿真:

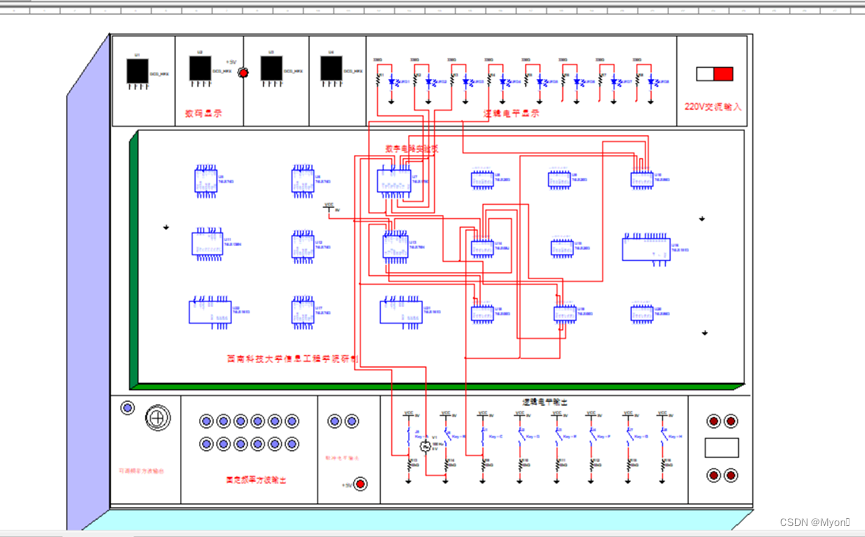

工程仿真:

?

?

文章来源:https://blog.csdn.net/Myon5/article/details/134990676

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!