紫光FPGA DDR3 IP使用和注意事项(axi4协议)

2023-12-17 23:32:20

紫光DDR3 IP使用

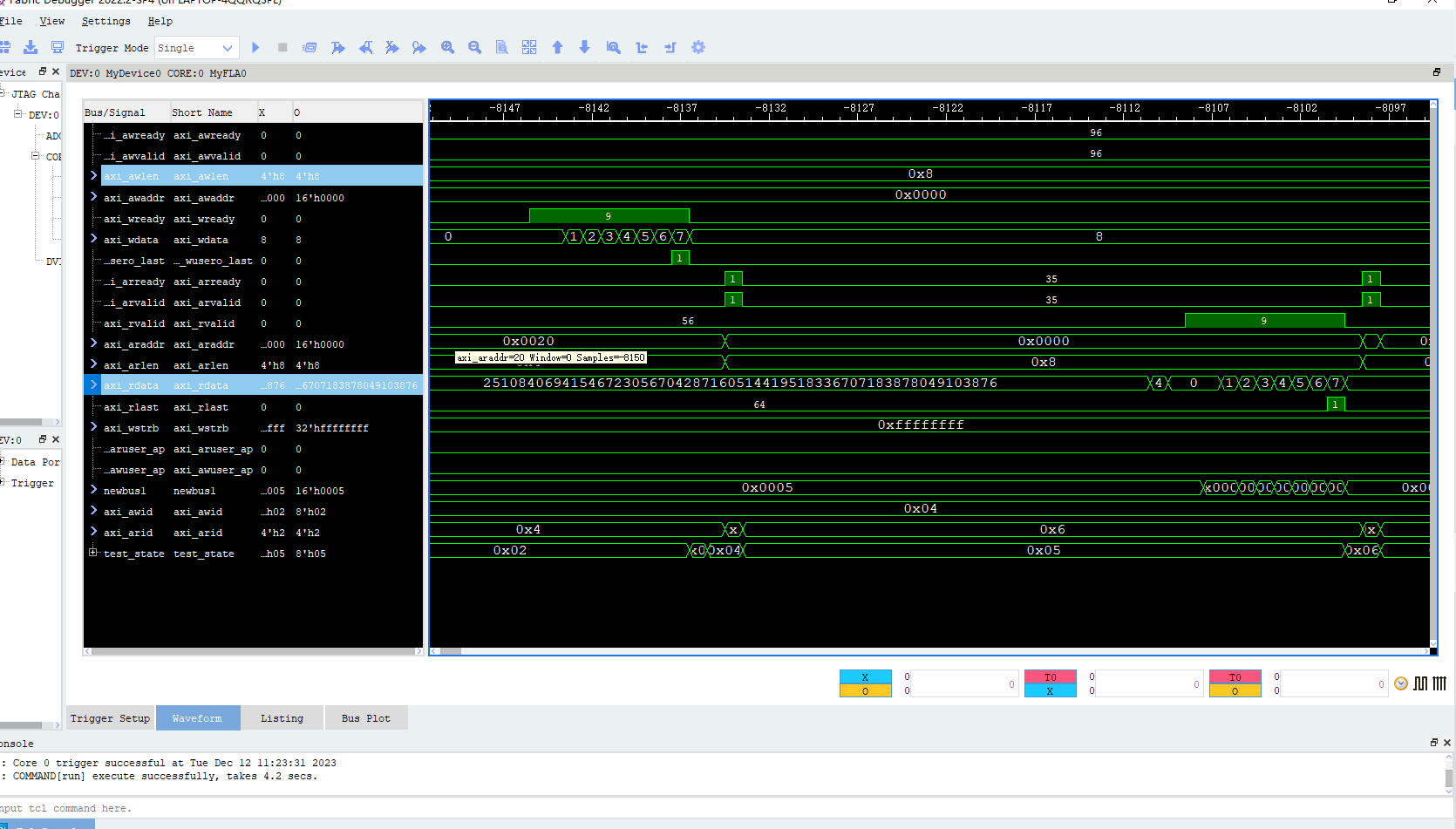

对于紫光ddr3 IP核的使用需要注意事情。

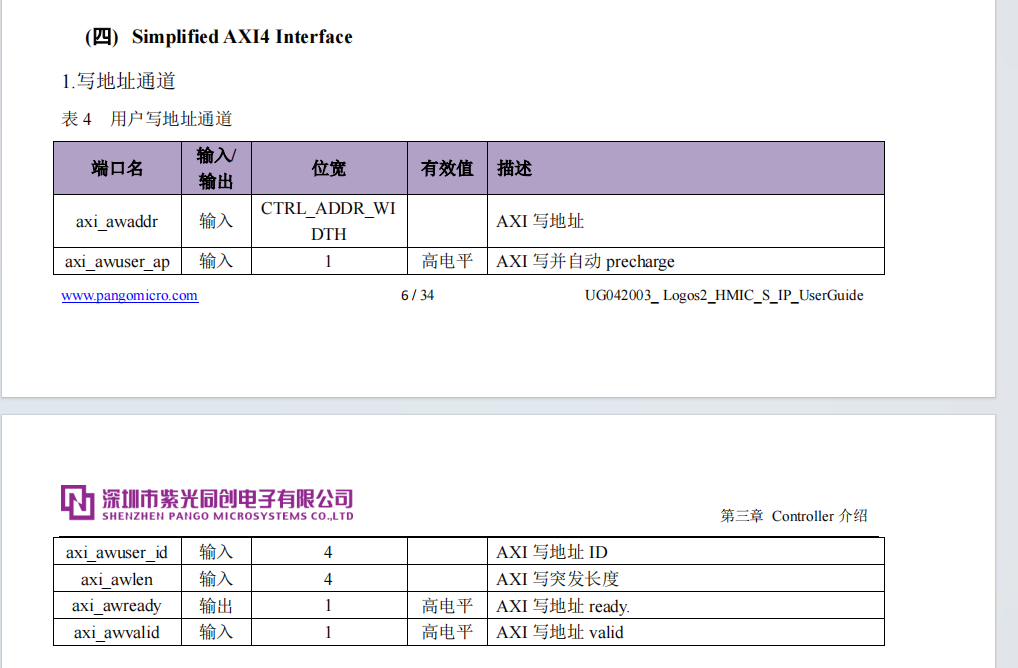

阅读ddr ip手册:

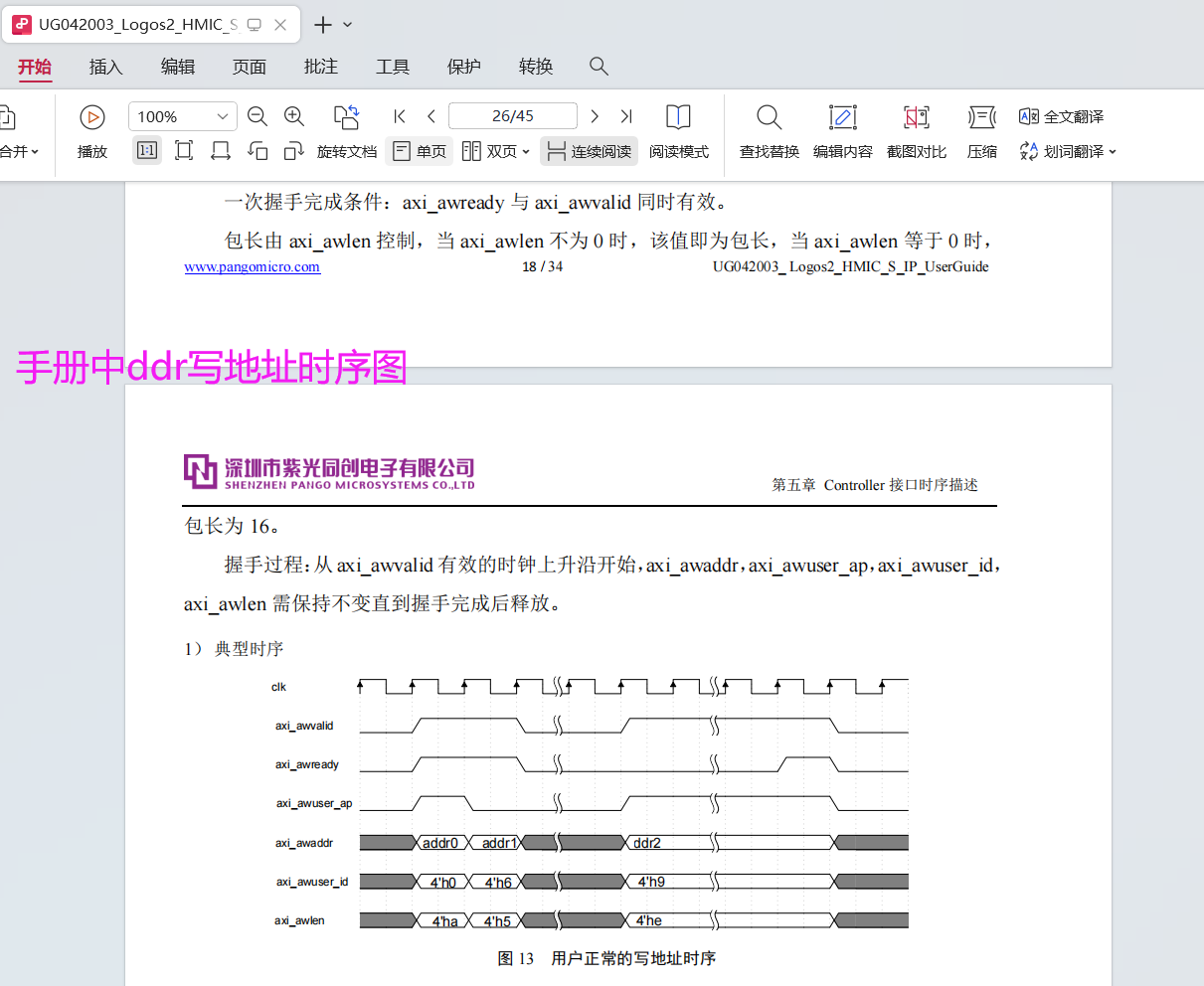

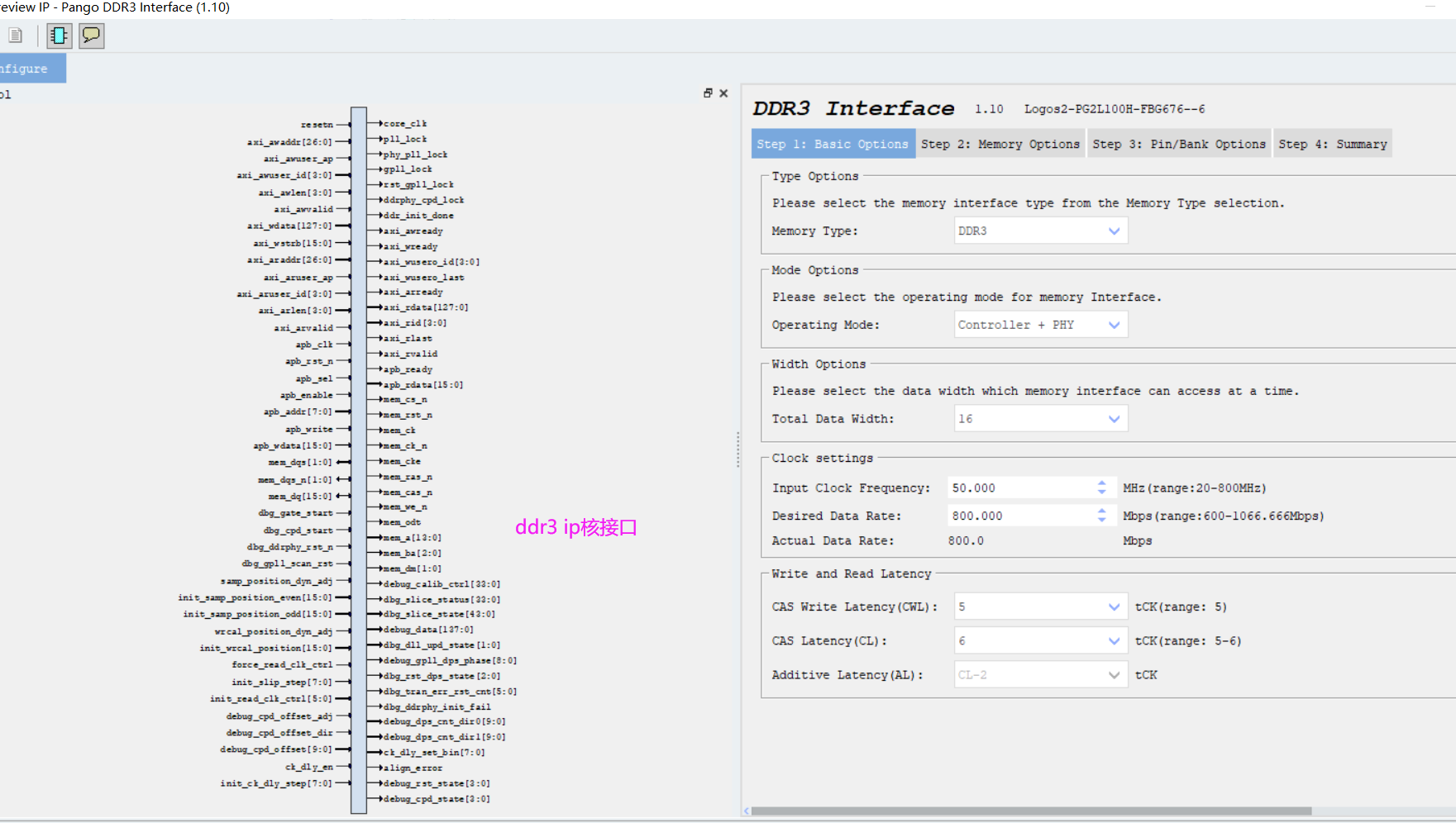

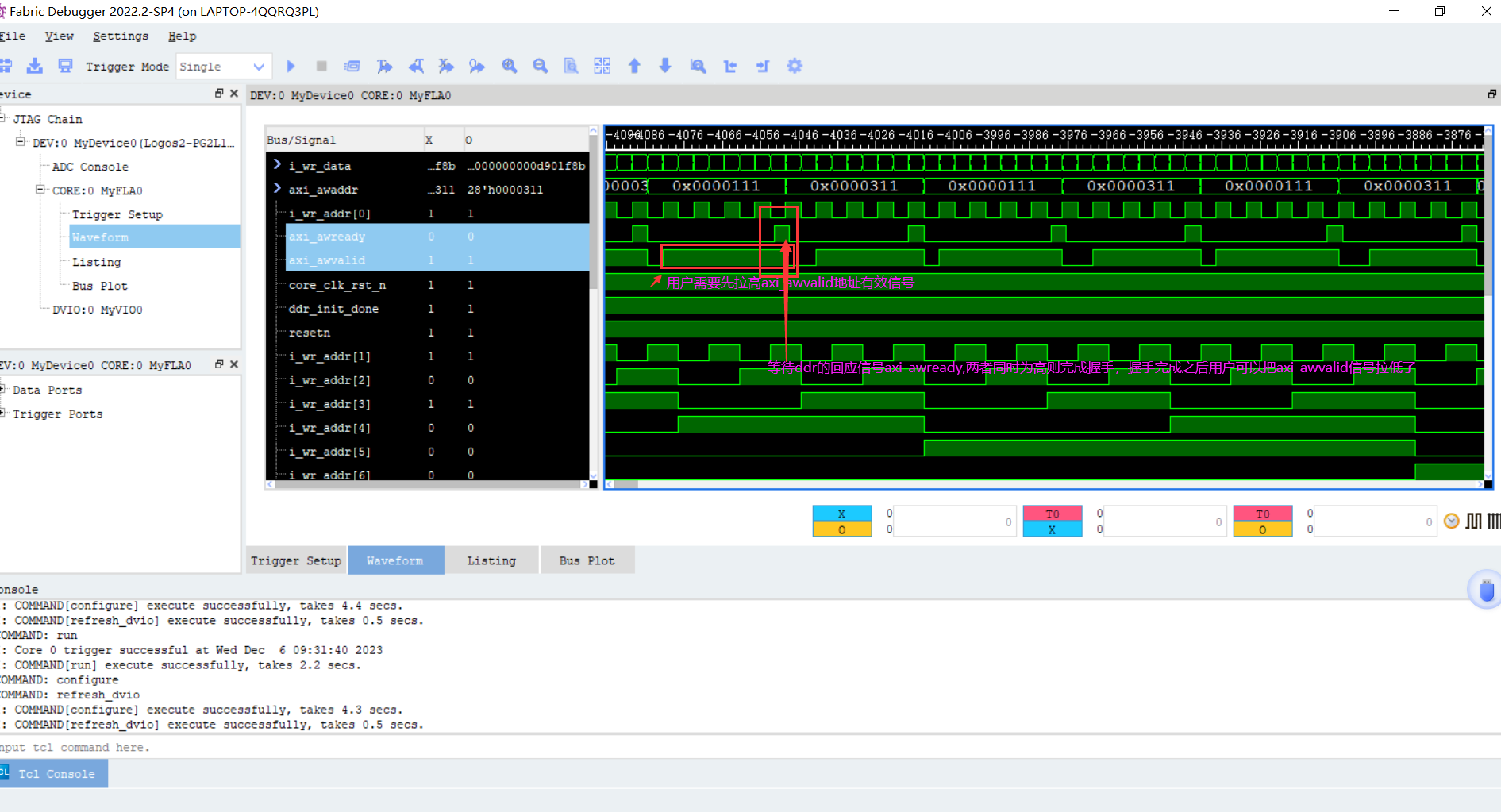

1、注意:对于写地址通道,axi_awvalid要一直拉高,axi_awready才会拉高。使用的芯片型号时PG2L100H-6FBG676,不同的型号IP核接口和axi的握手协议也不一样(一定要注意),这点要注意,这也给我挖了一个很大的坑,一把心酸一把泪啊。下图是上板之后通过debug和jtag_hub IP核抓取的信号

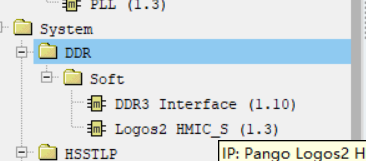

与芯片匹配的IP核:

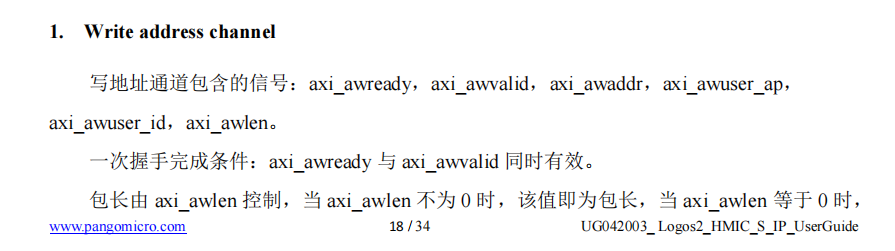

2、写地址握手的过程,代码解析

用户需要一直拉高axi_awvalid地址有效信号,直至ddr返还axi_awready信号,两者同时为高完成握手信号,完成握手之后用户 就可以把axi_awvalid信后拉低,为下次握手做好准备。下面代码就是握手的过程

8'd1:begin//先拉高axi_awvalid信号,然后 等待axi_awready信号

axi_awuser_ap <= 'b0;

axi_awvalid <= 1;

if(axi_awvalid & axi_awready)//握手信号

begin

axi_awvalid <= 1'b0;//完成握手用户拉低axi_awvalid信号,为下次握手做好准备

axi_awaddr<=28'h0000111;//握手成功就写入首地址,

axi_awid<=8'h01;

axi_awlen<=8'd120;//实际长度为 axi_awlen+1

state<=8'd2;

end

else//等待写地址握手成功

begin

state<=8'd1;

end

end

这段代码是用状态机的方式对ddr循环写地址,只有两个状态,状态1写入地址0x0000111,状态2写入地址0x0000311,对应上面图的

reg [7:0] cnt /* synthesis syn_keep = 1 */;// synthesis syn_keep = 1 防止信号被优化的语句

//reg [256-1:0] rd_data /* synthesis syn_keep = 1 */;

reg rd_valid /* synthesis syn_keep = 1 */;

always @(posedge axi_clk or negedge rst_n)

begin

if (!rst_n)

begin

state<=8'd0;

axi_awvalid<=1'b0;

//axi_wvalid<=1'b0;

axi_arvalid<=1'b0;

axi_wdata<=256'b0;

axi_aruser_ap <= 1'b0;

axi_awuser_ap <= 1'b0;

wr_wlast<=1'b0;

end

else

begin

case(state)

8'd0:begin//空闲状态

if(ddr_init_done==1'b1 && test_start==1'b0)

state<=8'd1;

else

state<=8'd0;

axi_awvalid<=1'b0;

axi_arvalid<=1'b0;

axi_wdata<=256'b0;

end

8'd1:begin//先拉高axi_awvalid信号,然后 等待axi_awready信号

axi_awuser_ap <= 'b0;

axi_awvalid <= 1;//这里注意,一定要先拉高axi_awvalid这个信号,否则ddr3 IP不会返还这个axi_awready信号。axi_awready没有被拉高的原因就在这里

axi_awaddr<=28'h0000111;//握手成功就写入首地址,

axi_awid<=4'h1;

axi_awlen<=4'd12;//实际长度为 axi_awlen+1,只能有4bit,axi_awlen[3:0]

if(axi_awvalid & axi_awready)//握手信号

begin

axi_awvalid <= 1'b0;//完成握手用户拉低axi_awvalid信号,为下次握手做好准备

state<=8'd2;

end

else//等待写地址握手成功

begin

state<=8'd1;

end

end

8'd2:begin//先拉高axi_awvalid信号,然后 等待axi_awready信号

axi_awuser_ap <= 'b0;

axi_awvalid <= 1;

axi_awaddr<=28'h0000311;//握手成功就写入首地址,

axi_awid<=4'h1;

axi_awlen<=4'd12;//实际长度为 axi_awlen+1

if(axi_awvalid & axi_awready)//握手信号

begin

axi_awvalid <= 1'b0;//0

state<=8'd0;

end

else//等待写地址握手成功

begin

state<=8'd2;

end

end

3、读ddr时,ddr的位宽在配置ip时设置为32,axi总线的宽度为256,256 /32=8,所以读ddr时每读一个数据地址就要偏移8,否则从ddr3中读出来的数据是不对的。

8'd6:begin//写读ddr地址

axi_arvalid<=1'b1;

axi_araddr<=axi_araddr + 'd8;//地址偏移8,否则读出来的数据是不对的

axi_arid<= axi_arid + 4'h1;

axi_arlen<=4'd4;//实际长度为 axi_awlen+1

axi_aruser_ap <= 1'b0;

if(axi_arvalid & axi_arready)

begin

axi_arvalid<=1'b0;

state<=8'd7;

end

else

begin

//axi_arvalid<=1'b0;

state<=8'd6;

end

end

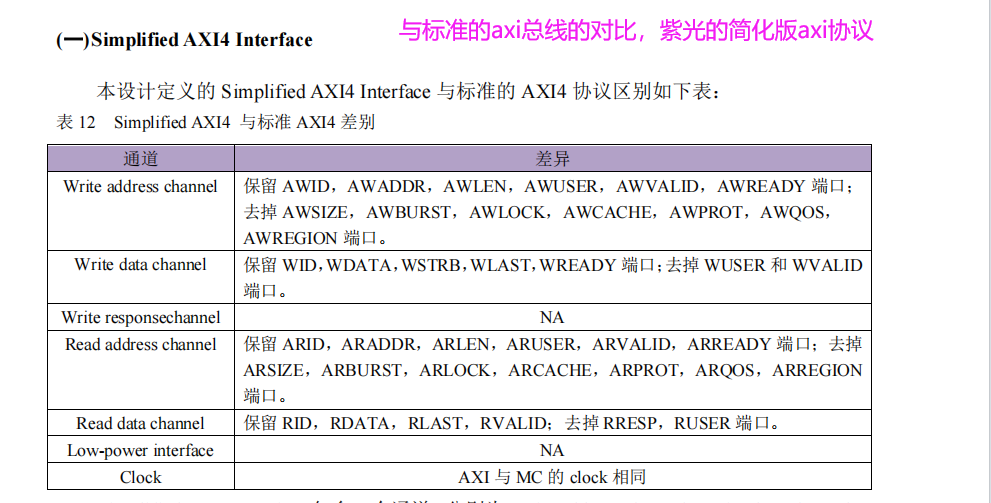

紫光使用的axi4协议是简化版的协议,跟标准的不一样,一定要注意。不同的FPGA芯片型号ddr3的ip核也不一样,axi握手时序也不一样,需要仔细阅读文档。

---晓凡 2023年12月17日于武汉书

文章来源:https://blog.csdn.net/xzs520xzs/article/details/135051468

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!