计算机组成原理——存储器21-40

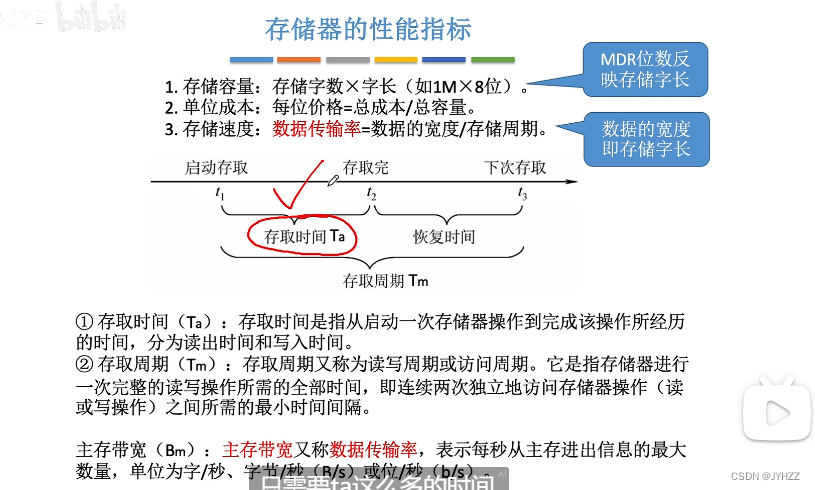

21、存储器存取周期是指(C)

A、存储器的读出时间

B、存储器的写入时间

C、存储器进行连续读或写操作所允许的最短时间间隔

D、存储器进行一次读或写操作所需的平均时间

存取周期是存储器进行连续读或写操作所允许的最短时间间隔

存取时间是存储器进行一次读或写操作所需的平均时间

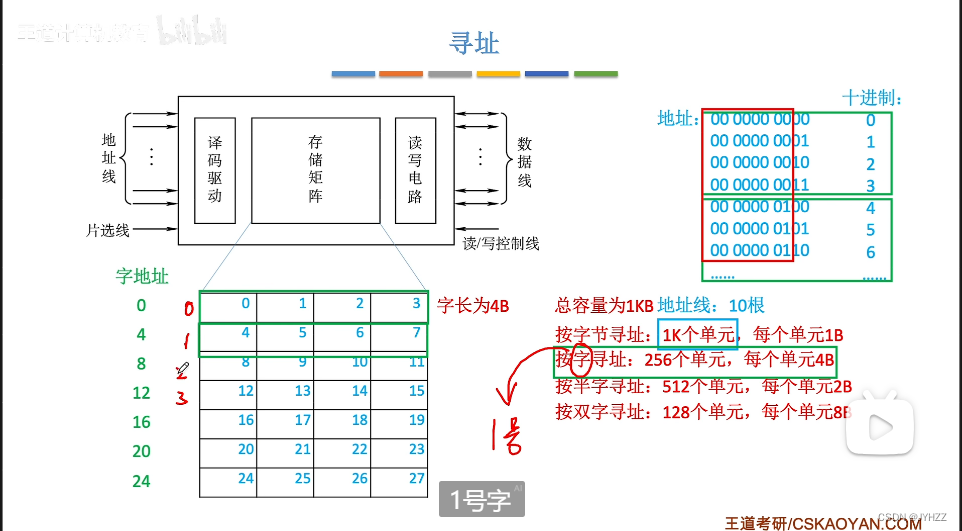

22、设机器字长为32位,一个容量为16MB的存储器,CPU按半字寻址,其可寻址的单元数是(B)

A、2^24

B、2^23

C、2^22

D、2^21

16MB=2^24B

字长=32b=4B=2^2B

按半字寻址,一个地址单元占半个字长,即16b=2B

所以可寻址单元=2^24B/2B=2^23

23、设机器字长为64位,存储容量为128MB,若按字编址,它可寻址的单元个数是(B)

A、16MB

B、16M

C、32M

D、32MB

字长=64b=8B=2^3B

128MB=2^27B

可寻址单元个数=2^27B/2^3B=2^24B=16M(不是16MB)

24、在多级存储体系中,“Cache-主存”结构的作用是解决(D)问题

A、主存容量不足

B、主存与辅存速度不匹配

C、辅存与CPU速度不匹配

D、主存与CPU速度不匹配

“Cache-主存”结构,拥有Cache的速度和主存的容量,而Cache只能与主存和CPU进行相应的存取操作,不能直接与辅存进行操作,因此“Cache-主存”结构与辅存无关,利用该结构可以将主存的速度提高,因此是解决主存与CPU速度不匹配的问题。

25、下列关于多级存储系统说法中正确的是(A)

a.多级存储系统是为了降低存储成本

b.虚拟存储器中主存和辅存之间的数据调动对任何程序员是透明的

c.CPU只能与Cache直接交换信息,CPU与主存交换信息也需要经过Cache

A、仅a

B、仅a和b

C、a、b和c

D、仅b

多级存储系统是将一些常用的数据放在离CPU近的地方,不常用的放在外存/辅存中,这样既可以保证计算机的运行效率,又可以使得尽可能便宜的扩大存储容量,降低了存储成本。

虚拟存储器中主存和辅存之间的数据调动是通过操作系统的相关指令来实现的,只对应用程序员透明。其他的程序员需要操控数据调用,因此不能透明。

CPU可以和Cache以及内存直接进行交换信息。

26、某一SRAM芯片,其容量为1024*8位,除电源和接地端外,该芯片的引脚的最小数目为(A)

A、21

B、22

C、23

D、24

解析:选A

容量为1024*8位,因此数据线为8根,地址线为10根(1024=2^10),除了电源和接地线,还需要片选线(1根),读写数据线(可以合用1根,可以读写分开用2根)。因此最小数目为10+8+1+1=20根,但题目中没有20的选项,因此采用读写数据线分开,即10+8+1+2=21根。

?

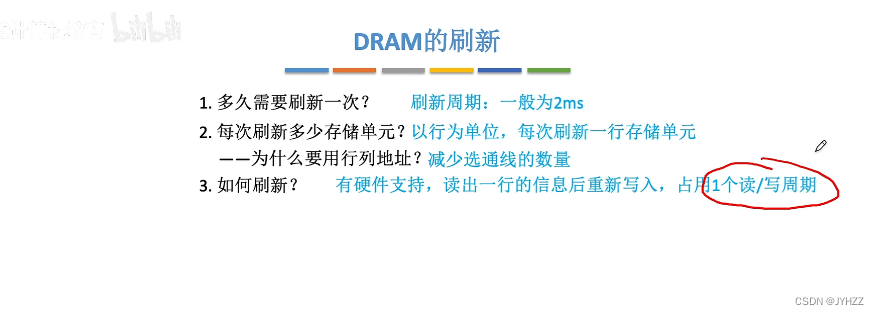

27、下列(C)是动态半导体存储器DRAM的特点

a.在工作中存储器内容会发生改变

b.每隔一段时间,需要根据原存内容重新写入一遍

c.一次完整的刷新过程需要占用两个存储周期

d.一次完整的刷新过程只需要占用一个存储周期

A、a、c

B、b、c

C、b、d

D、只有c

动态半导体存储器(DRAM),利用电容存储电荷的特性记录信息,由于电容会放电,电荷会流失,因此需要每隔一段时间,根据原存内容重新写入一遍,写入的内容不会发生改变。

动态半导体存储器的刷新是不经过CPU的,利用RAM内部自带的刷新放大器,将内容存入刷新放大器,需要一个存取周期,然后取出来的时候就不需要了,因为刷新放大器本身就在RAM上,并不需要访问其他的部件,因此只需要一个存取周期。

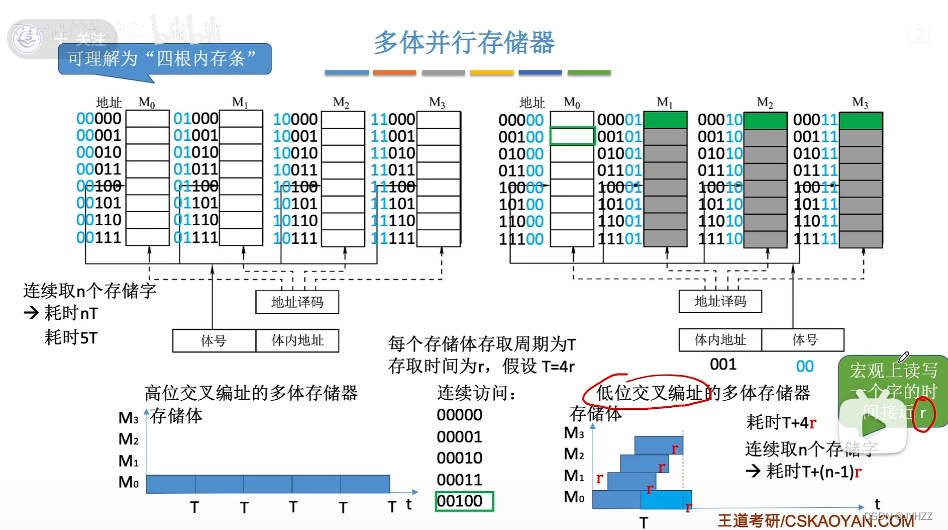

28、机器采用四体低位交叉存储器,现分别执行下述操作:①读取6个连续地址单元中存放的存储字,重复80次;②读取8个连续地址单元中存放的存储字,重复60次,则①、②所花费的时间之比()

A、1:1

B、2:1

C、4:3

D、3:4

设T为存取周期,r为存取时间。因为为四体低位交叉存储器,所以需要满足4>=T/r,设T=4r

对于1:读取1次6个连续单元需要2T,80次为160r

对于2:读取1次8个连续单元需要2T,60次为120r

3.2.4 双端口RAM和多模块存储器_哔哩哔哩_bilibili

29.下列说法中,正确的是(B)

a.高位多体交叉存储器能很好的满足程序的局部性原理

b.高位四体交叉存储器可能在一个存储周期内连续访问4个模块

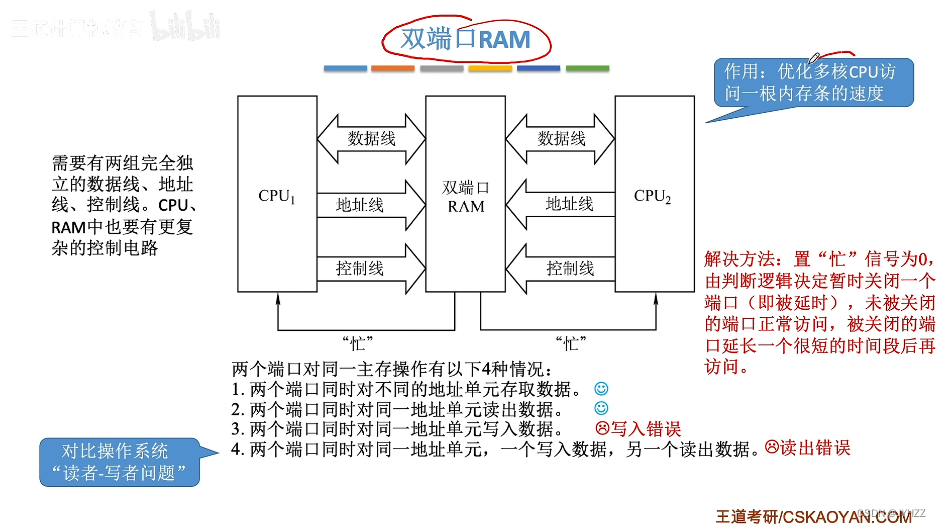

c.双端口存储器可以同时访问同一区间、同一单元

d.双端口存储器当两个端口的地址码相同时,必然会发生冲突

A、a、c

B、b、c

C、b、c和d

D、c、d

由于高位多体交叉存储器(或称连续编址存储器)在一个存储体内地址连续,所以一个程序的指令和数据极大可能只分布在一个存储体上,这样的只能顺序读取,而无法充分利用并行存取。(即一次并行取出来的指令或数据不在一个程序的局部上,跨度很大,可能是在一个程序的首尾,或不同的程序,也就不再满足局部性原理。(事实上,这里仅作解释使用,准确而言,高位多体交叉只能顺序存取),所以无法提高CPU访问存储器的速度。

而低位多体交叉(或称交叉编址存储器)将一个程序的指令、数据分散在不同存储体上,由于可以“并行”访问(流水线式),一次取出的指令或数据在一个程序段上,则CPU执行指令时无需反复的访问存储器取指,满足程序的局部性原理。

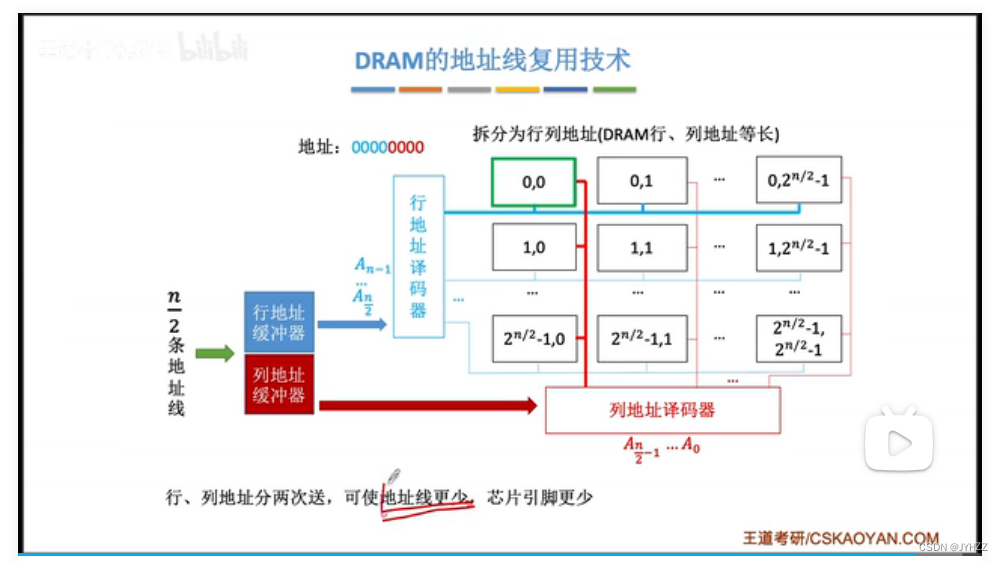

30、某容量为256MB的存储器由若干4M*8位的DRAM芯片构成,该DRAM芯片的地址引脚和数据引脚总数是(A)

A、19

B、22

C、30

D、36

4M =>2^22,因此需要22根地址线,因为DRAM采用地址复用技术,因此只需要原来地址线的一半,即地址信号分行、列两次发送,因此需要11根地址线。

8位,因此需要8根数据线

即11+8=19根

31、某计算机主存按字节编址,由4个64M*8位的DRAM芯片采用交叉编制方式构成,并与宽度为32位的存储器总线相连,主存每次最多读写32位数据。若double型变量x的主存地址为804001AH,则读取x需要的存储周期数是(C)

A、1

B、2

C、3

D、4?

double类型是64位,每次最多读写32位,如果不考虑恢复时间,则需要两个存储周期2T,但是每读完一次需要一定的恢复时间,因此需要的存储周期一定大于2,且恢复时间一般小于存储周期,因此2<=x<=4,因此选3个存储周期。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!