硅像素传感器文献调研(三)

写在前面:

引言:也是先总结前人的研究结果,重点论述其不足之处。

和该方向联系不大,但还是有值得学习的地方。逻辑很清晰,易读性很好。

1991年—场板+半阻层

使用场板和半电阻层的高压平面器件

0.摘要

提出了一种基于场板与氧化物上半阻层(SIPOS)结合使用的改进高压技术。场板和SIPOS具有互补的功能。场板的存在减少了结曲率电场效应。硅表面电势通过氧化物上的主要SIPOS层线性化,从而降低场板边缘处的峰值电场。第二高电阻率SIPOS层提供优异的钝化,并且还防止下层SIPOS膜的介电击穿。以下描述高压平面晶体管的完整制造、设计、电气特性和可靠性。

1.引言

在过去的25年中,已经使用了许多技术来提高高压和功率器件的电压处理能力,目的是实现平面结的接近理想的击穿[ 11]。一种利用半绝缘多晶硅(SIPOS)的薄膜技术首先由Matsushita [2]提出,以减少表面态效应并增加击穿电压。然而,直接在硅上沉积SIPOS常常引起表面污染,导致大的漏电流,再现性差,集电极电流-hFE特性的退化,和dV/dt敏感性。相反,如果SIPOS层沉积在氧化物缓冲层上,则这些问题被绕过[3]。不幸的是,SIPOS膜的介电击穿和离子污染物(主要是钠离子)迫使在SIPOS上方使用钝化层,因此增加了工艺复杂性。当使用CVD(化学气相沉积)-SiO2膜时尤其如此,从而需要额外的技术。我们选择利用第二高电阻率SIPOS膜作为钝化层,从而大大简化了平面工艺[4]。这种拓扑结构已被应用于设计和制造1000至1500 V范围内的高压平面双极晶体管,能够取代梅萨技术中的等效器件[5]。与以前的工作[2]和[3]相比,在此提出的技术中,我们没有注意到集电极电流-hFE特性的任何退化。此外,实现了非常好的可靠性。

2.技术

图1 基本的SIPOS工艺

SIPOS的基本流程如图1所示。起始硅晶片是(111)磷掺杂的,具有60 Ω cm(1000-V器件)和75 Ω cm(1500-V器件)的电阻率。首先,切割用于p基极扩散的开口(步骤(a))。接下来,切割用于n+发射极和截止沟道的窗口(步骤(B))。集电极基极结为14 μ m,最终场氧化层厚度为1.25 μ m。然后在相同的反应器运行中通过LPCVD(低压CVD)在氧化物上沉积两个SIPOS层(步骤(c))。这通过在反应器运行期间将一氧化二氮与硅烷的比率从0.12调节至0.30来实现。然后沿着氧化物缓冲层蚀刻SIPOS层(步骤(d))。最后,在整个表面上沉积铝并蚀刻(步骤(e))。由此产生的工艺具有与没有SIPOS的标准中压端接相同数量的掩膜步骤。相比之下MESA高压终端需要两个额外的掩膜步骤。工艺复杂度尽可能低。

该提出的工艺允许获得电阻率为2.5 × 10 7Ωcm的第一SIPOS层(12%氧),其通过场板效应在硅中扩展等势线,随后是较高电阻率的第二SIPOS层(30%氧),其防止第一SIPOS膜的介电击穿和任何离子污染。图2示出了两个SIPOS层的典型样品的SIMS分析(对于该研究,SIPOS沉积直接在Si(111)衬底上进行)。SIMS信号揭示了两种SIPOS膜,每一种都具有均匀的组成(该图中使用的任意单位不能与氧原子浓度直接相关)。

图2 一个典型样品的SIMS分析

3.SIPOS影响

所提出的平面双极器件如图1所示(步骤(e))。场板技术增加了扩散结的曲率半径,SIPOS层避免了场板边缘附近的常见电场拥挤效应[6]。实际上,第一SIPOS膜使场板边缘与停止沟道接触件之间的电势线性化,并且第二SIPOS膜防止湿气和电弧现象。因此,场板边缘处的电场减小,并且电压处理能力显著提高。

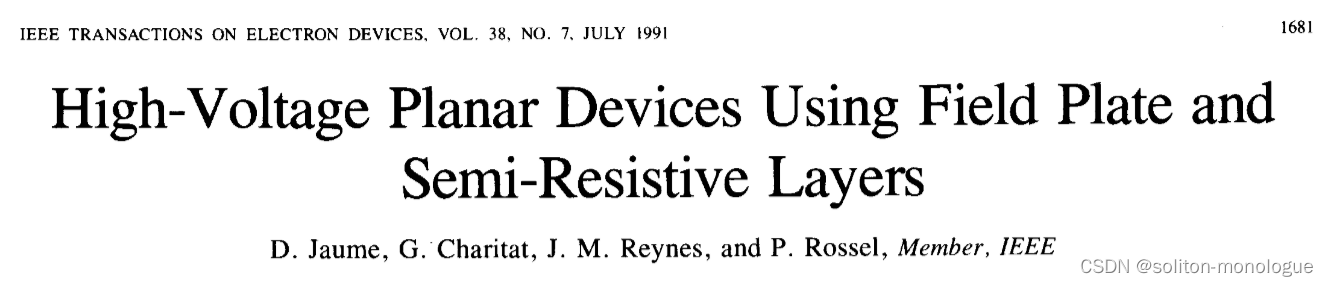

场板和SIPOS层的互补功能可以使用二维模拟器BIDIM2 [7]来显示,该模拟器是为高压和功率器件开发的。该软件可求解半导体的三个基本方程,但关态研究除外,在关态研究期间,仅求解泊松方程。雪崩诱导击穿定义为电子和空穴的电离积分等于1 [8]。我们选择利用Van Overstraeten和De Man [9]电离系数。沿着从最高场点开始并沿两个方向上的势梯度线的路径沿着执行积分。关键器件区域(结、触点末端等)由BIDIM2单独检查。SIPOS效应是用场板边缘和光阑之间的氧化物表面上的简单线性电势分布来模拟的。这种简化的假设是基于Tarng的模型[IO],该模型预测SIPOS膜中横向导电的低场区域中的欧姆行为。图3显示了基极-集电极结的反向电压-电流特性,在低电压范围内具有预测的欧姆行为。

图4给出了SIPOS效应的一个例子,其中硅表面电场的计算值与从基底到截止沟道触点的距离,有SIPOS层和没有SIPOS层。所施加的偏压为630 V,这对应于没有SIPOS的器件的雪崩击穿。场板端部附近的峰值电场是场板终端技术的主要缺点,通过SIPOS线性化效应,场板端部附近的峰值电场从310(无SIPOS)kV/cm降低到160(有SIPOS)kV/cm。

4.结果

A、电压处理能力

对于图1(步骤(e))中描绘的所提出的结构,我们已经用2-D数值模拟和实验装置研究了临界物理和几何参数对电压处理能力的影响。实验结果与理论计算结果吻合较好。

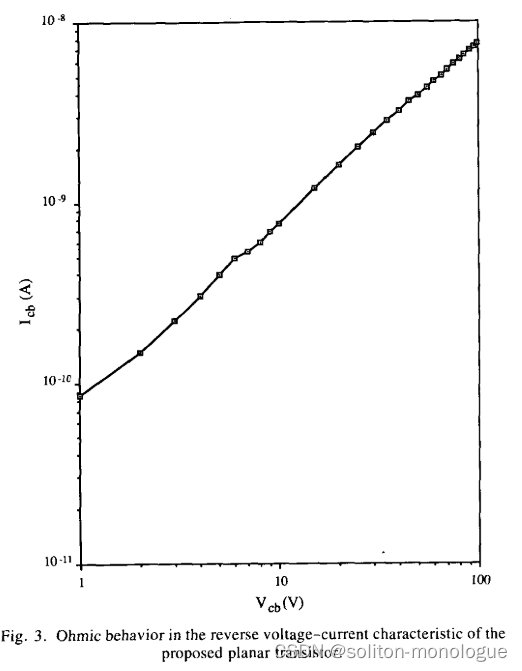

图5示出了在其他临界参数保持恒定的情况下,两种电阻率衬底的击穿电压(BVcho)对场板-停止沟道距离(Δ?L)的依赖性。可以看出,ΔL必须足够大以允许电位的扩展,使得SIPOS层施加的线性化效应将起作用。实际上,当ΔL从60 μ m(1000 V Bidim 2)增加到100 μ m(参考模拟结果)或从60 μ m(1500 V Bidim 2)增加到150 μ m(参考模拟结果)时,场板边缘处的电场松弛,从而将击穿位置从场板边缘移动到结曲率,导致击穿电压增加。对于1000-V器件大于100 μ m的ΔL值和1500-V器件大于200 μ m的ΔL值,击穿电压相对恒定。

B、开态电学特性

之前的作者(21,[3])已经观察到集电极电流-hFE特性的一些退化。这些退化已被归因于基极-发射极结的漏电流的增加,但是通过热氧化物内的磷的吸杂改善了hFE特性。图6显示了Gummel图[12],其提取的非理想因子m为1.015。该接近理想的m值是由于SIPOS沉积覆盖来自基极和发射极扩散的氧化物的事实。因此,热氧化物的吸杂效应是守恒的。

该值非常接近Cerofolini和Polignano在p-n二极管上给出的理想结的极限1.012 [ 131]。它可以有利地与1.05的梅萨工艺结值相比较。

C、dV/dt敏感性

文献[14]表明SIPOS会导致开关性能的一些不稳定性;特别是动态击穿电压可能低于直流条件下的击穿电压。我们已经成功地在集电极和发射极之间的所有器件上应用了7500 V/ps的dV/dt击穿,在电感电路的帮助下,击穿电压没有任何降低。我们没有观察到dV/dt限制,因为SIPOS沉积在足够厚度(1.25 μ m)的氧化物上以避免大的表面电容,并且第二SIPOS层的电阻率与CVD膜相比没有那么高。

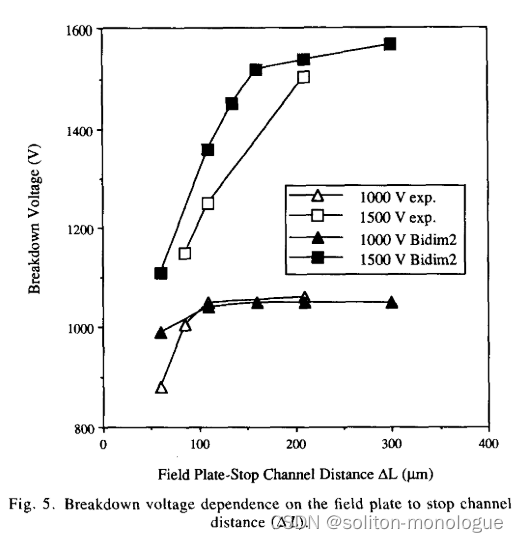

D、可靠性

所提出的结构已通过所有标准的可靠性测试,如温度循环,压力锅,高温,反向偏置(HTRB)。图7显示了1000-V和1500-V器件的HTRB/1500 C结果。对于1000 V器件,BV,= 1015 V,V,,= 5 V,I,= 10 mA;对于1500 V器件,SV,= 1500 V,V,,= 5 V,I,= 50 mA时,I,和HFE特性在168、500和1000 h时稳定。因此,可以认为所提出的装置非常可靠。

5.总结

?场板和SIPOS作为结端接技术的互补功能是这种设计理念高效率的关键。场板减小了扩散结曲率处的电场,SIPOS减小了场板边缘的电场。由于高电阻率SIPOS提供了极佳的钝化,因此两层SIPOS的沉积可以在一次反应器运行中完成。此外,与标准的台面终端相比,芯片面积节省了约20%。与其他器件端接技术相比,这是一个非常好的结果,而不会对面积、动态性能或成品率造成任何影响。此外,接近的设计规则可以应用于高压MOS器件,从而改善RON、RBSOA和开关。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!