【紫光同创国产FPGA教程】——(PGL22G第二章)键控流水灯实验例程

本原创教程由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处(www.meyesemi.com)

适用于板卡型号:

紫光同创PGL22G开发平台(盘古EU 22K)

一:盘古EU 22K开发板简介

盘古EU 22K开发板共有11个翠绿LED灯,其中1个是电源指示灯(POWER);2个是FPGA的运行状态指示灯:INIT和DONE;有8个用户LED灯(LED1~8),FPGA输出高电平时对应的LED灯亮灯(详情请查看“MES22GP开发板硬件使用手册”)。

二:实验目的

由 USER_KEY1 按键输入,切换 USER_LED1~ USER_LED8 的输出效果。

三:实验原理

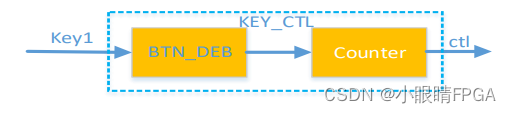

实现框架如下:

(1)顶层实现按键切换 LED 的流水灯状态;

(2)需要设计一个输入控制模块及一个输出控制模块; 这个实验带大家将多个模块整合成为一个工程,涉及到的知识点有子模块设计、模块例化; 子模块的设计主要是依据功能定位,确定输入输出,再做具体的设计;

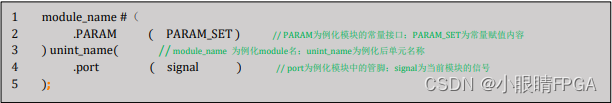

模块例化方式如下:?

按键控制模块功能 ?

接收按键输入信号。统计按键按下次数,由于流水灯模式是 3 种,计数统计范围是 0~2循环,将计数结果传递给 LED 控制模块;

根据需求输入信号有:时钟,按键;输出信号有:流水灯控制信号;

内部功能处理:

<1>内部需要对按键信号做消抖处理;

<2>按键触发计数器(计数值输出)改变继而调整流水灯的状态;

按键消抖模块 ?

前后抖动时间约为 5~10ms,取按键抖动区间开始标识,持续 10-20ms 后标识归零,在抖 动区间内输出保持,非消抖区间,按键状态输出。

LED 控制模块功能?

3 种流水灯模式有按键传递过来的计数控制切换,每一个 LED 的显示状态完整后进入下一 模式初始化。根据需求可得到如下信息:

输入信号:时钟,流水灯模式控制信号; 出信号:8bit 位宽的 LED 控制信号;

功能处理注意事项:流水灯状态切换点,不同状态的切换时如何初始化;

四:实验源码设计? ?

顶层文件源码 ? ? ? ? ? ? ? ? ??

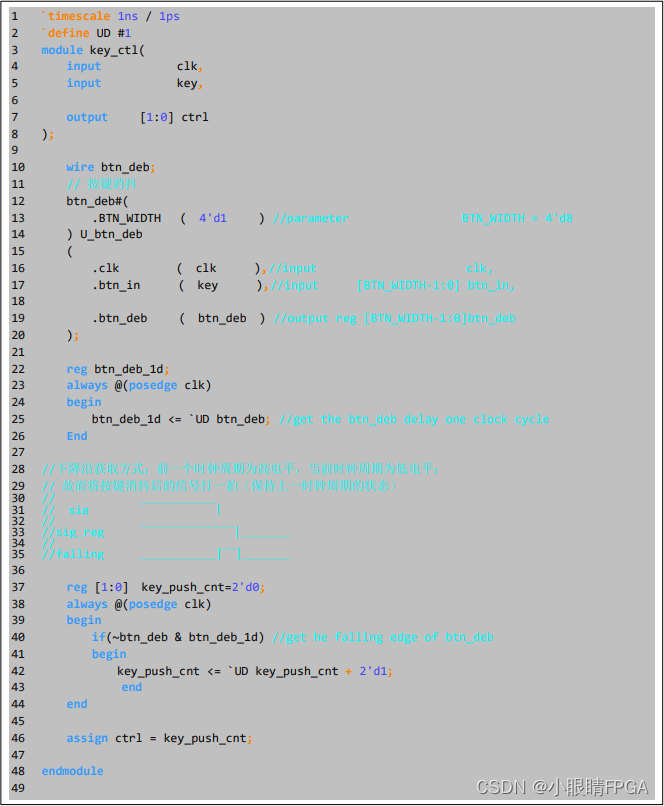

按键控制模块

按键消抖模块?

?Verilog 中的 generate 语句常用于编写可配置的、可综合的 RTL 的设计结构。它可用于 创建模块的多个实例化,或者有条件的实例化代码块。

我们常用 generate 语句做三件事情。一个是用来构造循环结构,用来多次实例化某个模 块。一个是构造条件 generate 结构,用来在多个块之间最多选择一个代码块,条件 generate 结构包含 if--generate 结构和 case--generate 形式。还有一个是用来断言。

在 Verilog 中,generate 在建模(elaboration)阶段实施,出现预处理之后,正式模拟 仿真之前。因此。generate 结构中的所有表达式都必须是常量表达式,并在建模(elaboration) 时确定。例如,generate 结构可能受参数值的影响,但不受动态变量的影响。

Verilog 中的 generate 块创建了新的作用域和新的层次结构,就像实例化模块一样。因 此在尝试对 generate 块中的信号进行引用时,很容易因此混乱,因此请记住这一点。

L E D 控 制 模 块

?

?

五:实验现象

每按下一次 KEY1,LED 灯状态切换一次,总共三种 LED 模式供循环切换;

LED 模式一:从高位到低位的 LED 流水灯;

LED 模式二:隔一亮一交替点亮;

LED 模式三:从高位到低位暗灯流水;

?

?

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!