什么是DMAC?

About the DMAC

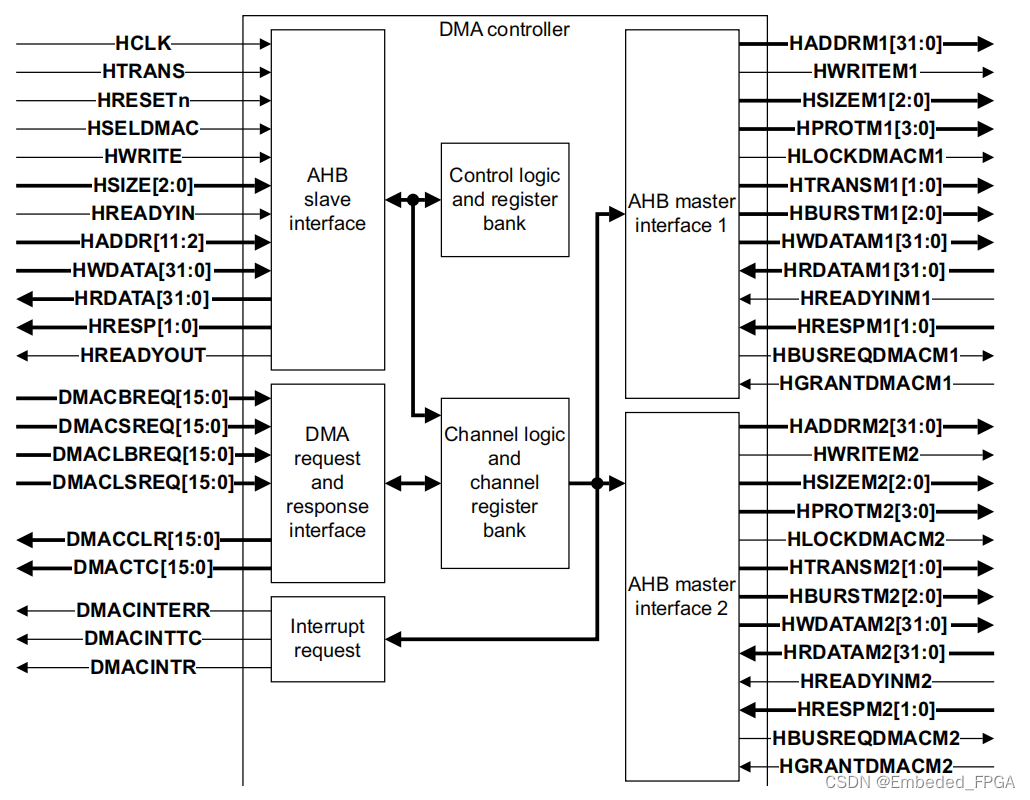

The DMAC is an Advanced Microcontroller Bus Architecture (AMBA) compliant System-on-Chip (SoC) peripheral that is developed, tested, and licensed by ARM Limited.

The DMAC is an AMBA AHB module, and connects to the Advanced

High-performance Bus (AHB).

Features of the DMAC

The DMAC offers:

? Compliance to the AMBA Specification for easy integration into SoC

implementation.

? Eight DMA channels. Each channel can support a unidirectional transfer.

? 16 DMA requests. The DMAC provides 16 peripheral DMA request lines.

? Single DMA and burst DMA request signals. Each peripheral connected to the

DMAC can assert either a burst DMA request or a single DMA request. You set the DMA burst size by programming the DMAC.

? Memory-to-memory, memory-to-peripheral, peripheral-to-memory, and

peripheral-to-peripheral transfers.

? Scatter or gather DMA support through the use of linked lists.

? Hardware DMA channel priority. Each DMA channel has a specific hardware priority. DMA channel 0 has the highest priority and channel 7 has the lowest priority. If requests from two channels become active at the same time, the channel with the highest priority is serviced first.

? AHB slave DMA programming interface. You program the DMAC by writing to the DMA control registers over the AHB slave interface.

? Two AHB bus masters for transferring data. Use these interfaces to transfer data when a DMA request goes active.

? 32-bit AHB master bus width.

? Incrementing or non-incrementing addressing for source and destination.

? Programmable DMA burst size. You can programme the DMA burst size to transfer data more efficiently. The burst size is usually set to half the size of the FIFO in the peripheral.

? Internal four word FIFO per channel.

? Supports eight, 16, and 32-bit wide transactions.

? Big-endian and little-endian support. The DMAC defaults to little-endian mode on reset.

? Separate and combined DMA error and DMA count interrupt requests. You can generate an interrupt to the processor on a DMA error or when a DMA count has reached 0. This is usually used to indicate that a transfer has finished. There are three interrupt request signals to do this:

— DMACINTTC signals when a transfer has completed.

— DMACINTERR signals when an error has occurred.

— DMACINTR combines both the DMACINTTC and DMACINTERR

interrupt request signals. You can use the DMACINTR interrupt request in systems that have few interrupt controller request inputs.

? Interrupt masking. You can mask the DMA error and DMA terminal count interrupt requests.

? Raw interrupt status. You can read the DMA error and DMA count raw interrupt status prior to masking.

? Test registers for use in block and integration system level testing.

? Identification registers that uniquely identify the DMAC. An operating system can use these to automatically configure itself.

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!