嵌入式工具 之三 详解 RAM、ROM、FLASH、MMC、SD 等存储器

存储器

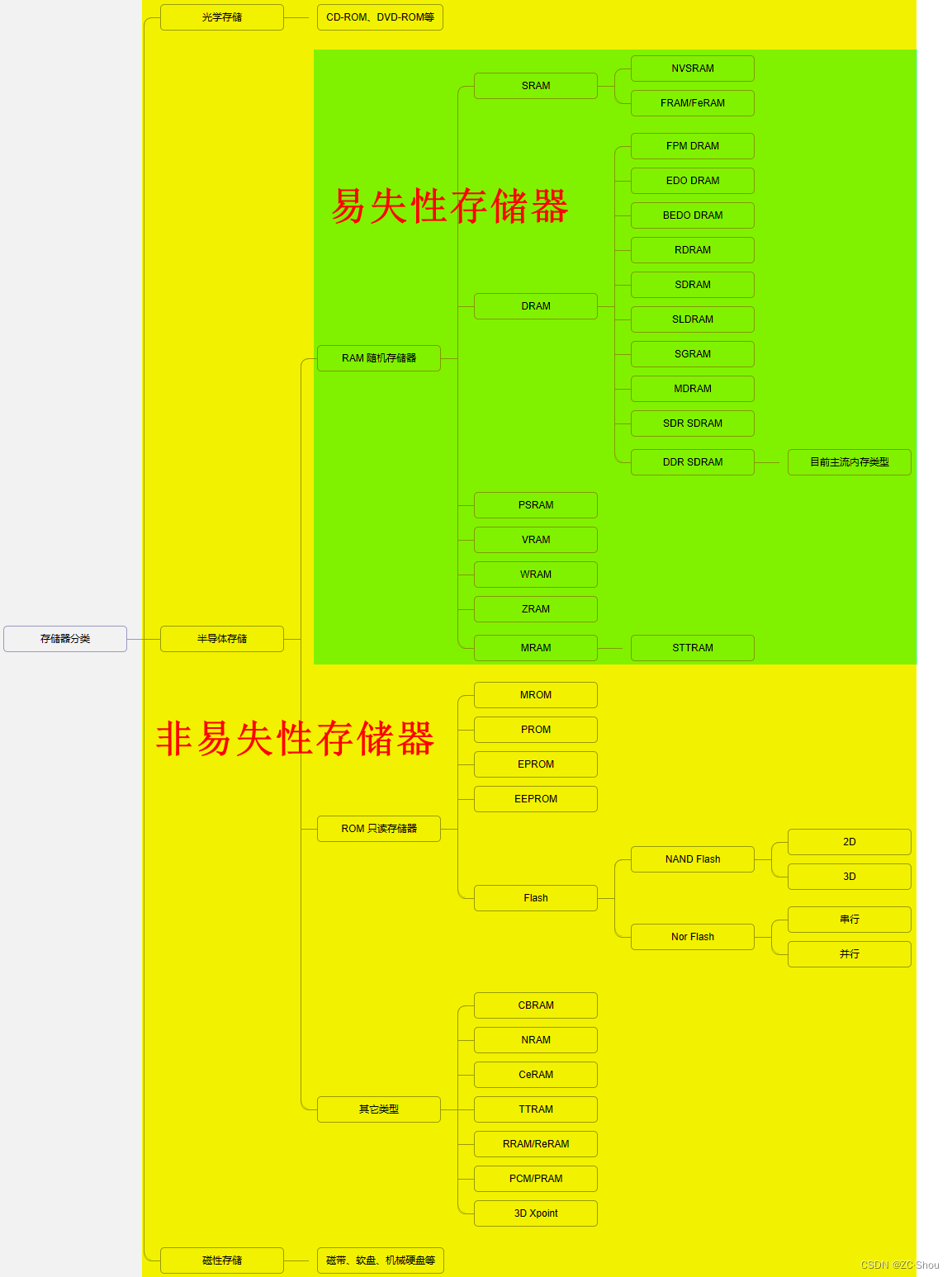

??存储器是电子系统中必不可少的存储设备,主要用于存放程序(指令)和数据。存储器分类有很多方法,下图是一个按照存储介质的不同的分类示意图(绿色是易失性存储器,黄色是非易失性存储器):

MOS 晶体管

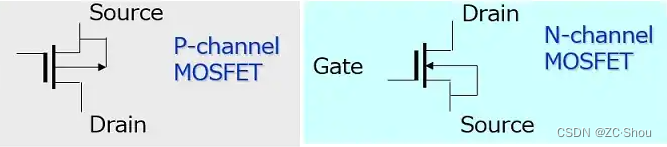

??1959 年,贝尔实验室的 Mohamed M. Atalla 和 Dawon Kahng 发明了 MOSFET(Metal–Oxide–Semiconductor Field-effect Transistor,金属氧化物半导体场效应晶体管),也称为 MOS 晶体管。最初有两种类型的 MOSFET 制造工艺,PMOS(p 型 MOS)和NMOS(n 型 MOS)。

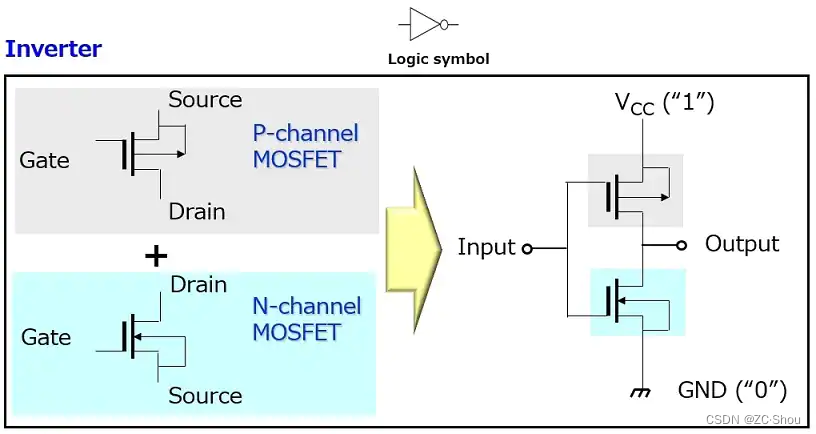

??互补金属氧化物半导体(Complementary Metal–Oxide–Semiconductor,CMOS)是一种金属氧化物半导体场效应晶体管(MOSFET)制造工艺,它是结合了 PMOS 和 NMOS 工艺的新型 MOSFET 逻辑。

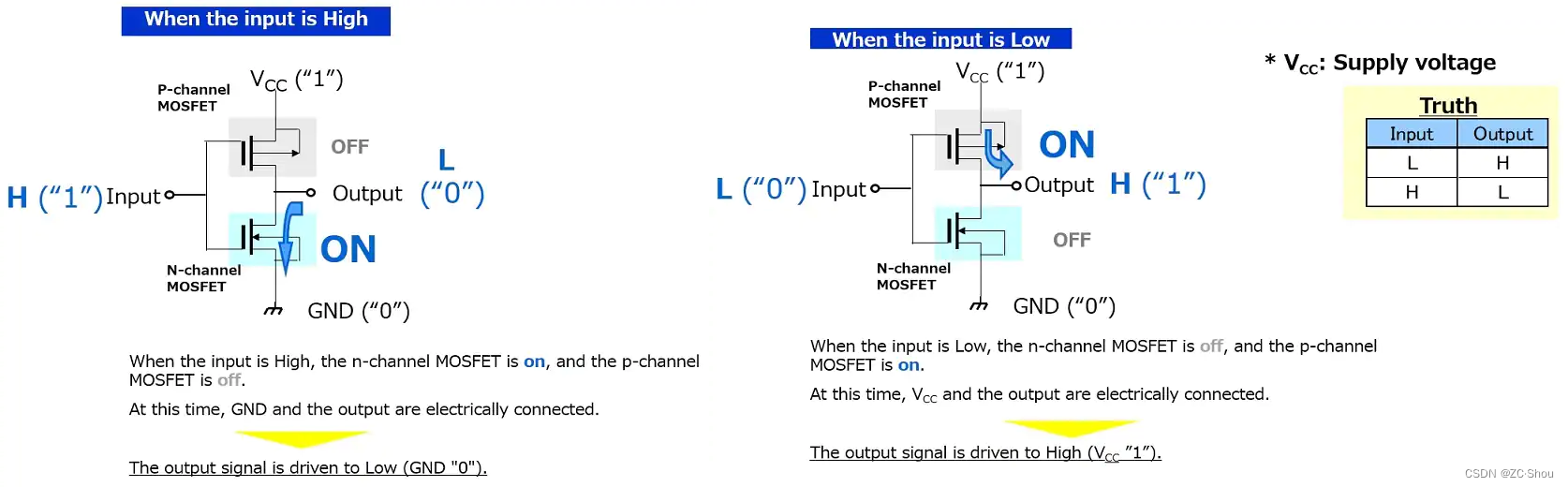

CMOS 逆变器的工作原理:

RAM

??随机存取存储器(Random Access Memory,RAM)是存储单元的内容可按照需要随机取出或存入,且存取的速度与存储单元的位置无关(内存中的每个存储位置都与其他位置一样容易到达,并且花费相同的时间)的一类存储器的总称。这种存储器在断电时,将丢失其存储内容,但得益于其速度快,常和 CPU 一起工作。

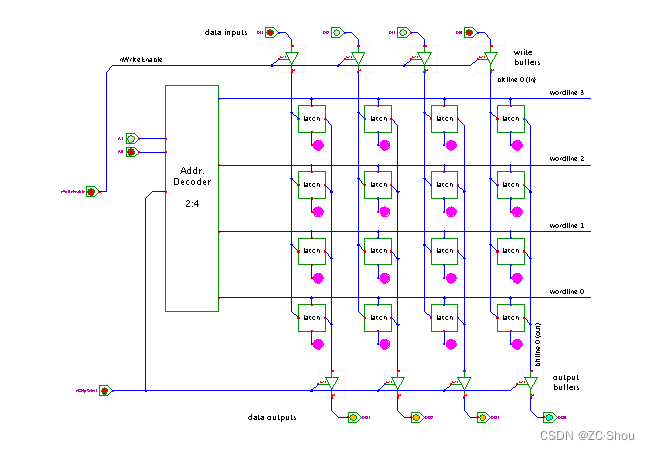

??在当今的技术中,随机存取存储器通常是采用集成电路(IC)芯片和 MOS(金属氧化物半导体)存储单元的形式。RAM 中包含多路复用和解复用电路,用于将数据线连接到寻址存储以读取或写入条目。

- 第一代 RAM 是 1947 年开始的威廉姆斯管,它将数据存储为阴极射线管表面的带电点

- 第二代则是 1947 年发明的磁芯存储器 ,通过改变每个环的磁化感,可以存储每个环一个位的数据。

- 第三代则是采用集成电路(IC)芯片和 MOS(金属氧化物半导体)半导体存储

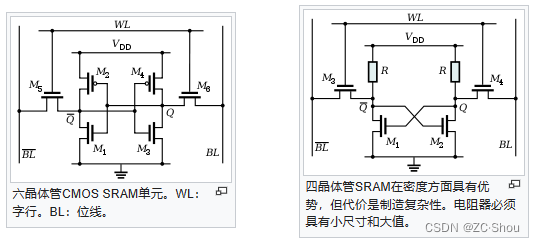

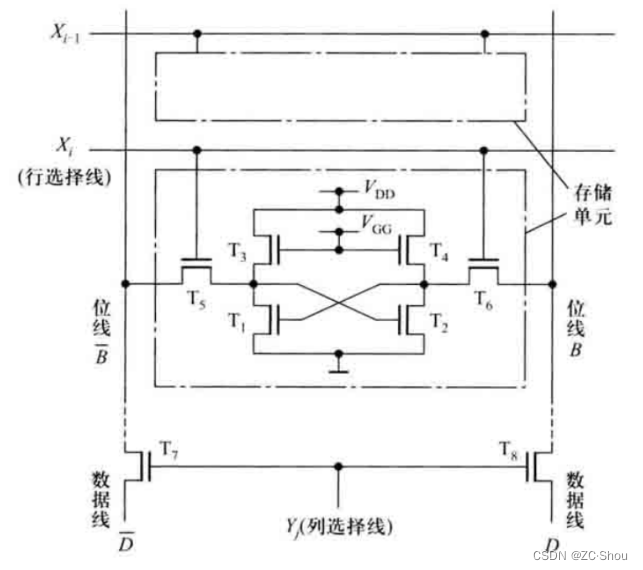

SRAM

??静态随机存取存储器(Static Random-Access Memory,SRAM)通常使用六个 MOS 晶体管存储器组成的单元(简称为 6T SRAM 单元)组成(没有电容器)。四晶体管 SRAM 在独立的 SRAM 器件中也很常见。

??单元中的每个位都存储在四个晶体管(M1,M2,M3,M4)上,形成两个交叉耦合逆变器。该存储单元具有两个稳定状态,用于表示 0 和 1,两个额外的接入晶体管用于在读写操作期间控制对存储单元的访问。晶体管不需要电源来防止泄漏,因此,SRAM 将在有电源的情况下永久保存其数据。

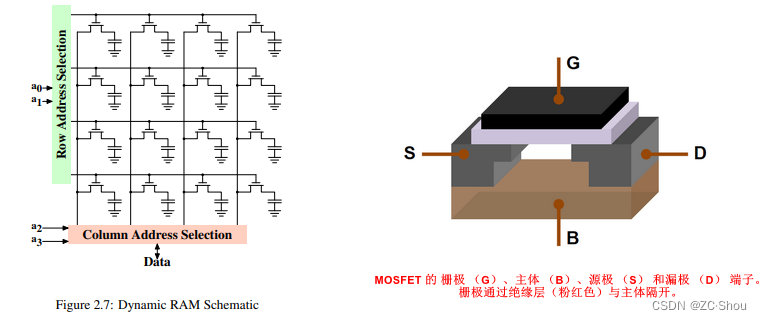

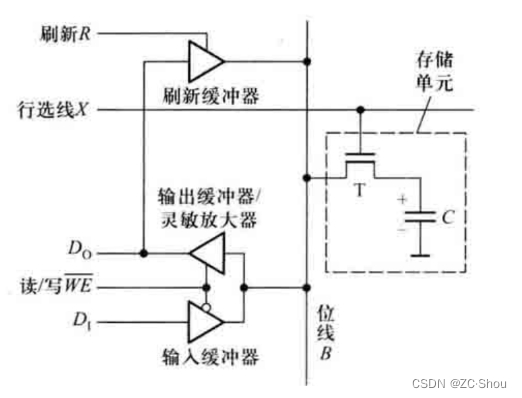

DRAM

??动态随机存储器(Dynamic Random-Access Memory,DRAM)是由众多随机存储器单元按行和列进行组织而成的矩形阵列组成。一个随机存储器单元由一个 MOS 晶体管和一个 MOS 电容器构成,存储一位数据。晶体管和电容器通常都基于金属氧化物半导体(Metal–Oxide–Semiconductor,MOS)技术。

MOS 技术是现代 DRAM 的基础

??电容器可以充电或放电,这两个状态就表示位的两个值。如果没有干预,电容器上的电荷将逐渐泄漏,电容器上的数据很快就会丢失。为了防止这种情况,DRAM 需要一个外部存储器刷新电路,该电路会定期重写电容器中的数据,将它们恢复到原始电荷。

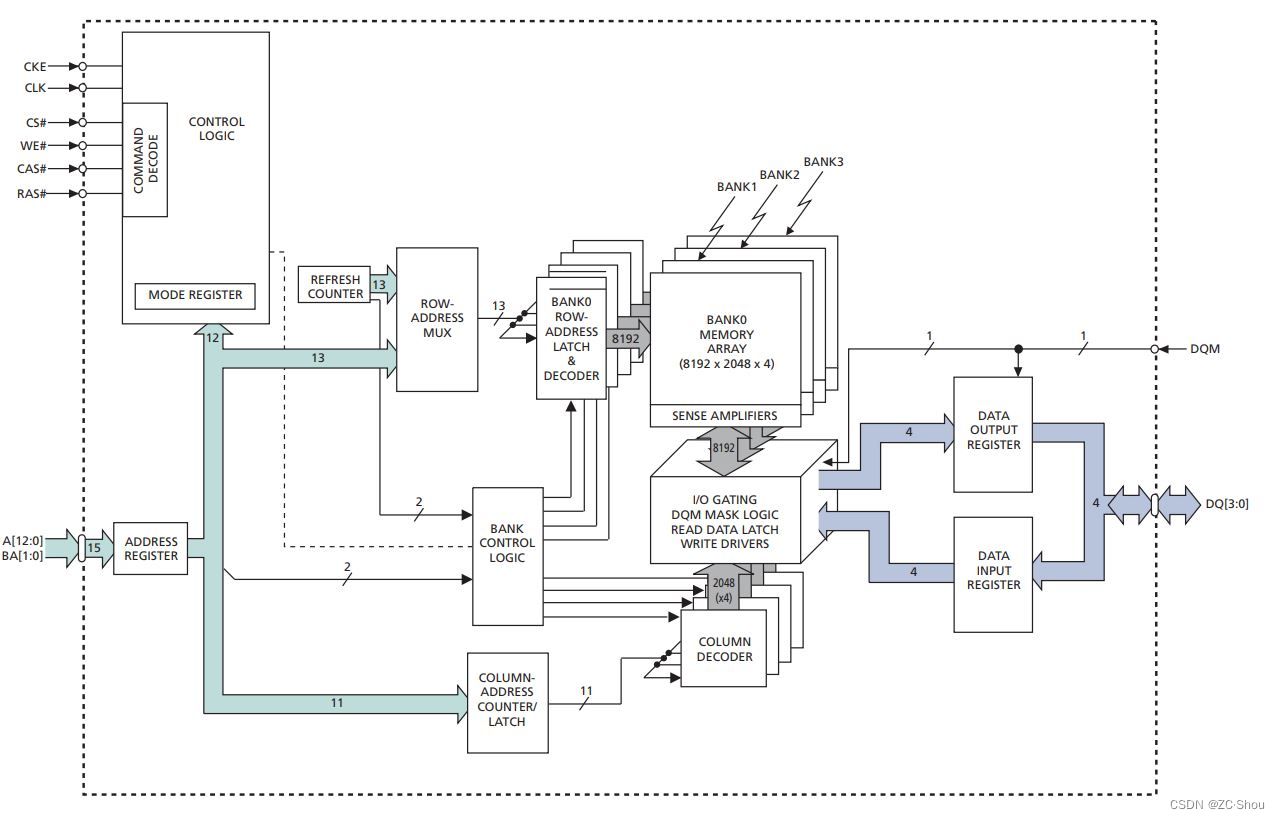

SDRAM

??同步动态随机存取存储器(Synchronous Dynamic Random-Access Memory,SDRAM)是指该 RAM 的时钟频率与对应控制器(北桥、CPU、FPGA)的系统时钟频率相同,而且内部命令的发送与数据传输都以该时钟为基准(数电概念里的同步时序)。

同步 DRAM 存储器是性能最高的外部存储器,可以存储大量数据而不会降低性能

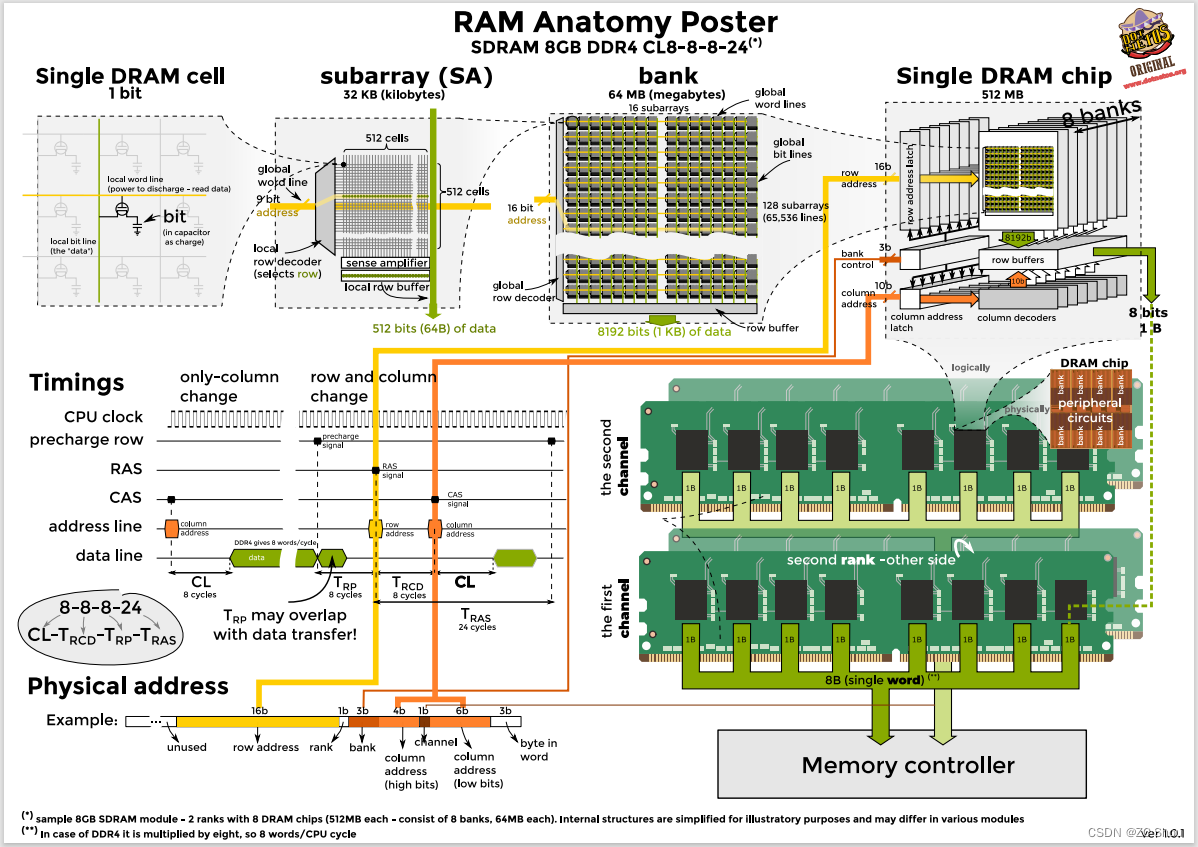

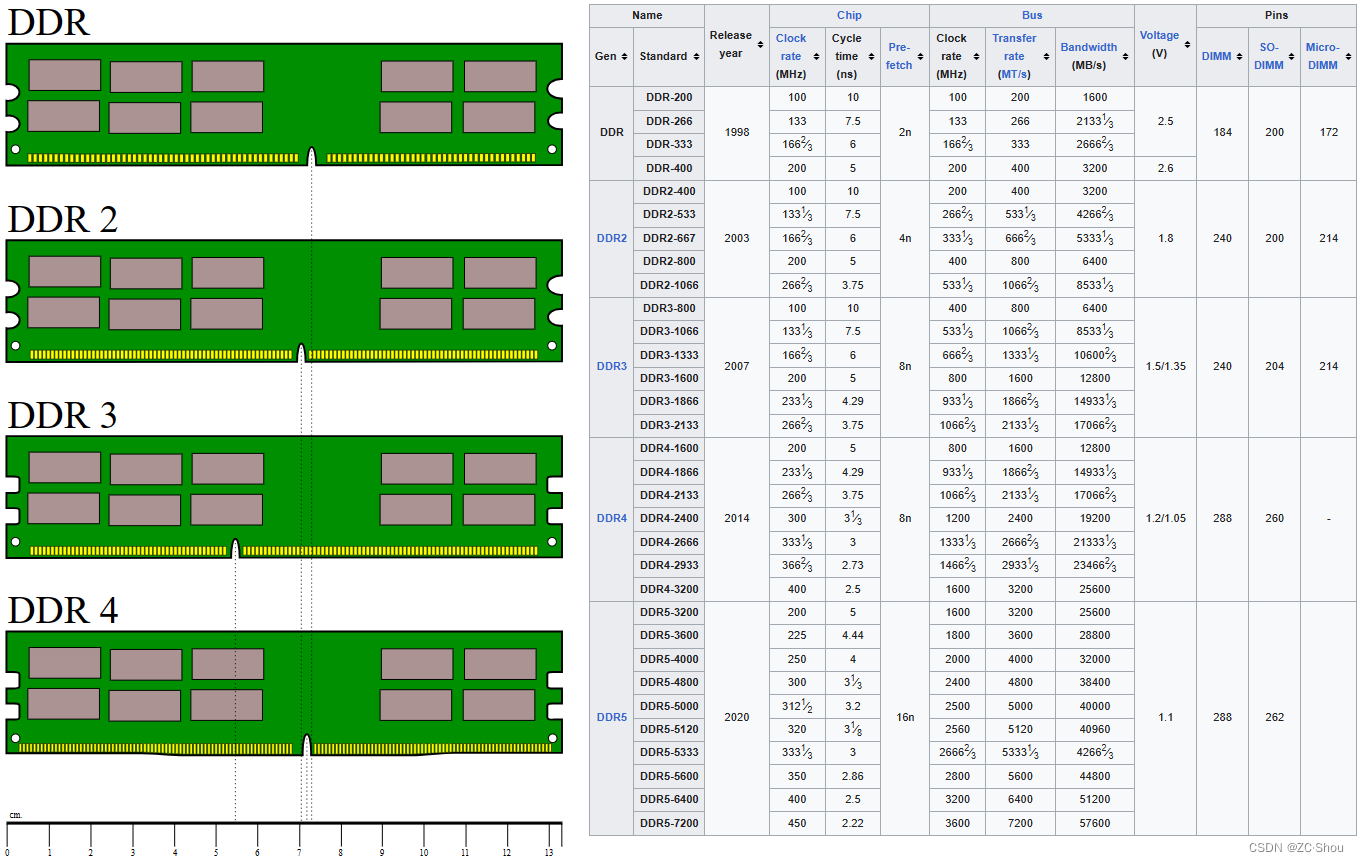

DDR SDRAM

??双倍数据率同步动态随机存取内存(Double Data Rate Synchronous Dynamic Random Access Memory,DDR SDRAM)常简称为 DDR,现在的电脑和手机中用的非常多。其显著特点是在系统时钟的上升沿和下降沿都可以进行数据传输(具有双倍数据传输率的 SDRAM)。

三星在1997 年展示了第一个 DDR 内存原型,并于 1998 年 6 月发布了第一个商用 DDR SDRAM 芯片

??DDR SDRAM 的相关标准由 JEDEC 固态技术协会制定,根据标准的版本, DDR SDRAM 也称为 DDR1 SDRAM,目前已被 DDR2 SDRAM,DDR3 SDRAM,DDR4 SDRAM 和 DDR5 SDRAM 取代。各版本之前互不兼容,无法通用!

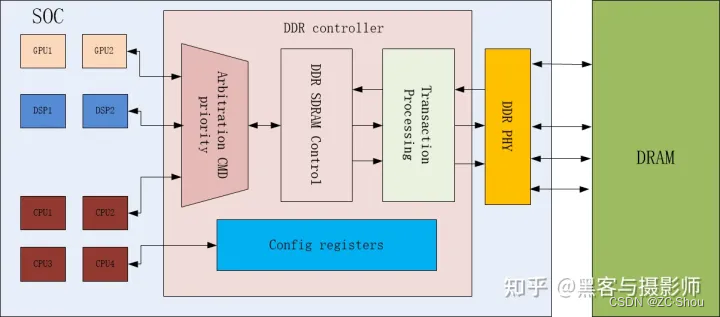

DDR SDRAM 子系统包含 DDR Controller、DDR PHY 和 DRAM 存储颗粒三部分。

-

DDR Controller: 负责初始化 DRAM,并重排读写命令,以获得最大的DRAM带宽。它通过多端口与其他用户核进行连接,这些端口的类型包含AXI4/AXI3/AHB/CHI。每个端口有可配置的宽度、命令和数据FIFO。

-

DDR PHY: 连接 DDR 颗粒和 DDR Controller 的桥梁,它负责把 DDR Controller 发过来的数据转换成符合 DDR 协议的信号,并发送到 DDR 颗粒。相反地,它也负责把 DRAM 发送过来的数据转换成符合 DFI(DDR PHY Interface)协议的信号并发送给内存控制器。DDR PHY 和内存控制器统称为 DDR IP,他们保证了 SoC 和 DRAM 之间的数据传输。

-

DRAM 存储颗粒: 就是上面 DRAM 章节介绍的存储器

PSRAM

??PSRAM(Pseudo Static Random Access Memory,伪静态随机存储器)是具有内置刷新和地址控制电路的 DRAM,使其行为则类似于 SRAM(不需要 SDRAM 那样复杂的控制器和刷新机制,不需要地址拆分成行列地址)。

??与采用 6T(6 个晶体管构成一个存储 Cell)的技术 SRAM 相比,PSRAM 采用的是 1T + 1C(1 个晶体管 + 1 个电容组成一个存储单元)技术,所以在体积上更小但容量更大,同时,PSRAM 的 I/O 接口与 SRAM 相同。

ROM

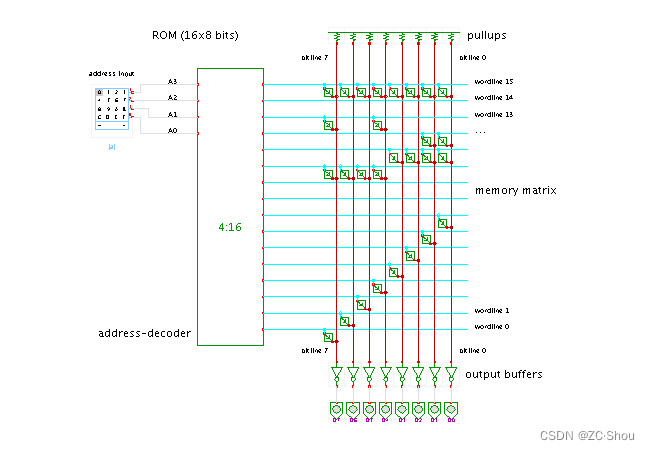

??ROM(Read Only Memory,只读存储器)是一种只能读出事先所存的数据的固态半导体存储器。ROM 中所存数据稳定,断电后所存数据也不会消失。最初的 ROM 一旦存储数据就再也无法将之改变或者删除。

MROM

??掩膜只读存储器(Mask ROM,MROM)中存储的信息只能由 MROM 的生产厂家在掩膜工艺过程中进程编写。在制造过程中,生产厂家将客户提供的书籍以特制光罩(Mask)烧录于线路中。

??MROM 的行线和列线的交点处都设置了 MOS 管,在制造时的最后一道掩膜工艺,按照规定的编码布局来控制 MOS 管是否与行线、列线相连,相连者定为1(或 0),未连者为 0(或 1)。这种存储器一旦由生产厂家制造完毕,后续就再也无法修改。

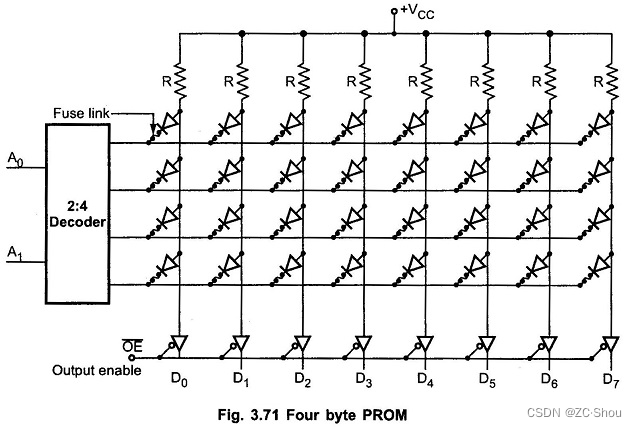

PROM

??可编程只读存储器(Programmable ROM,PROM)可以通过称为 PROM 编程器的特殊设备进行编程。通常,原理是该设备使用高电压永久性地破坏或创建芯片内的内部链路(熔断器或反熔断器)。因此,一个 PROM 只能被编程一次,以后再也无法更改!

- PROM 于 1956 年由美籍华人周文青在美国被研发

- PROM 属于 PLD(可编程逻辑器件)

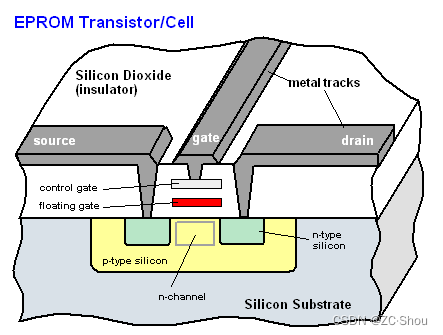

EPROM

??可抹除可编程只读存储器(Erasable Programmable ROM,EPROM)可利用高电压将数据编程写入,但抹除时需将线路曝光于紫外线下一段时间(EPROM 在封装外壳上会预留一个石英玻璃所制的透明窗以便进行紫外线曝光),数据始可被清空,再供重复使用。

英特尔的 Dov Frohman 于 1971 年发明

??EPROM 使用在控制门下方带有浮动栅极的晶体管,一个晶体管单元存储一个比特位。为了对位进行编程,向控制门施加了高压。这导致电子穿过绝缘氧化层进入浮动栅极,从而阻碍了控制栅极的后续操作。0 或 1 取决于控制门上的电压是否被阻断。

??浮动门可以保持电荷十多年或直到设备被擦除,但是,EPROM 仅支持几百个擦除-写入周期!

由于石英玻璃所制的透明窗比较费劲,后来又发明了 一次性可编程存储器(One-Time Programmable ROM,OTP)

EEPROM

??电可擦可编程序只读存储器(Electrically Erasable Programmable ROM,EEPROM) 被组织为浮栅晶体管阵列,一个存储单元由两个晶体管组成(一个浮栅晶体管,一个选择极晶体管)存储一个比特位,改写数据时,通过选择极晶体管来选择或反选某个浮栅。

??最初,EEPROM 仅限于单字节操作,这使得它们速度较慢,但现代 EEPROM 允许多字节页面操作。EEPROM 用于擦除和重新编程的寿命有限,现代 EEPROM 中达到一百万次操作。EEPROM 运作原理类似 EPROM,但抹除的方式是使用高电场来完成,因此不需要透明窗。

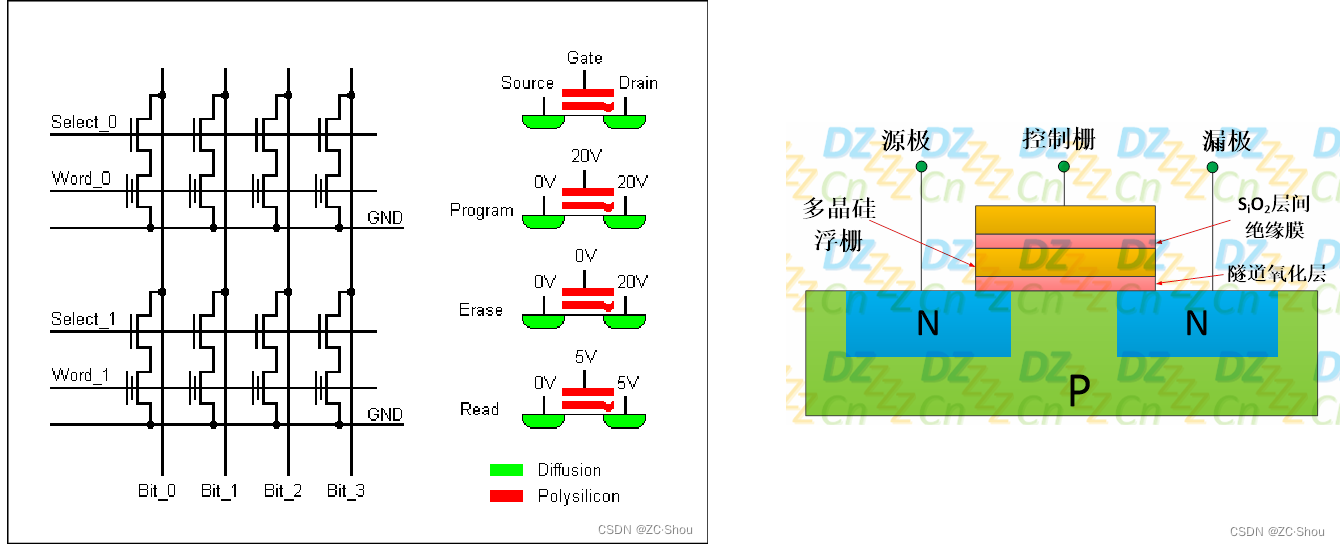

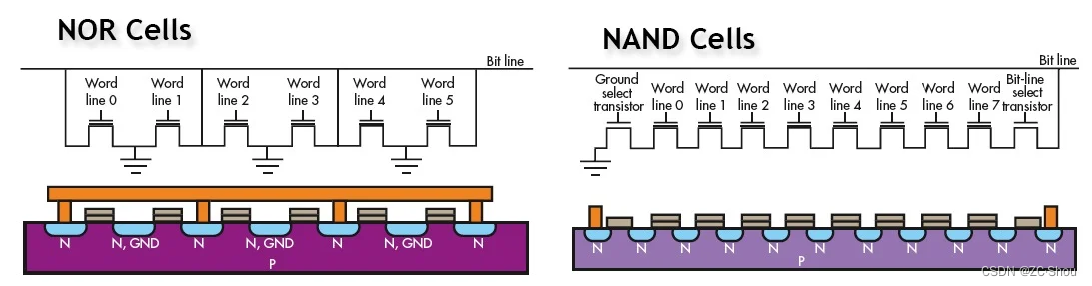

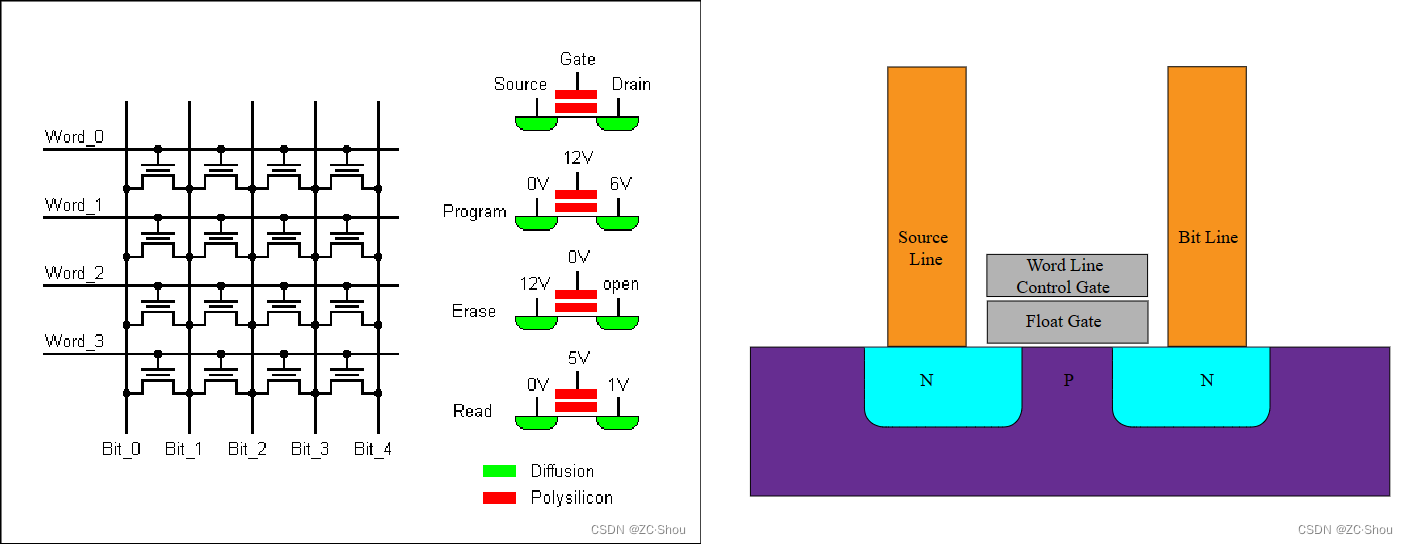

FLASH

??快擦除读写存储器(Flash Memory,常简称 FLASH 或 闪存)是英特尔公司 90 年代中期发明的一种高密度、非易失性的读/写半导体存储器,它既有 EEPROM 的特点,又有 RAM 的特点,是一种全新的存储结构。主要有 NOR FLASH 和 NAND FLASH 两大类(以 NOR 和 NAND 逻辑门命名)。

??NOR FLASH 和 NAND FLASH 都由浮动栅极 MOSFET 组成,一个浮动栅极 MOSFET 存储一个比特位。它们在电路级别有所不同,具体取决于位线或字线的状态是拉高还是拉低:在 NAND FLASH 中,位线和字线之间的关系类似于 NAND 门;在 NOR FALSH 中,它类似于 NOR 门。

??与 EEPROM 一样,FLASH 使用电可擦技术,整个快闪存储器可以在一秒钟至几秒内被擦除,速度比 EPROM 快得多。另外,它能擦除存储器中的某些块,而不是整块芯片。与 EEPROM 一样,FLASH 也有编写寿命,通常为十万次或百万次。

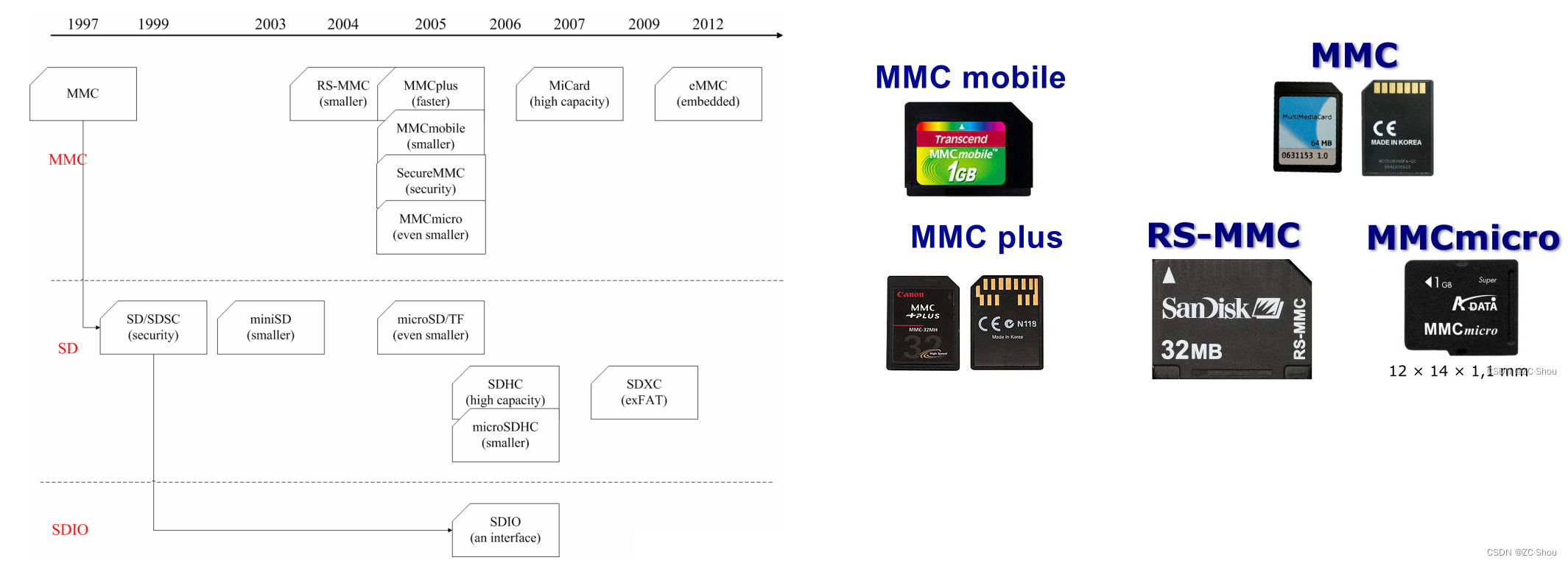

MMC

??MMC(MultiMedia Card)中文多媒体卡,是在 1997 年,由西门子公司(Siemens AG)和闪迪公司(SanDisk)使用东芝的 NAND 闪存开发的一种存储卡。在多年的发展中,MMC 卡出现了多种不同尺寸的衍生版本:

MMC 卡逐渐被 SD 卡取代

??MMC 卡对应的规范是在 1998 年,由 14 个公司作为最初的成员成立的多媒体卡协会(MMCA)负责制定和维护。2008 年 9 月,MMCA 将 MMC 相关知识产权转移给了 JEDEC,MMCA 解散。相关规范可以在 JEDEC 官网下载(部分是收费的)。

??MMC 规范定义了 MMC 卡支持 SPI 和 MMC 两种通信方式,定义了诸如卡的形态、尺寸、容量、电气信号、和主机之间的通信协议等。SD 卡、eMMC 都是基于 MMC 的,MMC 本身是对 NAND 的封装。

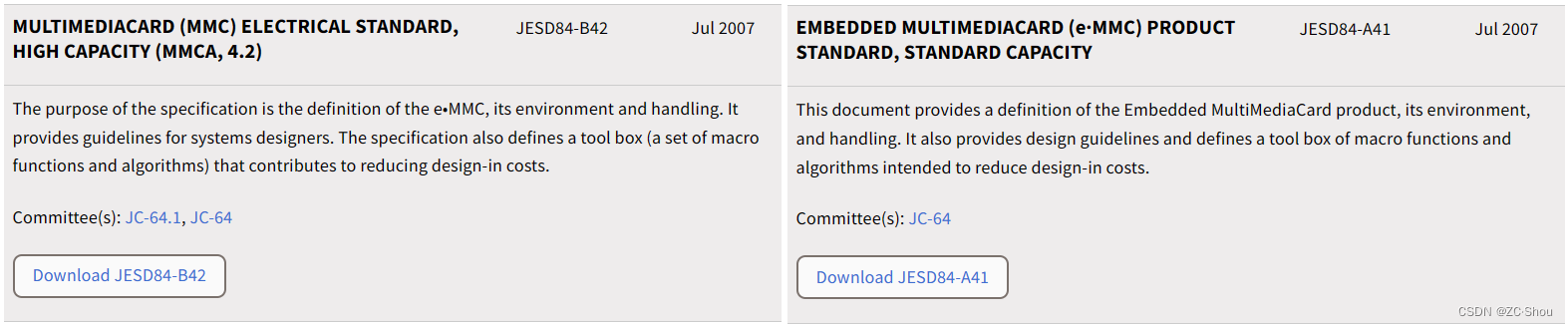

eMMC

??嵌入式多媒体卡(Embedded Multimedia Card,eMMC)是一种新的存储技术,最初的标准是由 MMC 协会所订立,现在由 JEDEC 负责维护。该架构标准将 MMC 组件(闪存加控制器)放入一个小的球栅阵列封装(BGA)中,是一种主要用于印刷电路板的嵌入式非易失性存储器系统。

从 2016 年开始,逐渐被 UFS 取代

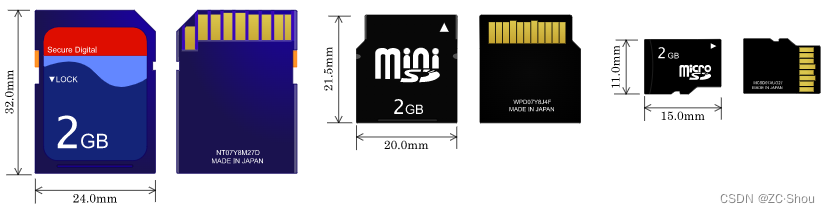

SD

??SD (Secure Digital)是由 SD 协会(SDA)开发的一种专有的非易失性闪存卡格式,用于便携式设备。最初是由东芝在现有的 MMC 中添加了加密硬件,并将其命名为 Secure Digital 或 SD Card。同样,在多年的发展中,SD 卡也出现了多种不同尺寸的衍生版本

micro SD 卡最初被命名为 TransFlash,就是我们之前说的 T-Flash 卡(TF卡)

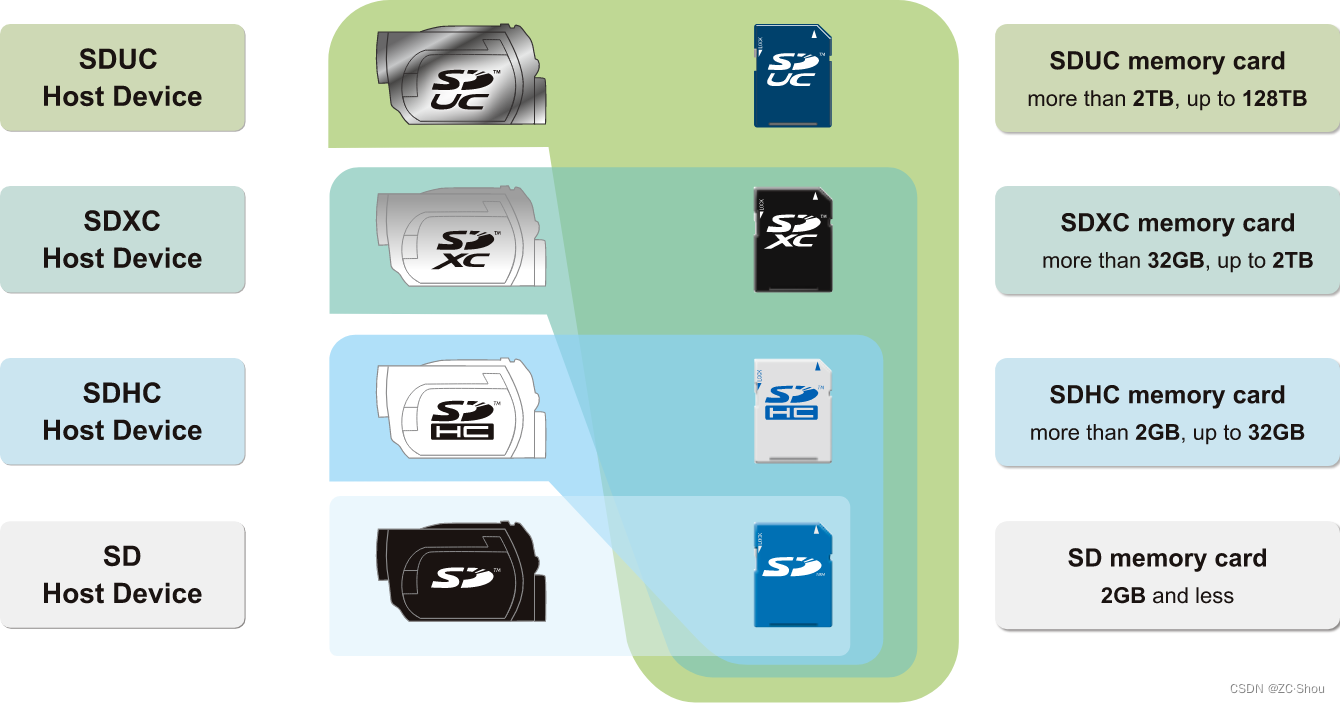

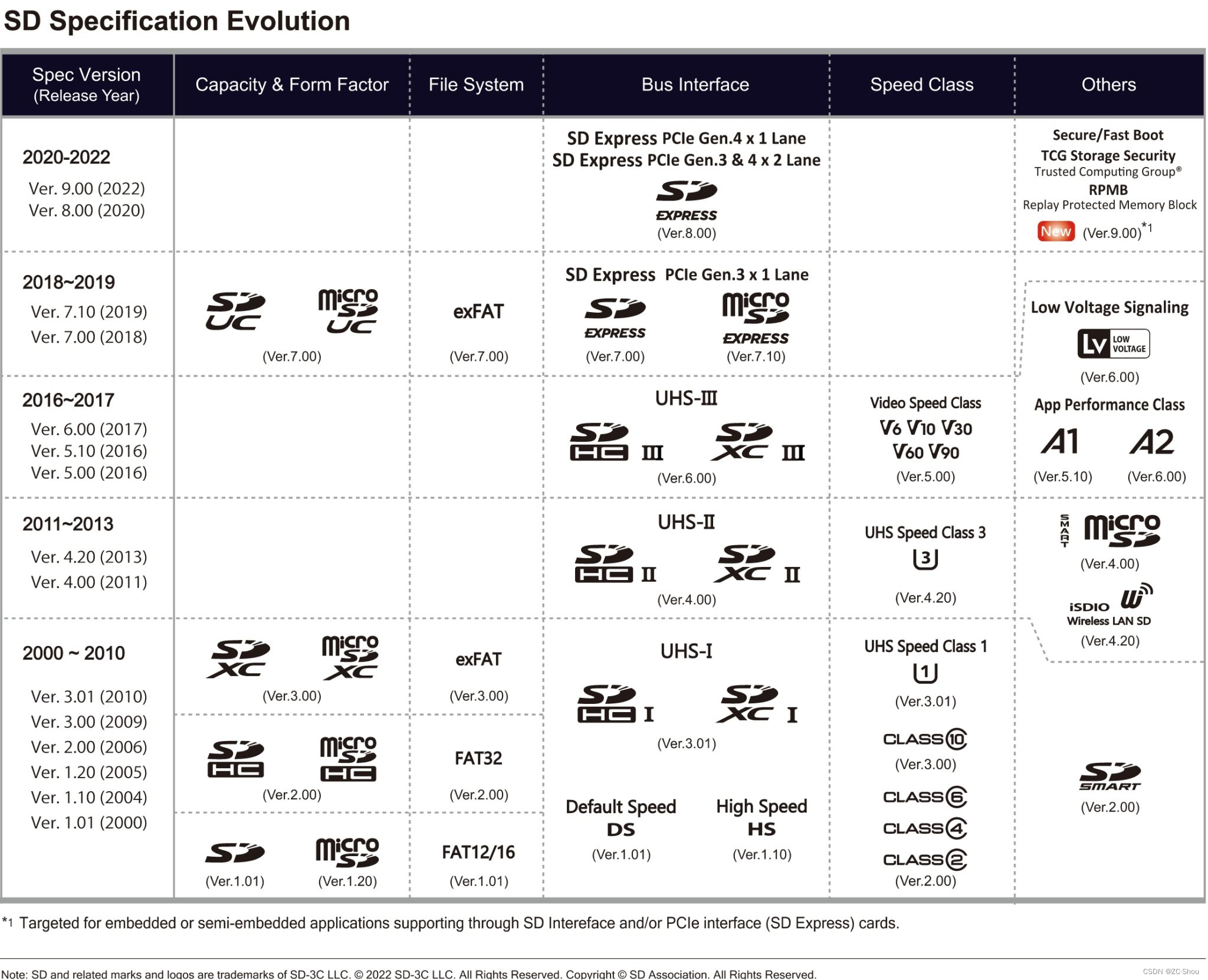

??在多年的发展中,SD 标准目前工制定了五种不同容量的卡系列。这五个系列是最初的标准容量(SDSC),高容量(SDHC),扩展容量(SDXC),超容量(SDUC)。而且,每种卡的读写速度也有所不同。

SD 协会为 Windows 和 Mac OS X 提供了一个格式化实用程序,用于检查和格式化 SD、SDHC、SDXC 和 SDUC 卡

??SD 卡对应的标准于 1999 年 8 月由 SanDisk、松下和东芝共同推出,作为对多媒体卡(MMC)的改进。这些公司还于 2000 年 1 月成立了SD 协会(SDA),以促进和创建 SD 卡标准。

SD 通信协议兼容 MMC通信协议(弃用了一些命令,也增加了一些命令),因此,MMC 卡可以在支持 SD 卡的设备设备上运行

SDIO

??SDIO(Secure Digital Input and Output,安全数字输入输出接口)由 SD 卡协议演进而来,向前兼容 SD 卡协议,在 SD 卡协议基础上增加了 CMD52、CMD53 命令,两个命令可以方便的访问某个功能的某个地址寄存器。

??SDIO 本身是一种接口(协议标准),我们可以用它来连接 SD 卡,从而实现对 SD 卡的读写。此外,还可以用它来连接 SDIO 接口设备。

??2006 年 1 月 SD 卡协会宣布的 SDHC 格式带来了改进(32 GB 存储容量、FAT32 文件系统的强制支持等)。4月,SDA 发布了 SD 存储卡标准中非安全相关部分以及安全数字输入输出(SDIO)卡和标准 SD 主机控制器的详细规范

参考

- http://www.wowotech.net/basic_tech/mmc_sd_sdio_intro.html

- https://blog.csdn.net/m0_37621078/article/details/105093404

- https://blog.csdn.net/qq_43706825/article/details/115454702

- https://www.chinastor.com/baike/fenlei/

- https://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/40-memories/20-rom/chapter.html

- https://blog.csdn.net/weixin_44643510/article/details/111682297

- https://www.cnblogs.com/still-smile/p/12050501.html

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!