Quartus的Signal Tap II的使用技巧

概述:

Signal Tap II全称Signal Tap II Logic Analyzer,是第二代系统级调试工具,它集成在Quartus II软件中,可以捕获和显示实时信号,是一款功能强大、极具实用性的FPGA片上调试工具软件。

传统的FPGA板级调试是由外接的逻辑分析仪连接到FPGA的控制引脚,将内部信号引出至引脚I/O上,接着进行板级调试。

? ? ? ? note:这种方法缺点是,需要逻辑分析仪,且效率很低,经常需要飞线,而且如果要测10个信号以上就非常庞杂,而且,考虑到100Mhz左右的信号完整性,不能用逻辑分析仪,要用高性能的示波器,测量的信号质量也存在失真的情况。

Signal Tap II在线逻辑分析仪克服了以上所有缺点,将采样逻辑电路编程后放在FPGA中,即,用FPGA资源来构成了嵌入式逻辑分析仪。

操作:

1、打开Signal Tap Logic Analyzer

在Quartus软件中打开待测工程,然后选择Signal Tap Logic Analyzer,

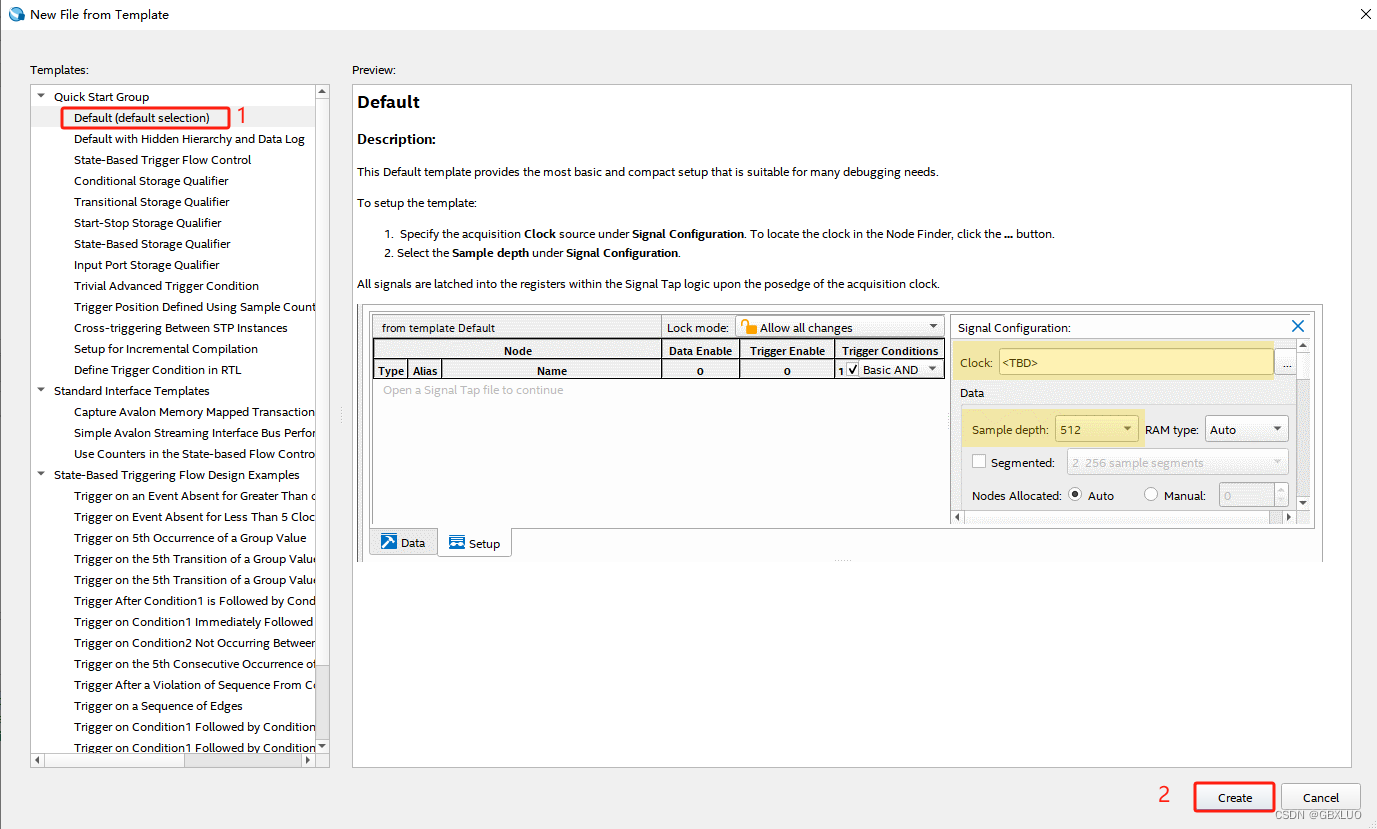

在弹出的New File from Template窗口选择Default (default selection)即可;

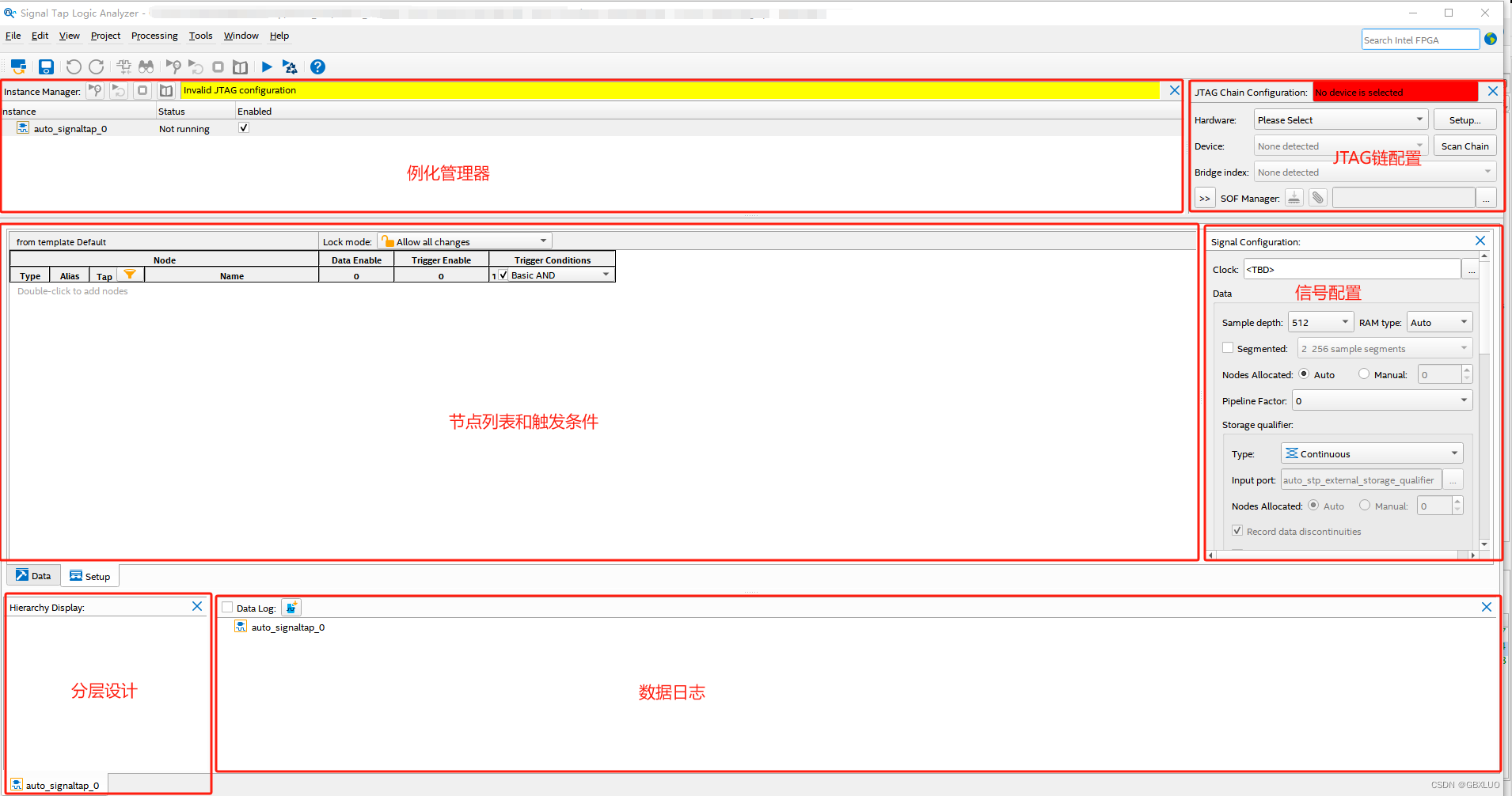

弹出Signal Tap Logic Analyzer界面,包含例化管理器(Instance Manager)、JTAG链配置(JTAG Chain Configuration)、节点列表和触发条件(Data与Set两个子界面可选)、信号配置(Signal Configuration)、分层设计(Hierarchy Display,分层显示)以及数据日志(Data Log),如下图。

2、实例管理

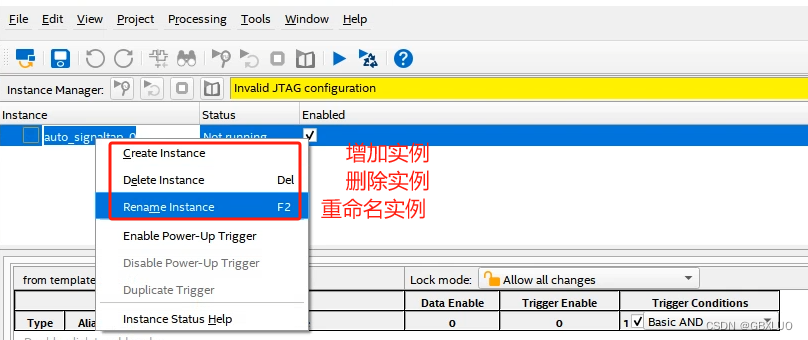

首先选择例化管理器,选中默认的auto_signaltap_0,可以增加、删除、重命名实例,这里一个实例可以理解为一组信号对+一个配置时钟,可以通过Enabled来选择该实例是否被编译到该工程中,因此可以有多组实例,方便分析各不同模块的信号。

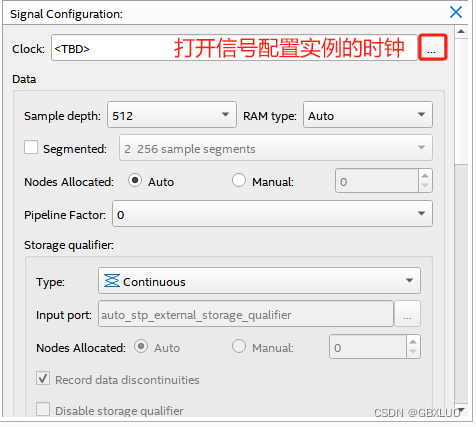

3、时钟配置

选择信号配置,进行实例的时钟配置。

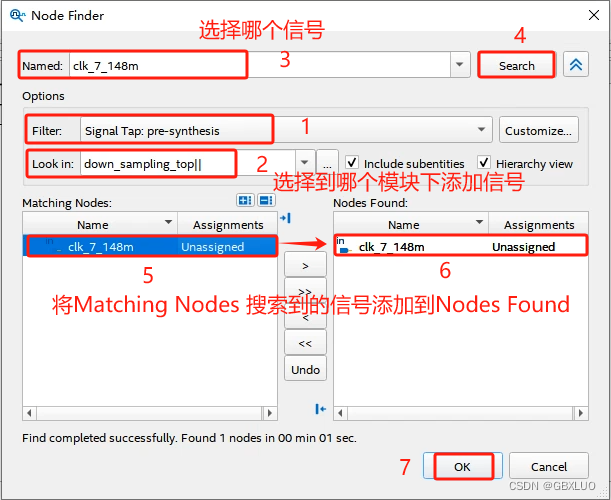

弹出的Node Finder界面中,首先在Options-Filter栏选择:Signal Tap: Pre-synthesis,在Options-Look in栏中选择down_sampling_top.v模块,接着输入想要在down_sampling_top.v模块中查看的信号的时钟:clk_7_148m,然后search搜索,在Matching Nodes中双击即可将clk_7_148m添加到Nodes Found栏,并单击ok即可完成时钟的添加,如下图:

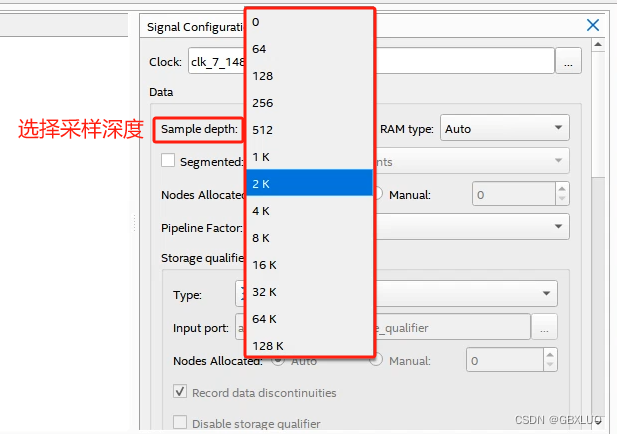

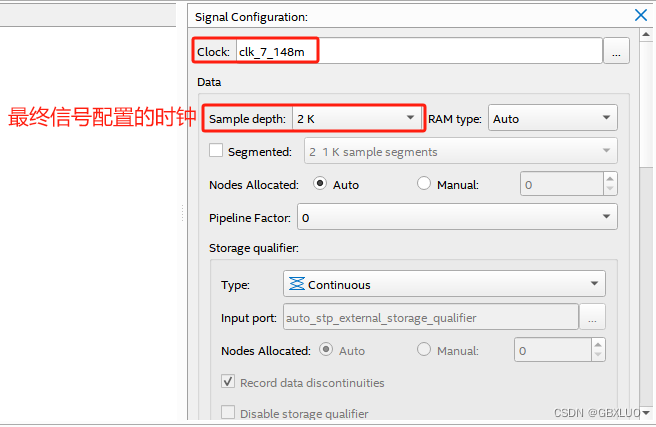

完成后根据需要选择采样深度即可,其他默认,如下图:

4、添加待抓取信号

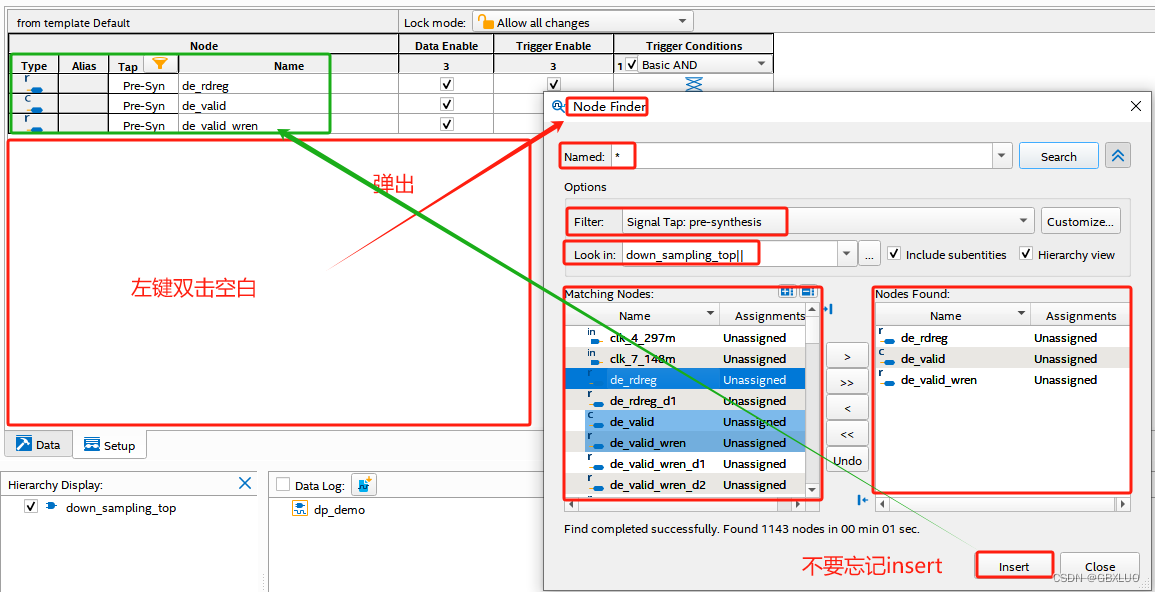

双击节点列表和触发条件界面,弹出Node Finder窗口,与上一步添加时钟信号一样的设置,选择自己想要的信号,最后要记得单击insert按键才能正常将信号成功添加。

5、设置信号触发条件

默认如下,但是可以根据需要对各个信号进行单独设置触发条件:

| Don't Care | 不设置触发方式 |

| Low | 低电平触发 |

| Falling Edge | 下降沿触发 |

| Rising Edge | 上升沿触发 |

| High | 高电平触发 |

| Either Edge | 双边沿触发 |

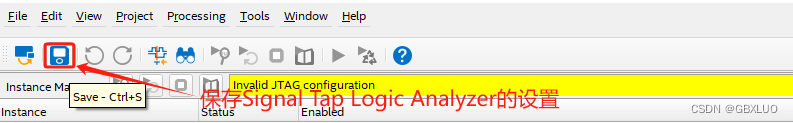

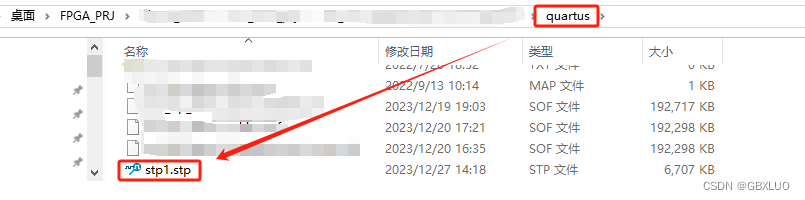

6、记得保存

选择保存路径为工程所在的quartus文件夹下,打开所在目录会发现多了一个stp1.stp文件,该文件即上述添加至工程中的分析文件。

7、开始编译

在工具栏选择Start Compilation 开始编译,等待工程编译完成即可。

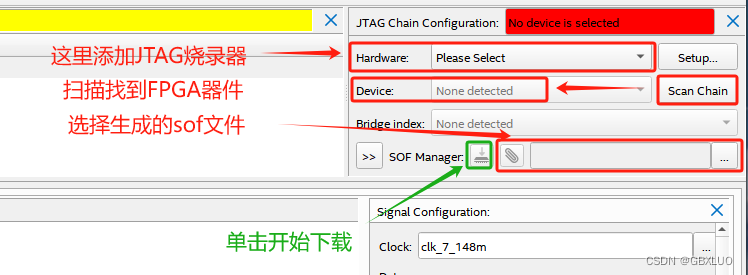

8、选择烧录文件并下载

首先连接JTAG烧录器与FPGA板,并给FPGA板子上电,接着Scan Chain,识别FPGA器件,然后选择生成的sof文件,并单击开始下载。

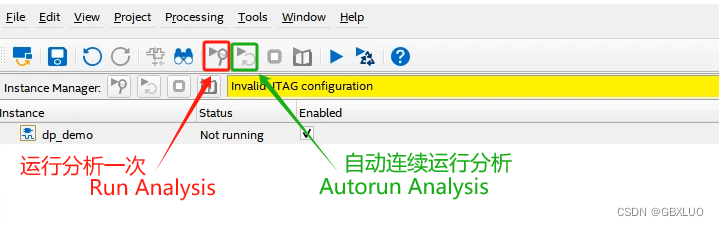

9、查看抓取的波形

单击Run Analysis运行分析一次,也就是刷新采样一次,单击Autorun Analysis自动连续运行分析,也就是一直刷新采样。

补充:

1、在打开的波形窗口,左键单击放大波形窗口,右键单击缩小波形窗口;

2、波形窗口的数据默认16进制,可以选中信号名后,右键单击-Bus Display Format中选择十进制或者其他进制;

3、在Signal Tap Logic Analyzer中下载程序时软件比较卡,可以在Quartus 的Programmer中下载好以后直接在Signal Tap Logic Analyzer分析;

4、在上述第4步添加待住区信号时,如果有些wire/reg定义的信号不能被观察到,应该是被Quartus软件优化掉了,导致无法使用Signal Tap II观察,有两种解决办法:

? ? ? ? 方法一、将wire/reg定义的信号改成端口信号(这种方法繁琐不推荐);

? ? ? ? 方法二、在待观察的wire/reg定义的信号后面添加特殊字符:

wire????????[9:0]? ? ? ?time_cnt? /*synthesis keep*/ ;

reg? ? ? ? ?[9:0]? ? ? ? time_cnt /*synthesis keep*/;

或者

(* noprune *)?wire????????[9:0]? ? ? ?time_cnt ;

(* noprune *)?reg? ? ? ? [9:0]? ? ? ?time_cnt ;

5、Signal Tap II除了支持电平、边沿触发外,还支持计数触发,如可以对time_cnt计数器设置具体的值来触发。

参考链接:

?

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!