STM32时钟树

2024-01-09 08:33:52

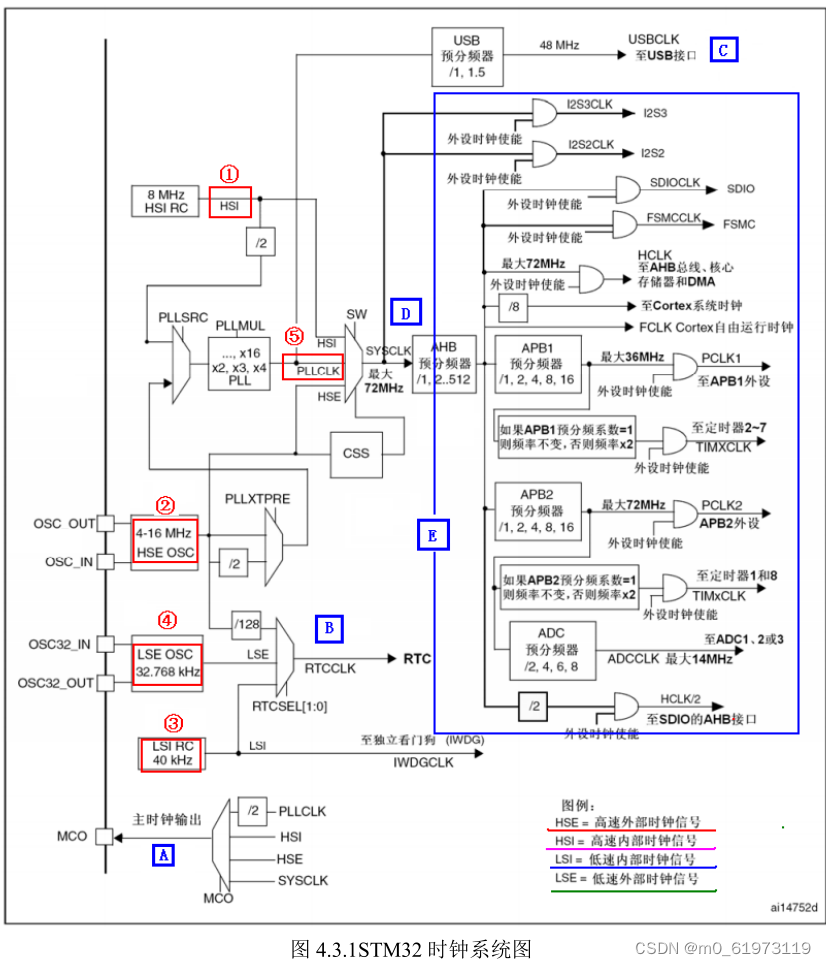

一、四个时钟源

?

?

?二、时钟树

各类时钟简括:

1.HSE时钟(高速外部时钟):来源为外部无源晶振,通常速度8M。

2.HSI时钟(高速内部时钟):来源为芯片内部,大小为8M,当HSE故障时,系统时钟会自动切换到HSI,知道HSE启动成功,相当于HSE的替补。

3.PLLCLK(锁相环时钟):来源为HSI/2、HSE经过倍频所得。

4.SYSCLK(系统时钟):来源为HSI、HSE、PLLCLK,最高速度为72M。

5.HCLK(AHB高速总线时钟):来源由系统时钟分频得到,速度最高为72M。

6.PCLK1(APB1低总线时钟):来源为HCLK分频得到,速度最高为36M ,为APB1总线上的外设提供时钟。

7.PCLK2(APB2高总线时钟):来源为HCLK分频得到,速度最高为72M,为APB2总线上的外设提供时钟。

8.RTC时钟:来源为HSE_RTC(HSE分频得到)、LSE、LSI,为芯片内部的RTC外设提供时钟。

9.MCO时钟输出 :来源为PLLCLK/2、HSE、HSI、SYSCLK,微控制器时钟输出引脚,由PA8复用所得。

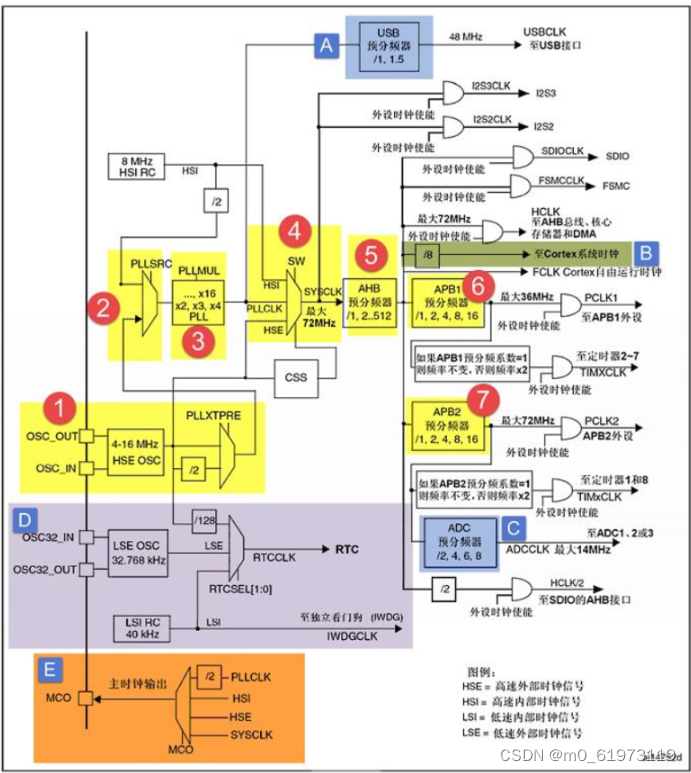

三、系统配置时钟

图中序号1~7对应着系统设置配置的流程

?

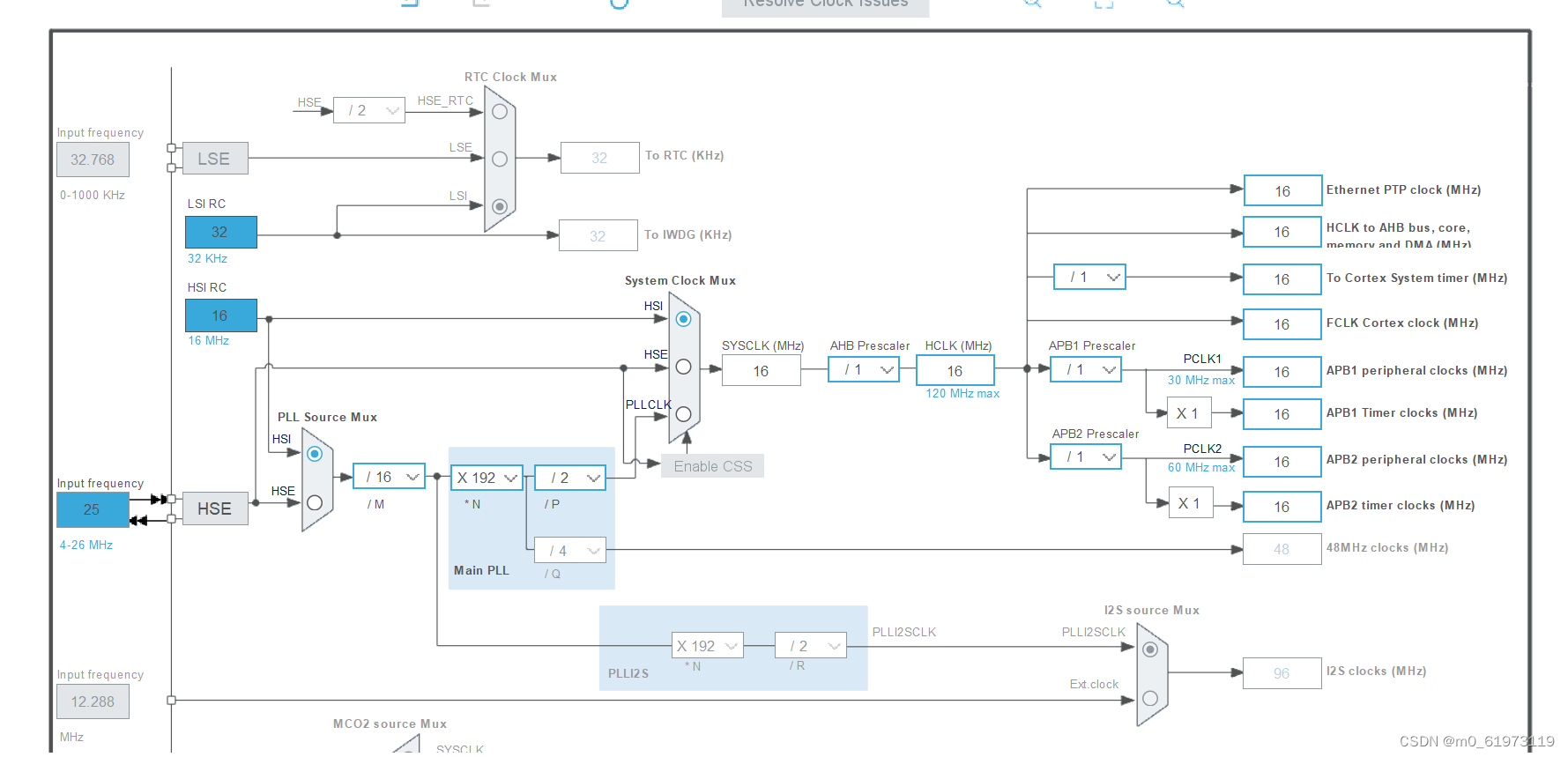

?四、HAL库直接使用cubemx软件图形化界面配置

?

五、常见英文缩写意思

- RCC: Reset and Clock Control,即复位和时钟控制。

- HSE: High Speed External Clock signal,高速外部时钟信号,即是OSC_IN和OSC_OUT接口所接的4~16MHz的晶振,一般接8MHz。

- LSE: Low Speed External Clock signal,低速外部时钟信号,即是OSC32_IN和OSC32_OUT接口,指外部用于RTC的32.768KHz晶振。

- HSI: High Speed Internal Clock signal,高速内部时钟信号,出厂校准的8MHz内部RC振荡器。

- LSI: Low Speed Internal Clock signal,高速内部时钟信号,带有校准功能的40KHz的内部RC振荡器。

- RTC: Real Time Clock实时时钟,用于带有年、月、日、小时、分钟、秒钟的计时器。

- PLL:锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

- SYSCLK:系统时钟,最高72MHz。

- AHB:高级高性能总线,这是一种“系统总线”AHB主要用于高性能模块(如CPU、DMA和DSP等)之间的连接。AHB 系统由主模块、从模块和基础结构(Infrastructure)3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。

- APB:一种外围总线。APB主要用于低带宽的周边外设之间的连接,例如UART等,它的总线架构不像 AHB支持多个主模块,在APB里面唯一的主模块就是APB 桥。

- OSC:晶振

文章来源:https://blog.csdn.net/m0_61973119/article/details/135410664

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!