【计算机组成&体系结构】双端口RAM和多体结构主存储器

一、存取周期回顾

DRAM的电容结构决定了DRAM的破坏性读出,因此DRAM需要在存取过程中不断的恢复刷新才能使数据不丢失。

由此引发了两个问题,多核CPU的每个核都要访存怎么办?以及如何解决恢复时间长的问题?

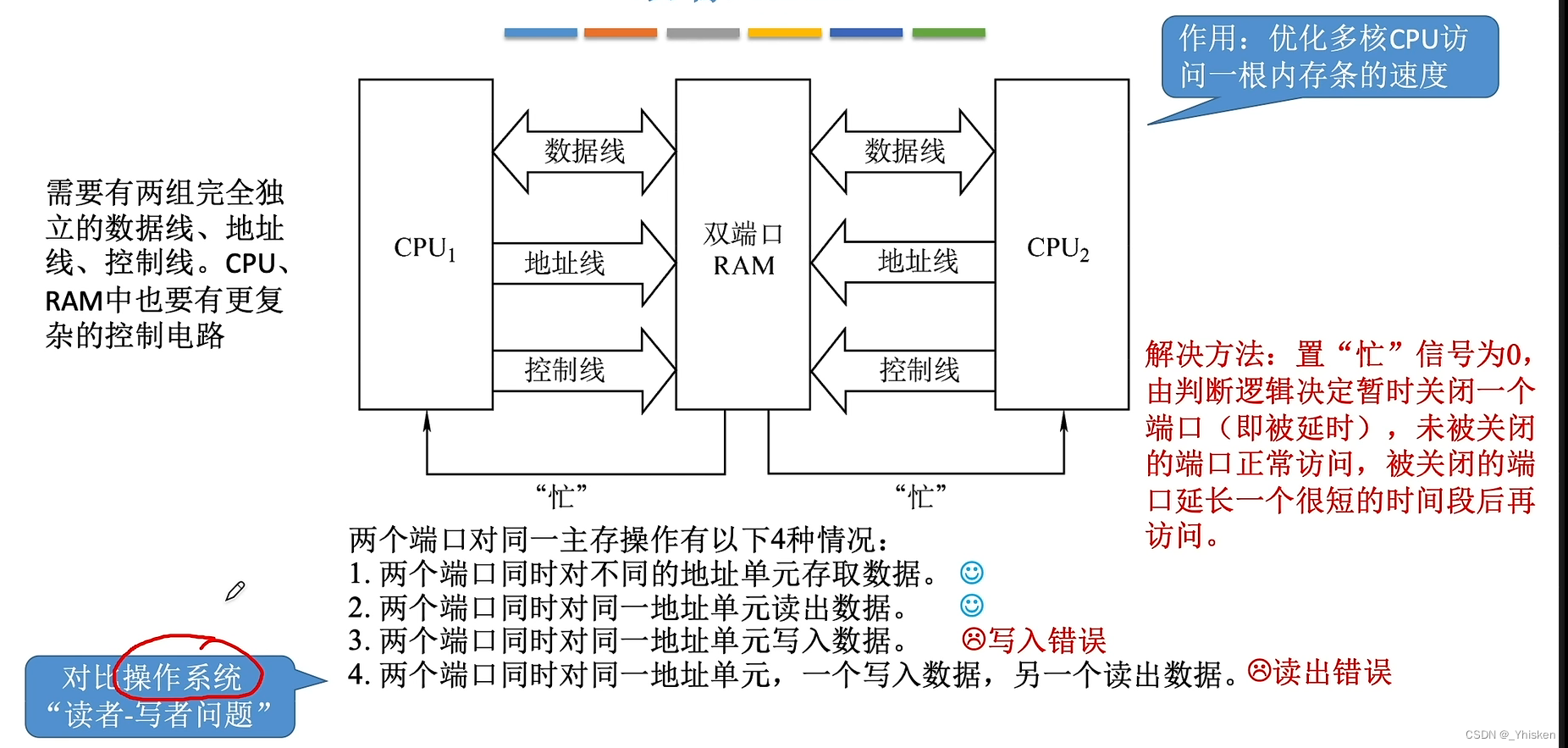

二、双端口RAM?

双端口RAM技术支持双核CPU同时访问一根内存条,当然有些操作是可以进行,有些则不能,如上图中列举的3,4会发生错误,这种情况要分先后执行操作,即将一个端口延时。?

三、多体结构主存储器

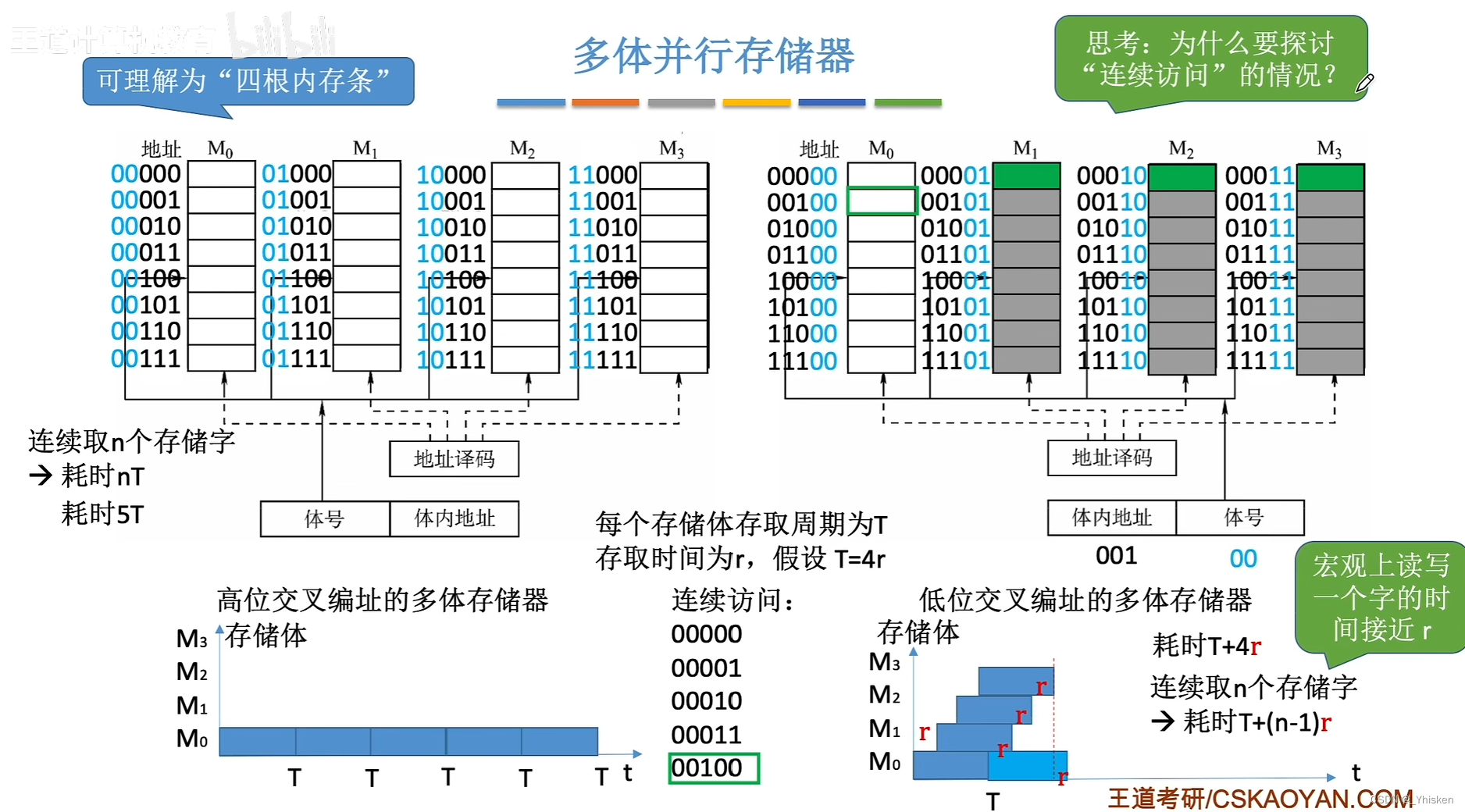

多体并行存储器,如上图所示,有四个存储体,每个存储体各自的地址应该是连续的,那么如果把它们合在一起,它们的地址可以列优先的依次增加,也可以行优先的依次增加。而这也就是高位交叉编址和低位交叉编址,本质区别就是在编码中是用高2位的二进制数表示第几个存储体还是用低位的2位二进制数表示第几个存储体。

低位交叉编址的好处就是我们顺序访问内存的时候,在访问下一个地址的时候不需要等待恢复刷新,因为下个地址在下一个存储体当中,而访问下一个存储体的时候,上个存储体的刷新不影响当前访问的地址。上图中的耗时计算说明了这个问题。

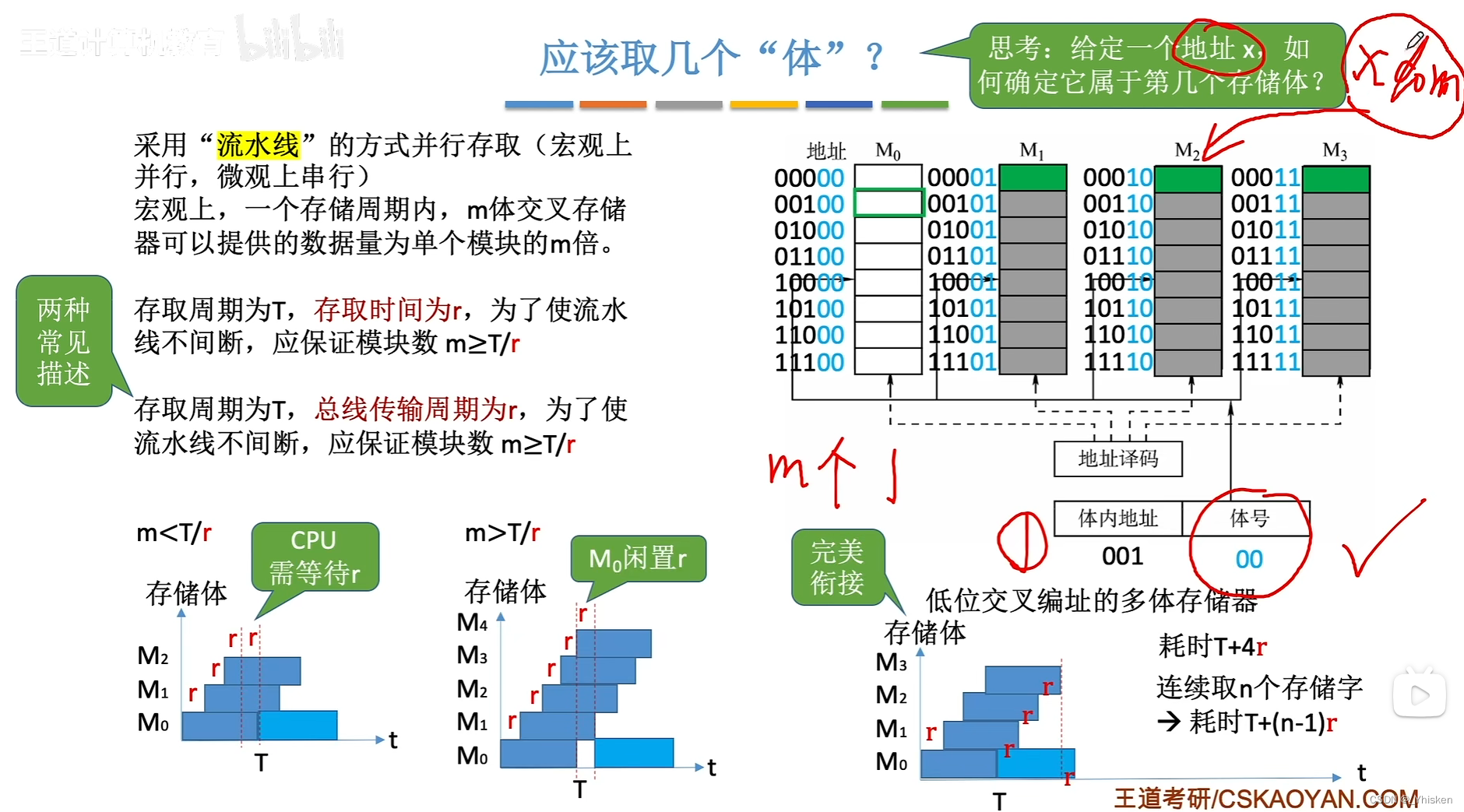

存储体的数量应该≥ T/r,T是存取周期,r是存取时间。原因如上图所示,如果小于T/r,会导致CPU仍然被存储体的恢复时间拖累。而如果大于的话会导致存储体有闲置时间,这个时间被浪费了。因此其实我们应该尽可能保证存储体的数量 = T/r。

至于通过地址判断属于第几个存储体,二进制直接看低位两位即可,十进制则对x取模即可。

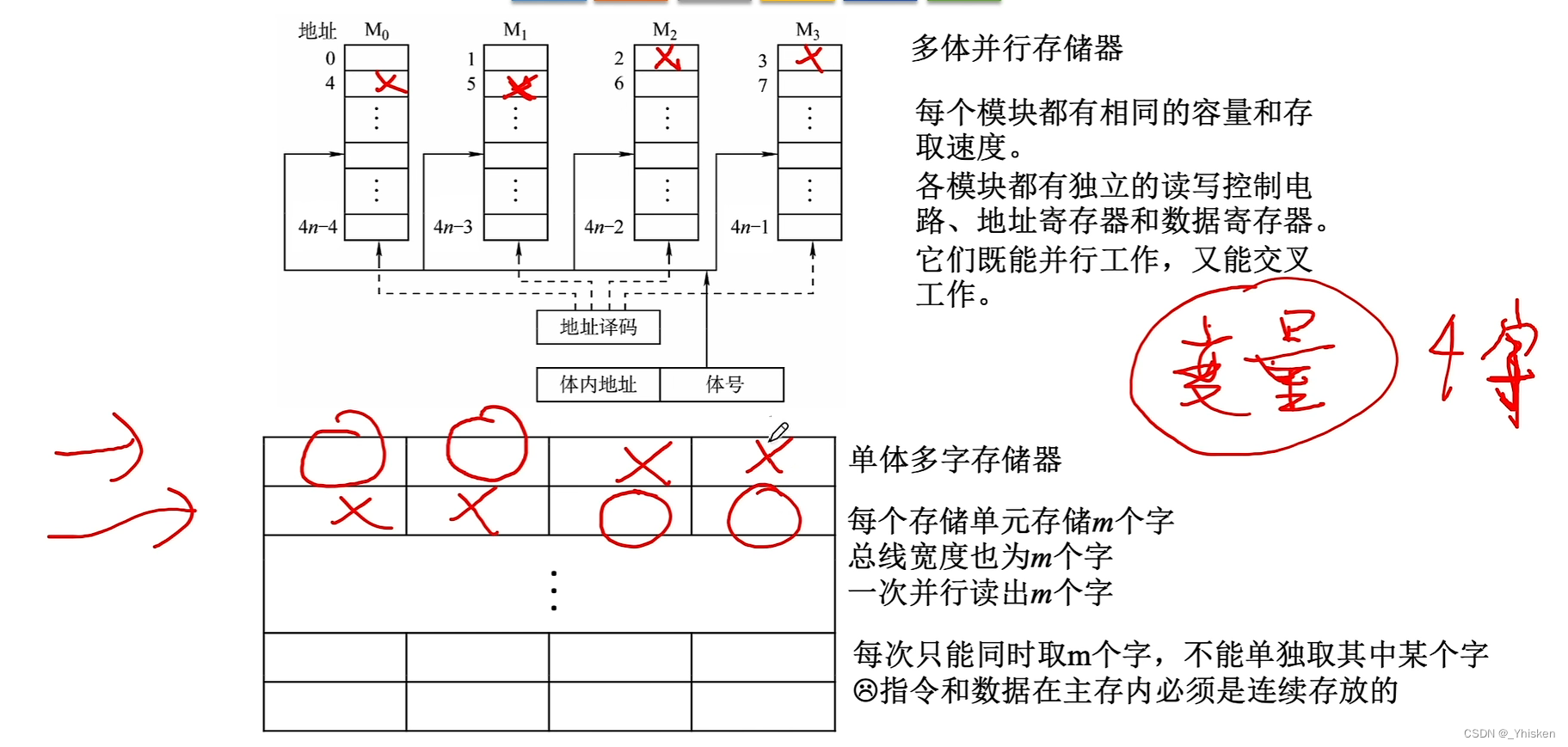

多体并行和单体多字

我们上面提到的多体结构是多体并行,各个存储体直接是相互独立的,可以选择从哪个存储体读出哪一个字,灵活性较高。

而与之相对的就是单体多字存储器,就是把四个存储体合并,整个存储器只有一套读写电路,地址存器,数据寄存器。每次可读出m个字,每个存储单元存储m个字,总线宽度也要随之提升。灵活性较差,不能单独读某个字,只能读某一行(可能会读入冗余信息)。

但两种方案的时间平均来看,平均读取一个字的时间是一样的。?

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!