vivado 关于时钟

2023-12-20 21:32:51

关于时钟

在数字设计中,时钟代表了从寄存器可靠传输数据的时间基准注册。AMD Vivado?集成设计环境(IDE)计时引擎使用时钟计算时序路径要求并通过以下方式报告设计时序裕度的特性松弛计算的方法有关更多信息,请参阅Vivado Design Suite用户指南:设计分析和结束技术(UG906)。必须正确定义时钟,以获得最佳定时路径覆盖率的最大值精确以下特性定义了时钟:

?它定义在其树根的驱动器引脚或端口上,称为源点。

?其边缘由周期和波形特性的组合来描述。

?周期以纳秒为单位指定。它对应于波形所经过的时间重复。

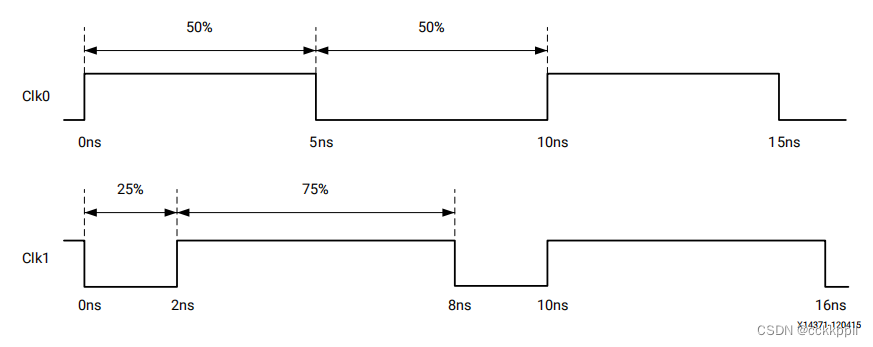

?波形是上升沿和下降沿绝对时间的列表,单位为纳秒,在时钟周期。该列表必须包含偶数个值。第一个值总是对应于第一上升沿。除非另有规定,占空比默认为50%并且相移为0ns。如下图所示,时钟Clk0具有10ns的周期、50%的占空比和0ns阶段时钟Clk1具有8ns周期、75%占空比(高时间是8ns中的6ns)和2ns上升沿相移。

Clk0: period = 10, waveform = {0 5}

Clk1: period = 8, waveform = {2 8}

传播的时钟

周期和波形特性代表了时钟的理想特性。进入时FPGA并通过时钟树传播,时钟边缘被延迟并变为受到噪声和硬件行为引起的变化的影响。这些特性称为时钟网络延迟和时钟不确定性。时钟的不确定性包括:

?时钟抖动(请参阅时钟抖动)

?相位误差

?您指定的任何额外的不确定性(请参阅额外的时钟不确定性)

默认情况下,Vivado IDE总是将时钟视为传播的时钟,即非理想时钟,以便以提供包括时钟树插入延迟和不确定性的精确松弛值。

专用硬件资源

AMD FPGA的专用硬件资源有效支持大量设计时钟。这些时钟通常由板上的外部组件生成。他们通常通过输入端口进入设备。

They can also be generated by special primitives called Clock Modifying Blocks, such as:

? MMCM

? PLL

? BUFR

它们也可以通过诸如LUT和寄存器之类的规则单元进行转换。

以下部分介绍了如何根据时钟的来源来最好地定义时钟。

文章来源:https://blog.csdn.net/cckkppll/article/details/135117253

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!