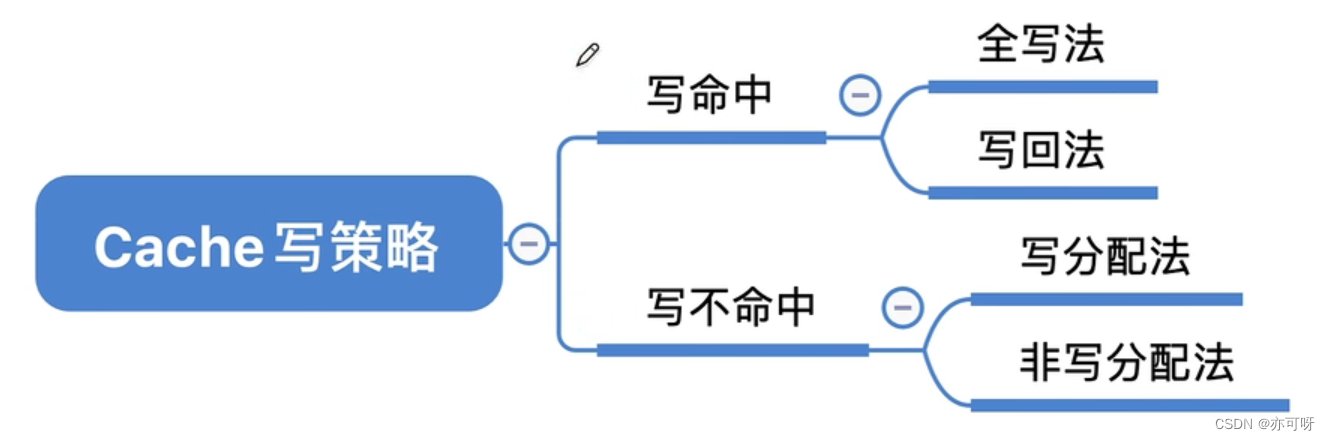

Cache写策略

\quad

CPU修改了cache中的数据副本,如何确保主存中数据母本的一致性?

\quad

为何不讨论读命中、读不命中的情况?

因为读不会改变原来的数据

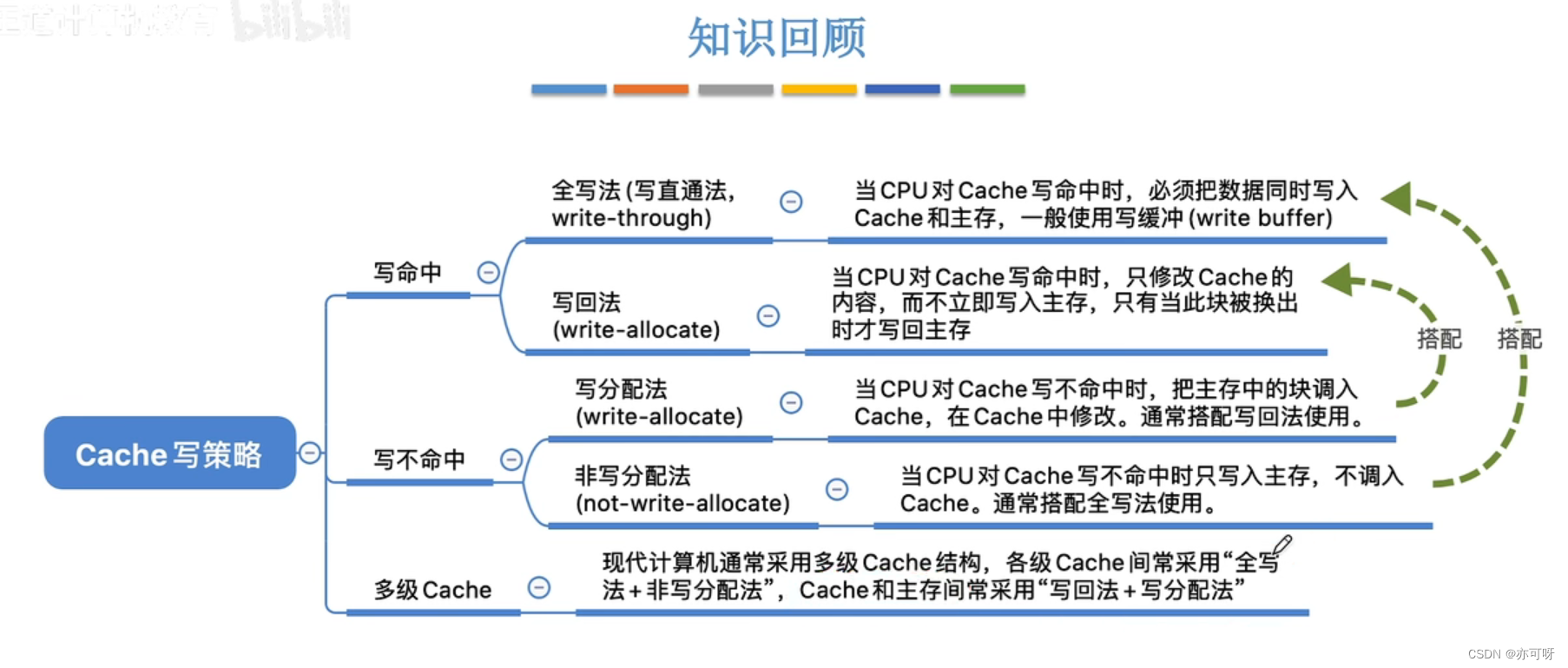

一. 写命中

\quad

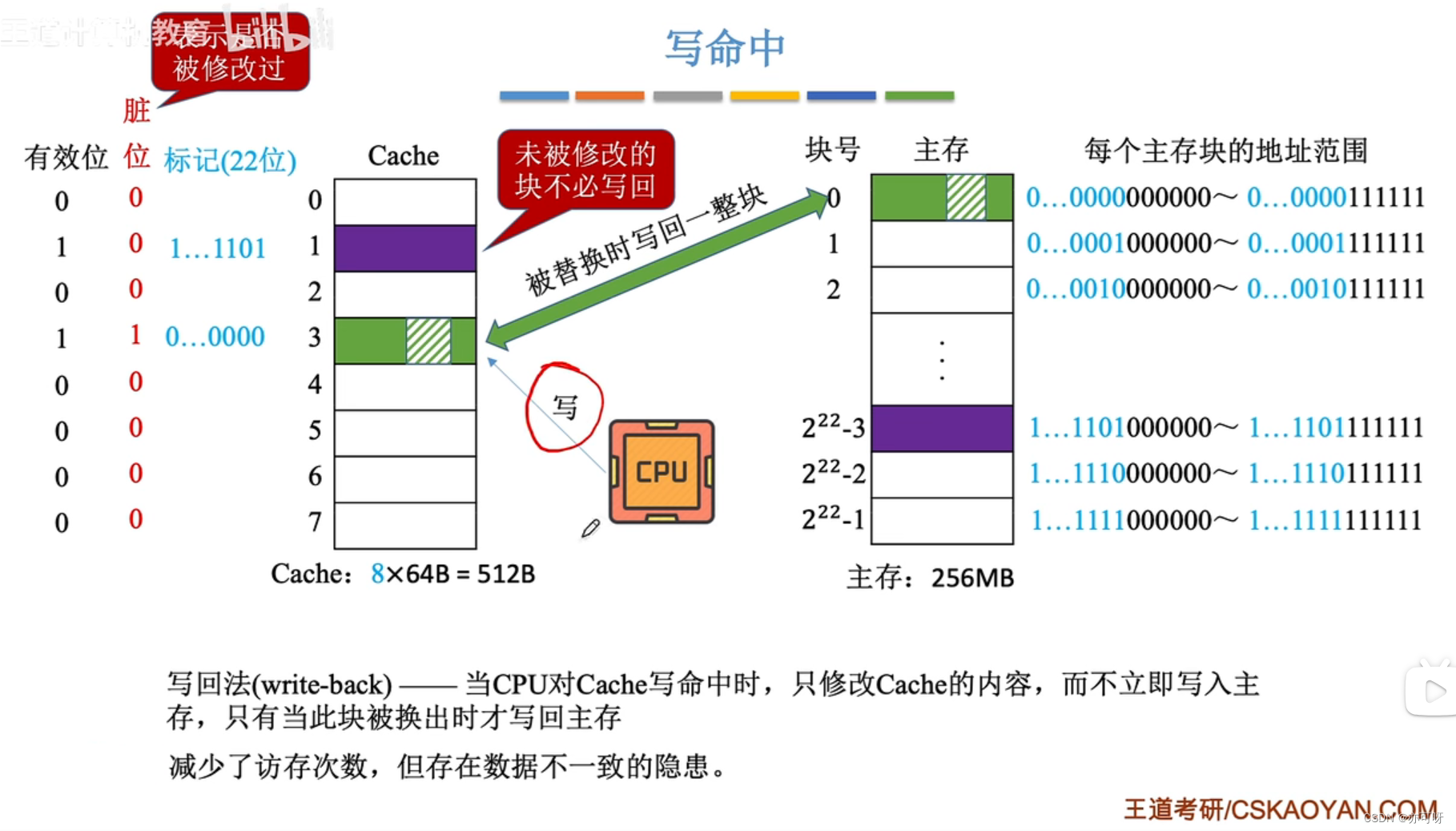

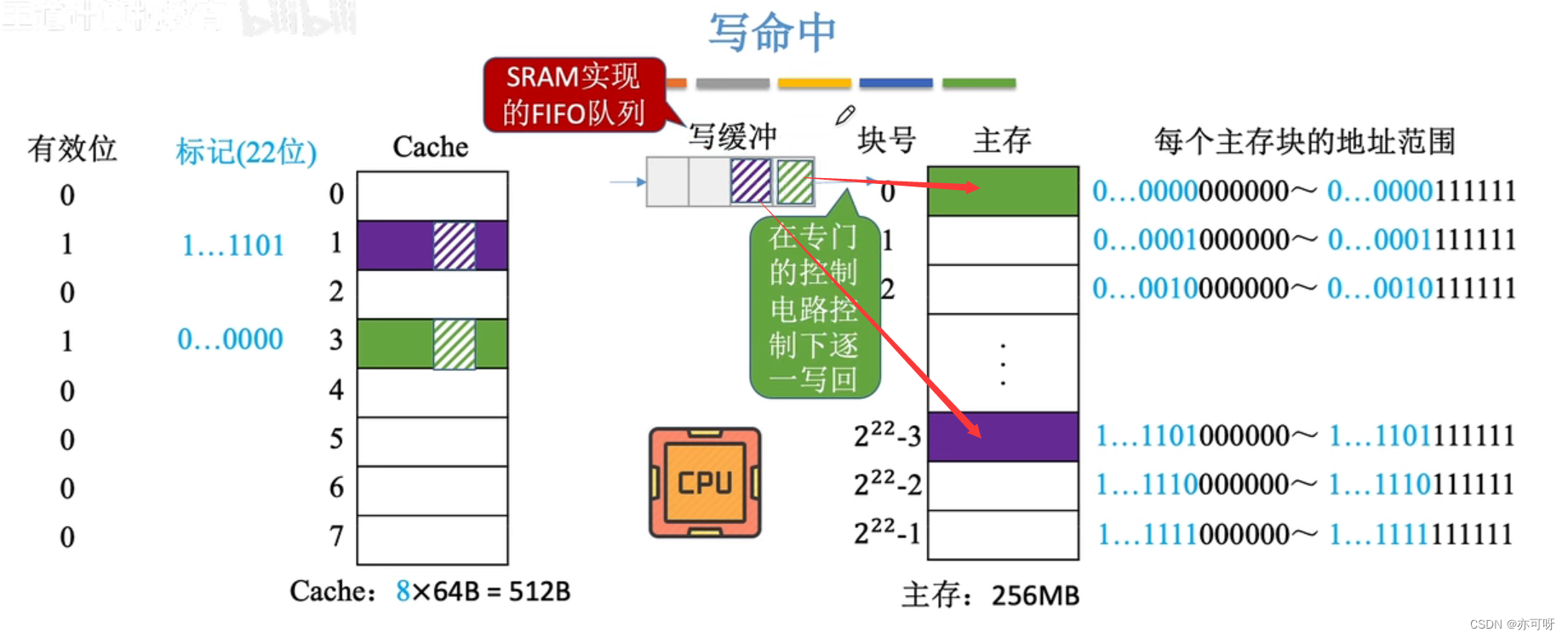

写回法

被修改过的数据在被替换的时候会被写回主存, 而怎么知道这个Cache行被修改过, 我们添加了脏位, 脏位为1则需要替换, 缺点就是会导致Cache与主存的数据不能实时保持一致

\quad

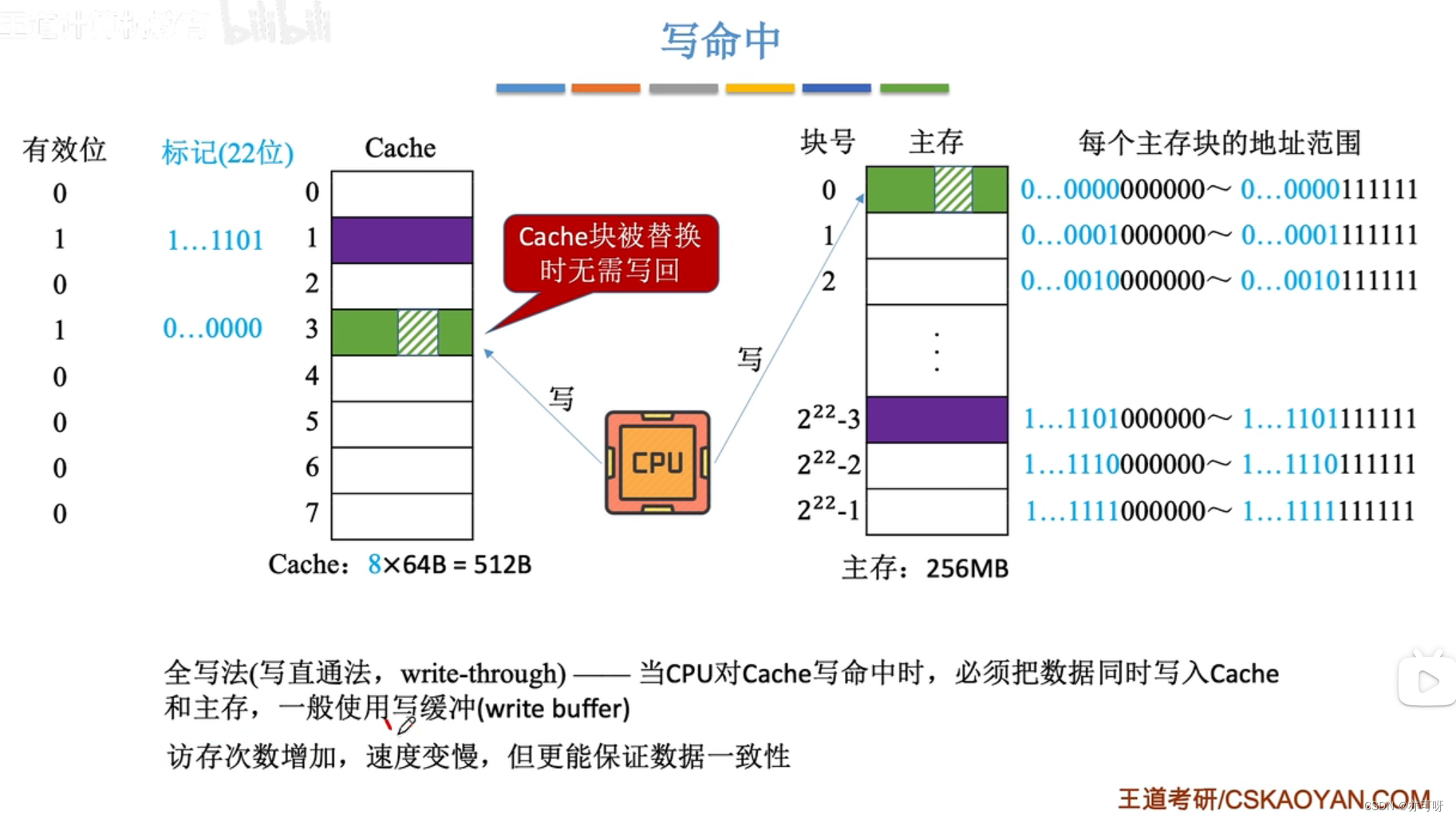

全写法

不需要写回

\quad

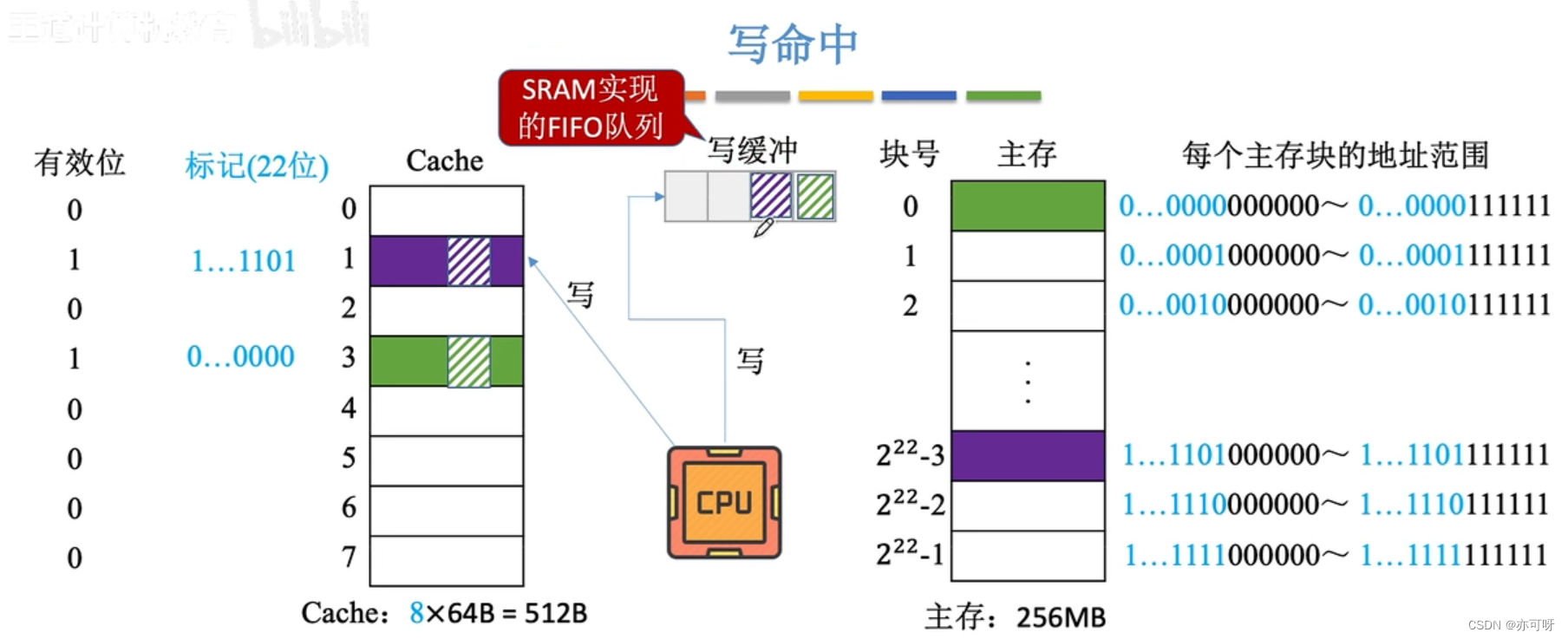

为了避免频繁访问主存, 我们增加了写缓冲

\quad

SRAM是静态随机存储器, 速度很快

FIFO是先进先出

有了写缓冲, Cache和写缓冲可以同时工作, Cache一边工作, 写缓冲一边将被修改过的数据写回主存

使用写缓冲,CPU写的速度很快,若写操作不频繁,则效果很好。若写操作很频繁,可能会因为写缓冲饱和而发生阻塞

\quad

\quad

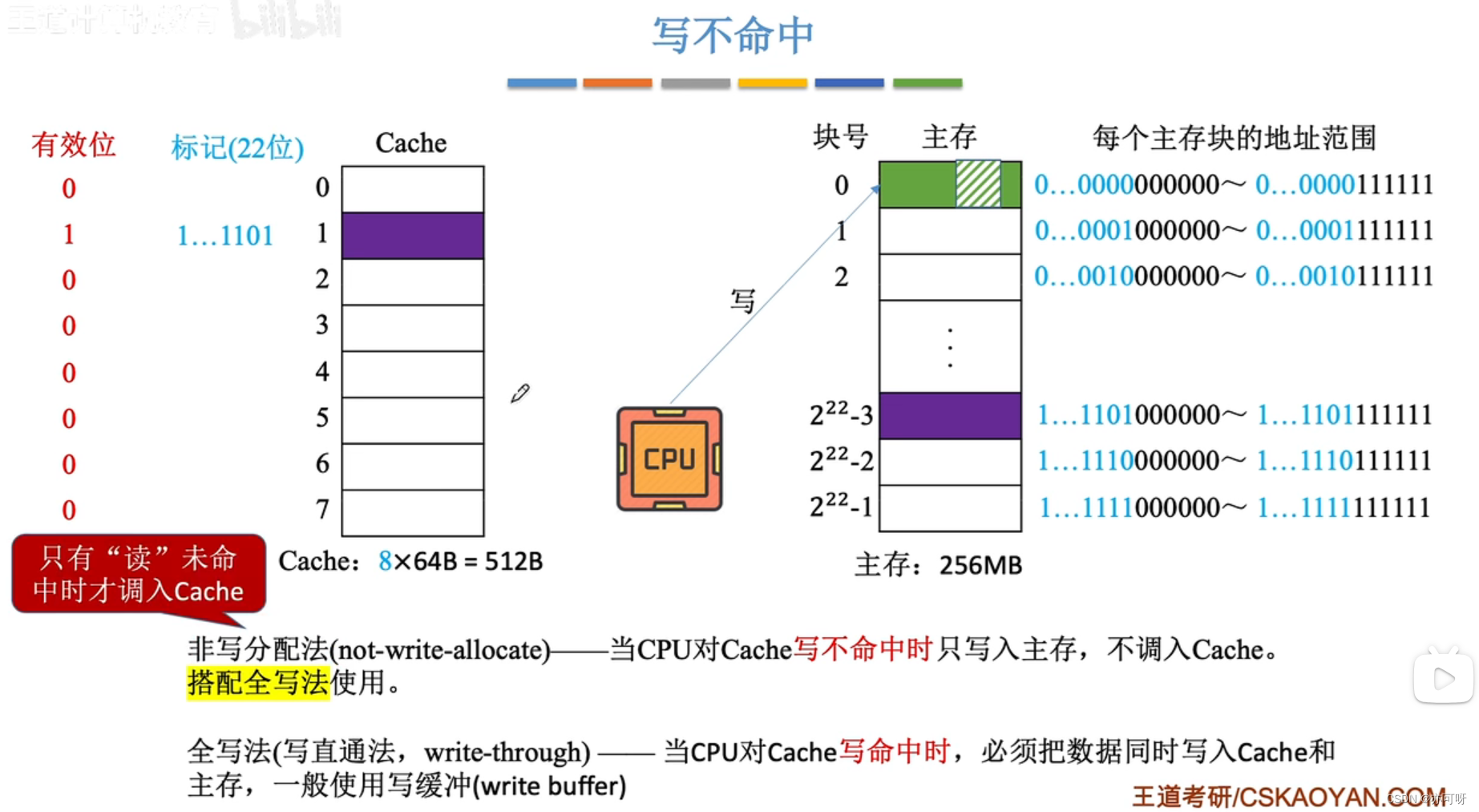

二. 写不命中

\quad

写分配法

\quad

\quad

非写分配法

只有CPU对Cache"读"未命中时才需要把数据从主存调入Cache

\quad

\quad

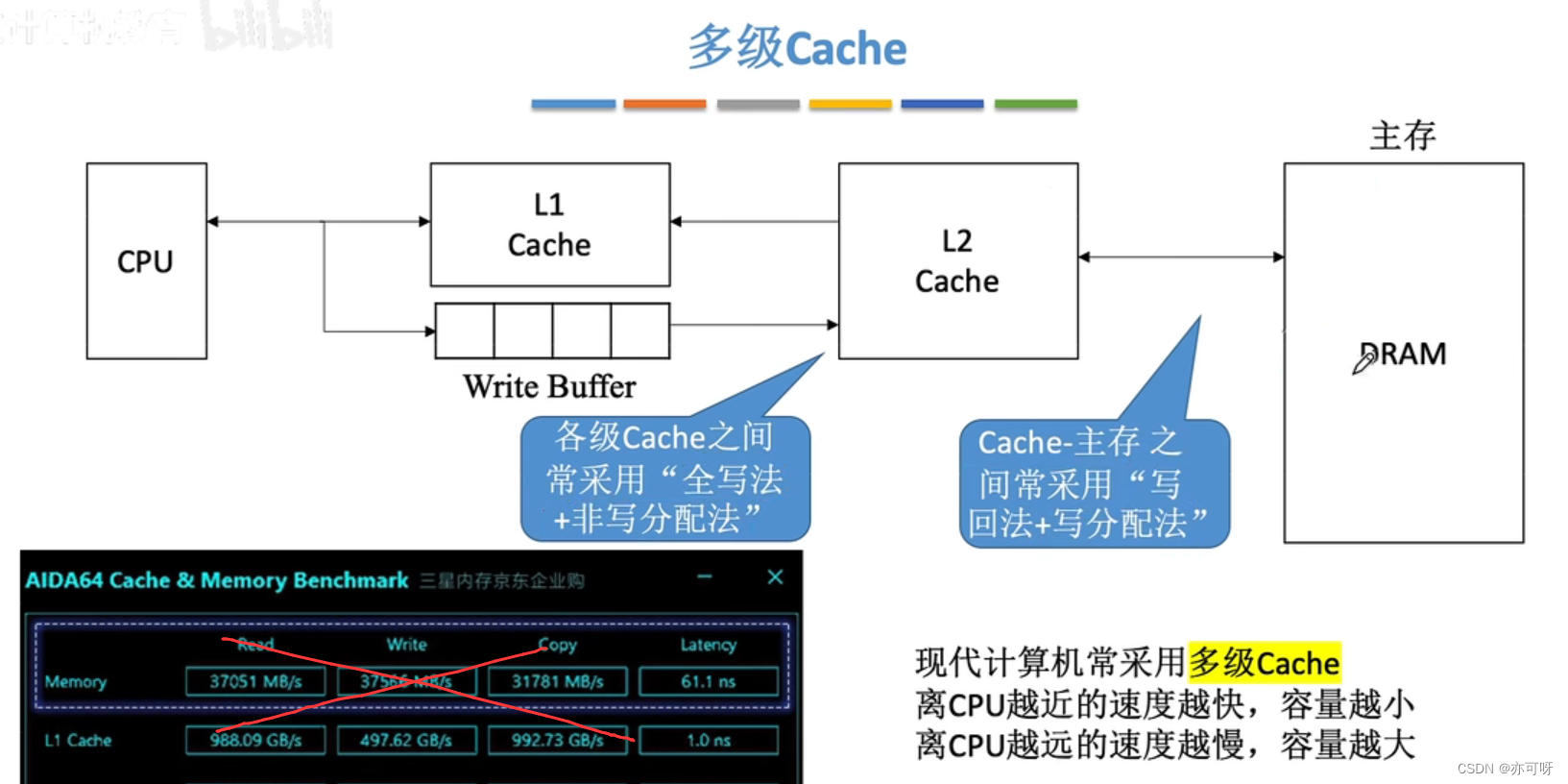

三. 多级Cache(了解即可)

\quad

L2存的是DRAM的一小部分数据的副本, L1存的是L2一小部分数据的副本, 所以是存在数据一致性问题的

\quad

\quad

\quad

\quad

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!