基于FPGA的简易BPSK和QPSK

2023-12-20 06:53:16

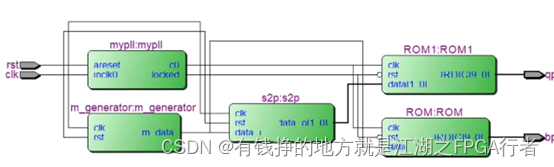

1、框图

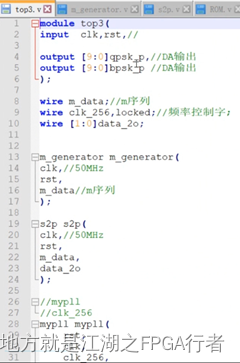

2、顶层

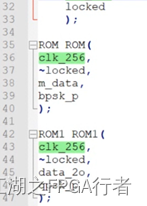

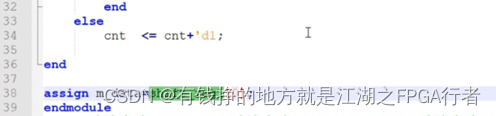

3、m_generator M序列的生成,输出速率为500Kbps

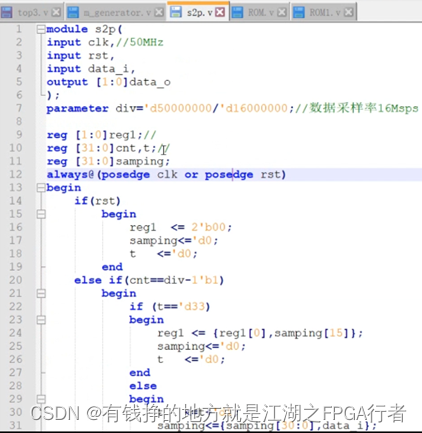

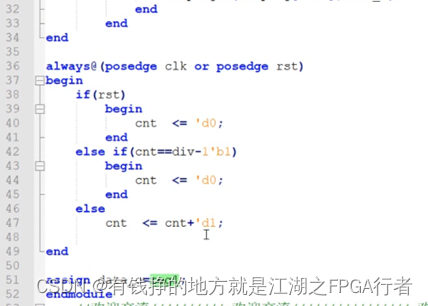

4、S2P是串并转换模块

将1bit的m序列转换到50M时钟下的2bit M序列数据(就有4个象限);

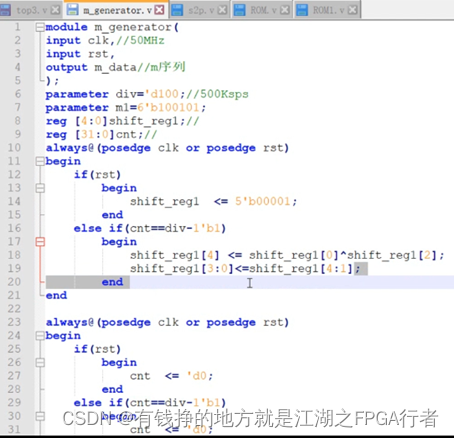

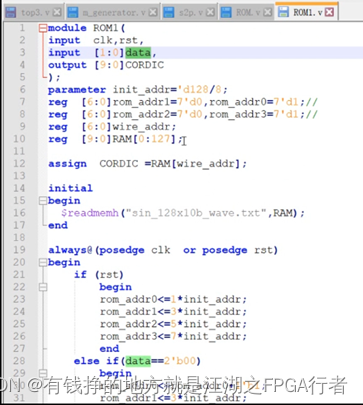

5、my_pll是生成256M的时钟作为载波,因为sin和cos信号的ROM做了256个点;

6、ROM是生成BPSK,只有0和π两个点

7、ROM1是生成QPSK,128个点要输出2M的速率,那么采样的时钟得为256M,所以锁相环生成256M。sin_128x10b_wave.txt可由matlab生成。

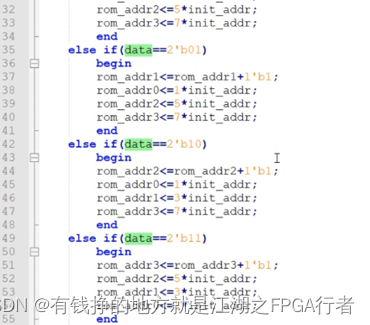

QPSK有4个相位,分别是00:1π/4,01:3π/4,11:5π/4,10:7π/4

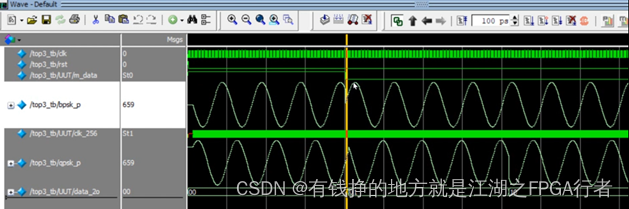

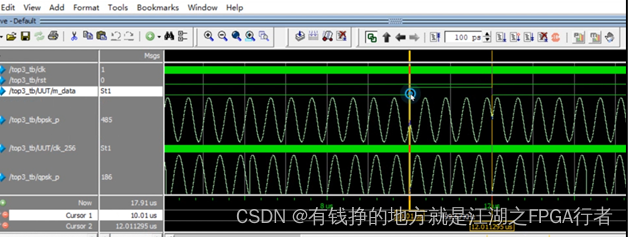

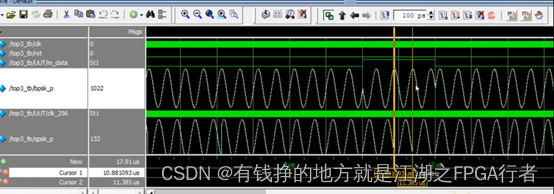

8、仿真

下面是测得码元为500kbps

载波波频测得为2M

测得采样率是16M

文章来源:https://blog.csdn.net/Real003/article/details/135097365

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!