STM32储存器和总线构架

一、引言

本篇文章旨在介绍STM32小容量、中容量和大容量的储存器和系统构架,文中涉及到一些专有名词和概念较为抽象和陌生,建议读者能够查阅相关资料和知识加深了解。

二、正文?

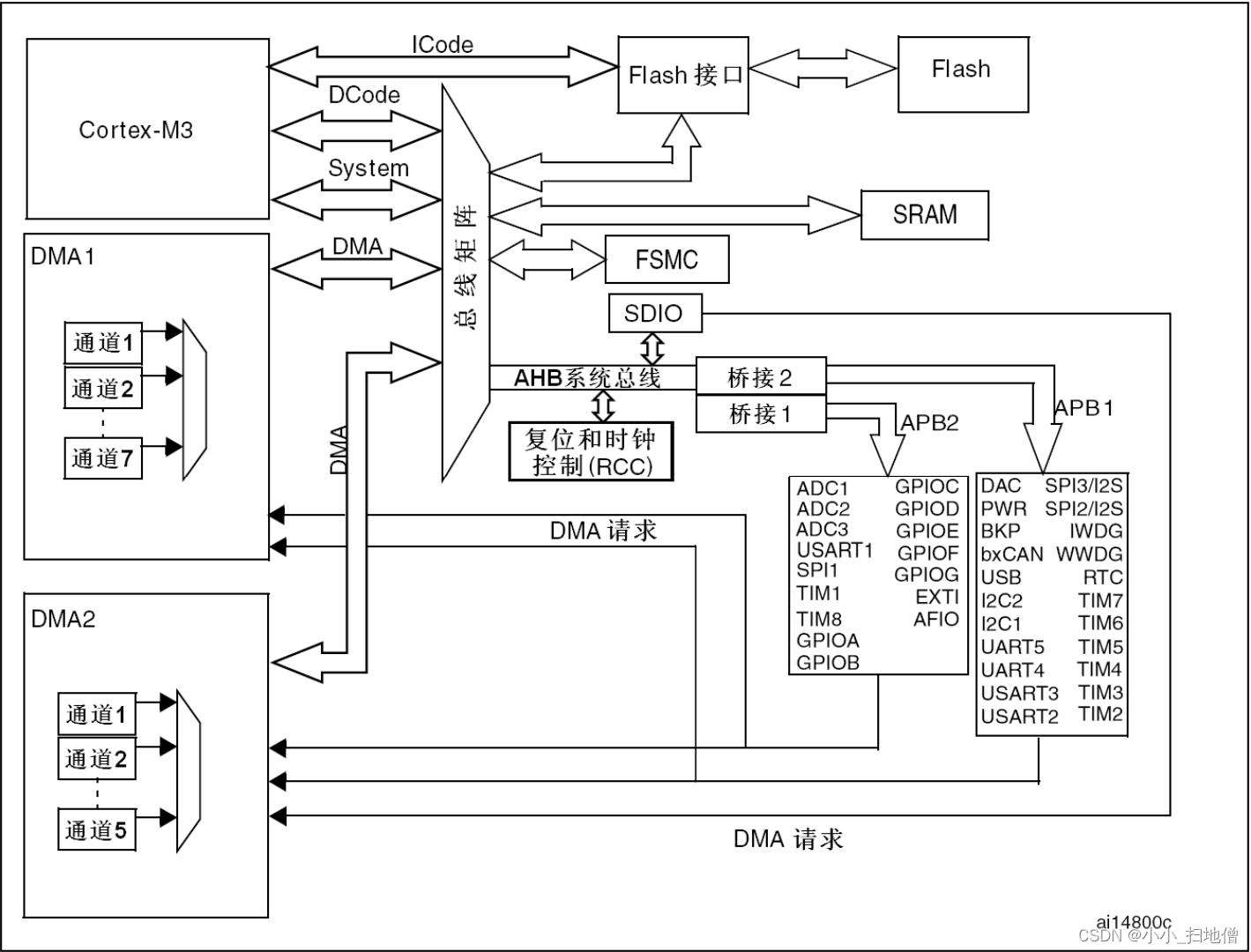

(一)、系统构架

在小容量、中容量和 大容量产品中,主系统由以下部分构成:

● 四个驱动单元:

─ Cortex?-M3内核DCode总线(D-bus)─ 系统总线(S-bus)

─ 通用DMA1和通用DMA2

● 四个被动单元

─ 内部SRAM

─ 内部闪存存储器

─ FSMC

─ AHB到APB的桥(AHB2APBx),它连接所有的APB设备

以上提及到的主系统部分构成都是通过一个多级的AHB总线架构相互连接的。?这是系统结构图:

?在互联型产品中,主系统由以下部分构成:

● 五个驱动单元:

─ Cortex?-M3内核DCode总线(D-bus),和系统总线(S-bus)

─ 通用DMA1和通用DMA2─ AHB到APB的桥(AHB2APBx),它连接所有的APB设备

● 三个被动单元:

─ 内部SRAM

─ 内部闪存存储器─ AHB到APB的桥(AHB2APBx),它连接所有的APB设备

补充:关于以上出现的部分名词,我将对其进行解释?

1、DCode总线(D-bus)

在STM32驱动单元中,DCode总线(D-bus)指的是一种内部总线架构,用于处理指令和数据之间的通信。

DCode总线是STM32微控制器内部的一个重要组成部分,它连接了CPU、存储器以及外设。它被设计用于高效地传输指令和数据,实现与外部设备的通信和数据交换。

通过DCode总线,CPU能够读取和写入存储器中的指令和数据。同时,外设也可以通过DCode总线与CPU进行交互,进行数据的输入和输出操作。

DCode总线具有高带宽和低延迟的特点,这使得STM32微控制器能够快速响应指令和数据的处理需求。它提供了良好的性能和可靠性,为驱动单元的正常运行提供了基础。

需要注意的是,DCode总线只是STM32内部的一个概念,不同系列的STM32微控制器可能会有不同的总线架构和命名方式。因此,在具体的STM32驱动单元中,可能会使用其他名称来描述类似的总线结构。

2、系统总线(S-bus)

在STM32微控制器中,S-Bus(System Bus,系统总线)是一个内部总线架构,用于连接处理器核心、存储器和外设模块之间的通信。

S-Bus提供了高效的数据传输机制,使得CPU能够与系统中的各种模块进行通信和数据交换。它主要用于处理器核心与存储器、DMA控制器以及其他系统级模块之间的数据传输。

通过S-Bus,CPU可以读取和写入存储器中的指令和数据。此外,外设模块也可以通过S-Bus与CPU进行数据的输入和输出操作,实现与外部设备的通信和数据交互。

S-Bus具有高带宽和低延迟的特点,这使得STM32微控制器能够快速响应数据访问需求和系统级操作。它提供了可靠的数据传输通道,确保系统中不同模块之间的协调运作。

需要注意的是,S-Bus只是STM32微控制器内部的一个概念,用于描述系统级总线连接架构。具体的STM32系列和型号可能会有不同的总线架构和名称,但基本原理和功能类似。因此,在具体的STM32系统中,可能会使用其他名称来描述类似的系统总线结构。

ICode总线

该总线将Cortex?-M3内核指令总线与闪存指令接口相连接。指令预取在此总线上完成;

Dcode总线

该总线将Cortex?-M3内核的DCode总线与闪存存储器的数据接口相连接(常量加载和调试访

问);

系统总线

此总线连接Cortex?-M3内核的系统总线(外设总线)到总线矩阵,总线矩阵协调着内核和DMA间的访问。

DMA总线

此总线将DMA的AHB主控接口与总线矩阵相联,总线矩阵协调着CPU的DCode和DMA到

SRAM、闪存和外设的访问。

总线矩阵

总线矩阵协调内核系统总线和DMA主控总线之间的访问仲裁,仲裁利用轮换算法。在互联型产品中,总线矩阵包含5个驱动部件(CPU的DCode、系统总线、以太网DMA、 DMA1总线和

DMA2总线)和3个从部件(闪存存储器接口(FLITF)、 SRAM和AHB2APB桥)。在其它产品中总线矩阵包含4个驱动部件(CPU的DCode、系统总线、 DMA1总线和DMA2总线)和4个被动部件(闪存存储器接口(FLITF)、 SRAM、 FSMC和AHB2APB桥)。AHB外设通过总线矩阵与系统总线相连,允许DMA访问。

AHB/APB桥(APB)

两个AHB/APB桥在AHB和2个APB总线间提供同步连接。 APB1操作速度限于36MHz,APB2操作于全速(最高72MHz)。(注意;这里只是基于STM32F10XXXX)有关连接到每个桥的不同外设的地址映射请参考表1。在每一次复位以后,所有除SRAM和FLITF以外的外设都被关闭,在使用一个外设之前,必须设置寄存器RCC_AHBENR来打开该外设的时钟。

注意: 当对APB寄存器进行8位或者16位访问时,该访问会被自动转换成32位的访问:桥会自动将8位或者32位的数据扩展以配合32位的向量。?

(二)、存储器组织?

程序存储器、数据存储器、寄存器和输入输出端口被组织在同一个4GB的线性地址空间内。

数据字节以小端格式存放在存储器中。一个字里的最低地址字节被认为是该字的最低有效字

节,而最高地址字节是最高有效字节。

可访问的存储器空间被分成8个主要块,每个块为512MB。

(三)存储器映像

嵌入式SRAM

STM32F10xxx内置64K字节的静态SRAM。它可以以字节、半字(16位)或全字(32位)访问。

SRAM的起始地址是0x2000 0000。

SRAM简介

STM32单片机的SRAM是指其内部集成的静态随机存储器(Random Access Memory)。SRAM是一种易失性存储器,能够快速读写数据,但是需要保持电源供应才能保留其中的数据,关机或掉电会导致其中的数据丢失。

不同型号的STM32单片机具有不同容量的SRAM,例如STM32F103C8T6具有20KB的SRAM,而STM32F407VGT6具有192KB的SRAM。 SRAM用于存储程序运行时的变量和栈等数据。 在进行STM32单片机开发时,需要合理地分配SRAM资源,以满足程序运行的需要。

STM32单片机的SRAM在程序设计中具有重要作用,包括以下几个方面:

存储变量和栈:SRAM用于存储代码运行时所需要的各种变量和栈。这些变量可能是程序运行时的临时存储器,也可以是需要长期保留的数据。

数据缓存:SRAM还可用作数据缓存器,提高程序的执行效率。通过将常用的数据缓存在SRAM中,避免了频繁从Flash或外部存储器读取数据的时间开销。

内存映射I/O:某些STM32单片机的外设寄存器会被直接映射到SRAM中,以便于对外设的访问和控制。

DMA传输:DMA(Direct Memory Access)引擎可以直接读写SRAM,使得大量数据传输更加高效,不需要CPU参与其中。

总之,SRAM是STM32单片机内部重要的存储器,直接影响了程序的运行效率、稳定性和数据存储能力。理解SRAM的特点和使用方法,能够有效提升系统性能、降低功耗,并优化代码设计。

?位段

Cortex?-M3存储器映像包括两个位段(bit-band)区。这两个位段区将别名存储器区中的每个字映射到位段存储器区的一个位,在别名存储区写入一个字具有对位段区的目标位执行读-改-写操作的相同效果。

在STM32F10xxx里,外设寄存器和SRAM都被映射到一个位段区里,这允许执行单一的位段的写和读操作。

下面的映射公式给出了别名区中的每个字是如何对应位带区的相应位的:

bit_word_addr = bit_band_base + (byte_offset× 32) + (bit_number× 4)

其中:

bit_word_addr是别名存储器区中字的地址,它映射到某个目标位。

bit_band_base是别名区的起始地址。

byte_offset是包含目标位的字节在位段里的序号

bit_number是目标位所在位置(0-31)

例子:

下面的例子说明如何映射别名区中SRAM地址为0x20000300的字节中的位2:

0x22006008 = 0x22000000 + (0x300× 32) + (2× 4).

对0x22006008地址的写操作与对SRAM中地址0x20000300字节的位2执行读-改-写操作有着相同的效果。

?嵌入式闪存

高性能的闪存模块有以下的主要特性:

● 高达512K字节闪存存储器结构:闪存存储器有主存储块和信息块组成:

─ 主存储块容量:

小容量产品主存储块最大为4K× 64位,每个存储块划分为32个1K字节的页(见表2)。

中容量产品主存储块最大为16K× 64位,每个存储块划分为128个1K字节的页(见表3)。

大容量产品主存储块最大为64K× 64位,每个存储块划分为256个2K字节的页(见表4)。

互联型产品主存储块最大为32K× 64位,每个存储块划分为128个2K字节的页(见表5)。

─ 信息块容量:

互联型产品有2360× 64位(见表5)。

其它产品有258× 64位(见表2

30/754、 表3、 表4)。

闪存存储器接口的特性为:

● 带预取缓冲器的读接口(每字为2× 64位)

● 选择字节加载器

● 闪存编程/擦除操作

● 访问/写保护

?闪存的读取

闪存的指令和数据访问是通过AHB总线完成的。预取模块是用于通过ICode总线读取指令的。仲裁是作用在闪存接口,并且DCode总线上的数据访问优先。

读访问可以有以下配置选项:

● 等待时间:可以随时更改的用于读取操作的等待状态的数量。

● 预取缓冲区(2个64位):在每一次复位以后被自动打开,由于每个缓冲区的大小(64位)与闪

存的带宽相同,因此只通过需一次读闪存的操作即可更新整个缓冲区的内容。由于预取缓

冲区的存在, CPU可以工作在更高的主频。 CPU每次取指最多为32位的字,取一条指令

时,下一条指令已经在缓冲区中等待。

● 半周期:用于功耗优化。

注: 1. 这些选项应与闪存存储器的访问时间一起使用。等待周期体现了系统时钟(SYSCLK)频率与闪存访问时间的关系:

0等待周期,当 0 < SYSCLK < 24MHz

1等待周期,当 24MHz < SYSCLK ≤ 48MHz

2等待周期,当 48MHz < SYSCLK ≤ 72MHz

2 . 半周期配置不能与使用了预分频器的AHB一起使用,时钟系统应该等于HCLK时钟。该特性只能用在时钟频率为8MHz或低于8MHz时,可以直接使用的内部RC振荡器(HSI),或者是主振荡器(HSE),但不能用PLL。

3. 当AHB预分频系数不为1时,必须置预取缓冲区处于开启状态。

4. 只有在系统时钟(SYSCLK)小于24MHz并且没有打开AHB的预分频器(即HCLK必须等于

SYSHCLK)时,才能执行预取缓冲器的打开和关闭操作。一般而言,在初始化过程中执行预取缓冲器的打开和关闭操作,这时微控制器的时钟由8MHz的内部RC振荡器(HSI)提供。

5. 使用DMA: DMA在DCode总线上访问闪存存储器,它的优先级比ICode上的取指高。 DMA在每次传送完成后具有一个空余的周期。有些指令可以和DMA传输一起执行。

编程和擦除闪存?

闪存编程一次可以写入16位(半字)。

闪存擦除操作可以按页面擦除或完全擦除(全擦除)。全擦除不影响信息块。

为了确保不发生过度编程, 闪存编程和擦除控制器块是由一个固定的时钟控制的。

写操作(编程或擦除)结束时可以触发中断。仅当闪存控制器接口时钟开启时,此中断可以用来从WFI模式退出。

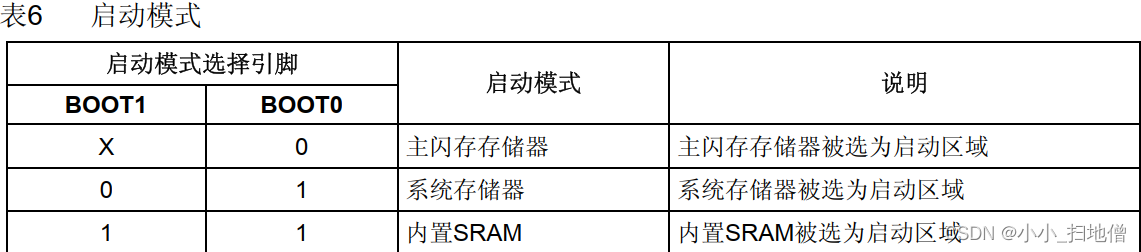

(四)、启动配置?

在STM32F10xxx里,可以通过BOOT[1:0]引脚选择三种不同启动模式。

在系统复位后, SYSCLK的第4个上升沿, BOOT引脚的值将被锁存。用户可以通过设置BOOT1和BOOT0引脚的状态,来选择在复位后的启动模式。

在从待机模式退出时, BOOT引脚的值将被被重新锁存;因此,在待机模式下BOOT引脚应保持为需要的启动配置。在启动延迟之后, CPU从地址0x0000 0000获取堆栈顶的地址,并从启动存储器的0x0000 0004指示的地址开始执行代码。因为固定的存储器映像,代码区始终从地址0x0000 0000开始(通过ICode和DCode总线访问),而数据区(SRAM)始终从地址0x2000 0000开始(通过系统总线访问)。 Cortex-M3的CPU始终从ICode总线获取复位向量,即启动仅适合于从代码区开始(典型地从Flash启动)。

STM32F10xxx微控制器实现了一个特殊的机制,系统可以不仅仅从Flash存储器或系统存储器启动,还可以从内置SRAM启动。

?(五)、结语

以上就是我对STM32F10XXX存储器和总线架构的学习和了解,文中涉及到一些名词较为陌生和抽象,我在最初学习的时候也是倍感无聊和痛苦,不过经过我查阅相关资料和文档,感觉静下心来学完后,还是受益匪浅的。故写此总结,与渴望知识的我们共享!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!