英诺赛科PCB layout 设计案列分享1----高压单管

2024-01-08 17:02:59

Layout设计中的几个关键步骤是布局、走线、铺铜、散热,英诺赛科高压单管GaN的Layout设计也不例外。

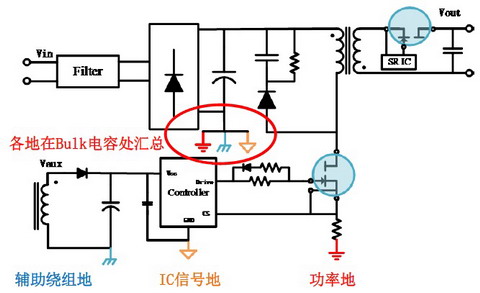

反激拓扑是高压单管GaN的典型应用,快充场合常用。该拓扑在地线的处理上都需特别注意,如下图所示,Layout时辅助绕组地、IC信号地功率地在bulk电容处汇合,避免IC地受干扰导致驱动振荡。

在GaN应用时,Layout上还需注意以下方面:

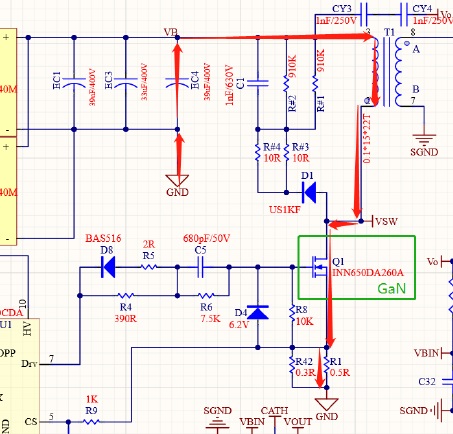

1) 由于电流检测电阻的存在,此种场合GaN的开尔文脚与源极直接连接,否则电流采样电阻失去作用。

2) Source端与bulk电容地的走线尽可能短、粗,减小寄生电感LS。

3) 驱动电路和功率电路分开布置,避免干扰

4) 驱动IC及驱动电路尽量靠近GaN一些,减小驱动回路的走线和面积

5) 高压场合,GaN的漏源极交叠铜皮的寄生电容尽量小,以优化开关loss。

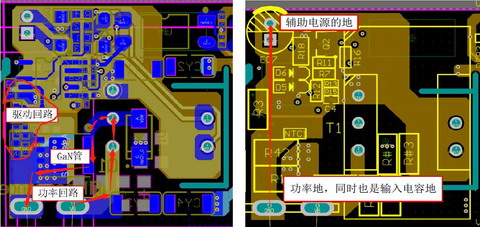

下面为DFN封装的高压GaN在65W快充应用中的layout案例:

QR反激拓扑,GaN在高网下无法零电压开通,GaN的漏极和源极的铺铜如果形成寄生电容,会额外增大开通loss,该案例的Layout中避免了该问题,由左图可见。同时,GaN的功率回路和驱动回路在布局上较好的分开,避免了功率电路对驱动电路的干扰。

另由图可见,通过中间层的大铺铜将辅助电源的地和功率的地线相连,地线的处理干净清晰.

文章来源:https://blog.csdn.net/wpgddt/article/details/135459018

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!