年度总结|存储随笔2023年度最受欢迎文章榜单TOP15-part2

TOP11:PCIe在狂飙,SAS存储之路还有多远?

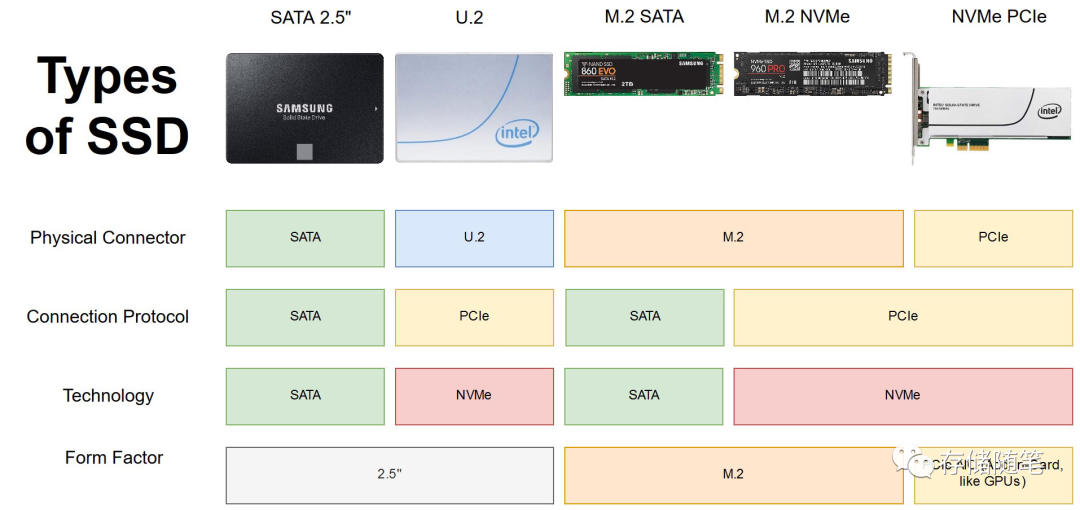

随着科技的飞速发展,固态硬盘(SSD)已经成为现代计算机系统中不可或缺的一部分。它以其出色的性能和可靠性,改变了我们对于存储设备的期待。当前业内SSD广泛应用,接口协议也有多样性,常见的SSD的接口协议归纳如下图:

SATA/SAS协议不可避免走向被NVME逐步替代的历史进程,滚滚车轮,不可阻挡!

TOP12:SSD数据在写入NAND之前为何要随机化?

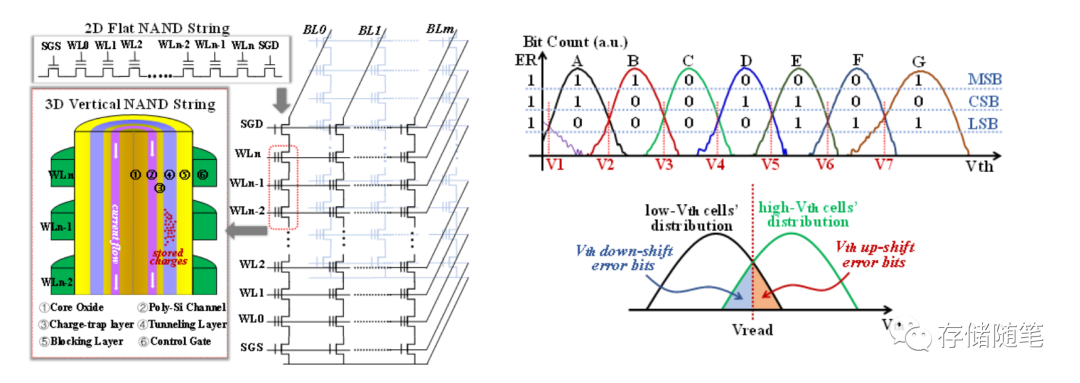

以TLC 3D NAND为例,当一个存储单元需要存储多位信息时,这些位会被赋予不同的编程延迟,以允许在相同单元内区分它们。

在这种情况下,LSB、CSB和MSB是根据它们的编程延迟来定义的:

-

LSB (Least Significant Bit):最低有效位,这是在同一个存储单元中编程延迟最小的位。对于3位的TLC NAND闪存来说,LSB通常是第一个被写入的位,因为它的编程阈值最低。

-

CSB (Central Significant Bit):中央有效位,位于LSB和MSB之间,其编程延迟介于两者之间。在某些编程模式下,CSB可能是在LSB之后紧接着被编写的位。

-

MSB (Most Significant Bit):最高有效位,具有最高的编程阈值,在同一存储单元中的编程延迟最大。因此,它是最后被编写的位。

TOP13:SSD基础架构与NAND IO并发问题探讨

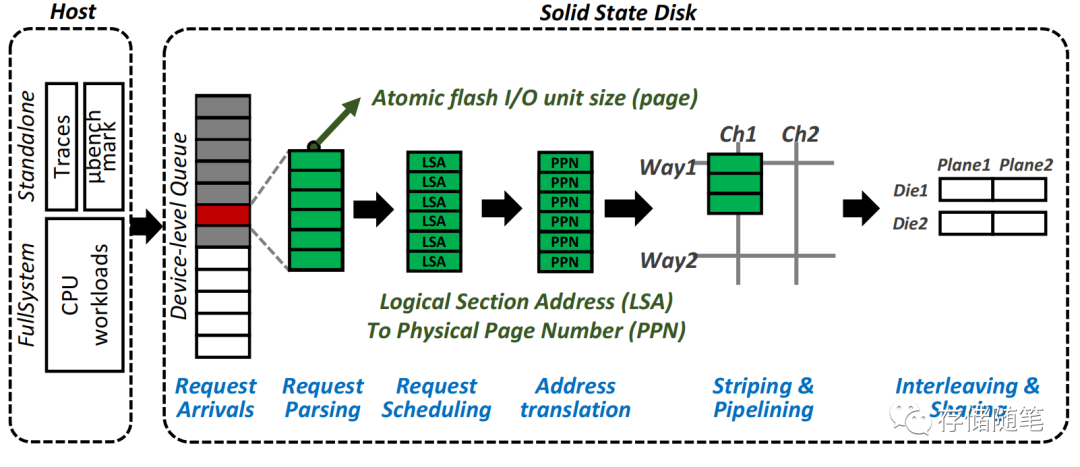

Host下发IO,到SSD内部的处理逻辑如下图。这里面核心点,IO逻辑地址LSA(或者叫LBA),到真正最后落入NAND,还有一层FTL转化为了NAND的物理地址PPN(或者叫做PBA)。为了提升固态硬盘(SSD)的性能,NAND相关的并发访问优化是关键因素之一。

TOP14:过度加大SSD内部并发何尝不是一种伤害

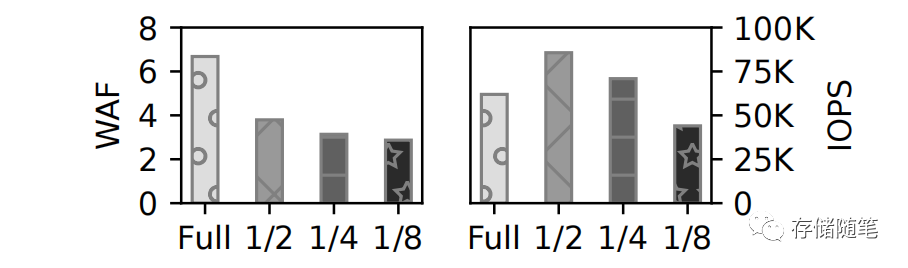

文章开始,结合SSD并发与写放大的关联,抛出一个观点:SSD中的过度并发实际上是有害的。例如,同时运行四个FIO线程,将不同特性的数据写入具有不同内部并发的SSD,实验结果显示:

-

随着并行性从1/8增加到全并行发,写放大因子(WAF)增加到230%。

-

反常的是,全并行并没有实现最高的吞吐量,因为高WAF导致半并发配置的吞吐量几乎比全并行高出40%。

TOP15:浅析LDPC软解码对SSD延迟的影响

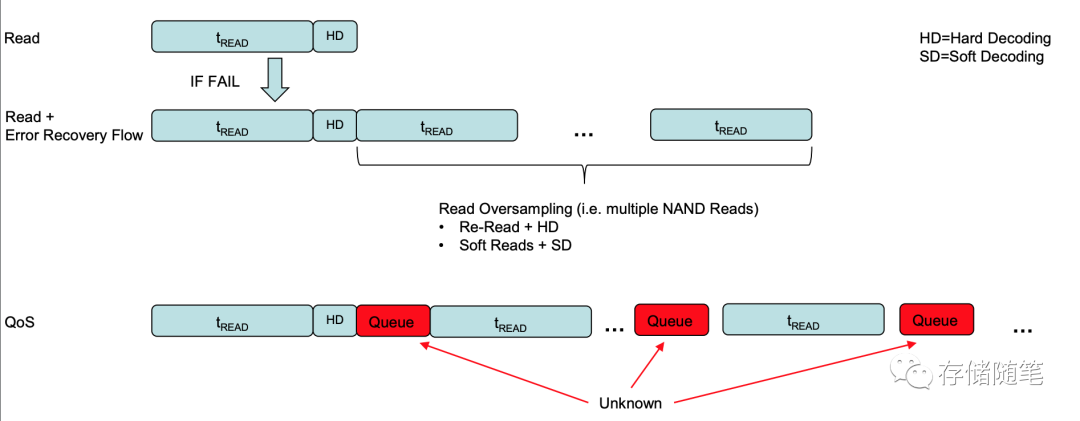

在host读取数据过程中,最理想的情况是一个Page Read Time的时间就可以直接返回数据。但显示的情况是,我们可能会因为一些不想看到的问题,导致性能受损。这个读取过程中,NAND相关问题的纠错对延迟也有很大的影响。

此外,2023年度,小编针对部分深度挖掘分析的内容,输出了3篇付费文章(介意这部分内容的同学,可以忽略):

小编每日撰文不易,如果您看完有所受益,欢迎点击文章底部左下角“关注”并点击“分享”、“在看”,非常感谢!

精彩推荐:

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!