ADS学习笔记(二)——更新中

八、中途容性负载的时延累加

1.原理简述

中途容性负载产生的第一位影响就是下冲噪声,第二位影响是远端信号的接收时间被延迟。电容器与传输线的组合就像一个RC滤波器,所以传输信号10%~90%上升边将增加,信号越过电压门限50%的时间也将推后。传输信号10%~90%上升边约为:

RT=2.2RC=ZoC? (8-1)

传输信号通过电压门限50%的时延增加量(时延累加)为ATD(ns)为:

ATD=RC=0.5ZoC? (8-2)

RT表示上升边的10%~90%(ns),Zo为传输线特性阻抗(Ohm),C为容性突变(nF)。使用图7.1的模型进行仿真,观察中途容性负载取不同电容值时造成的时延。

2.仿真条件

驱动器:阶跃电源VtStep,上升时间100ps,幅值为1V

驱动器内阻:10Ohm

源端端接电阻:40Ohm

时域扫描:结束时间60ns,步长0.01ns

TLD1、TLD2特性阻抗均为50Ohm,时延为1ns的传输线

终端负载输入电阻可看作开路

3.仿真结果

图8.1传输信号上升边(原始信号上升边100ps)

如图8.1,根据图像粗略估算,2pF、4pF、6pF、8pF、10pF的电容器对应的时延累加分别为50ps、150ps、250ps、350ps、450ps,与式8-2的结论不一致?——待更新

九、有载线

1.原理简述

当传输线上存在一个小的容性负载时,信号将失真,信号上升边也将退化。若传输线上每隔一段距离就分布一个电容,且间距小于上升边的空间延伸,则每个容性突变处引起的反射就会相互抵消:其效果相当于降低了传输线的特性阻抗。而其上均匀分布容性负载的传输线就被称为有载线。

有载传输线线仿真模型如图9.1所示,无载传输线线仿真模型如图9.2所示。

图9.1有载传输线线仿真模型

图9.2无载传输线线仿真模型

2.仿真条件

2.1有载线模型

驱动器:阶跃电源VtStep,上升时间1ns,幅值为1V

驱动器内阻:理想电源无内阻

时域扫描:结束时间60ns,步长0.01ns

TLD27~TLD32特性阻抗均为50Ohm,时延为0.167ns的传输线(相当于1in传输线)

C1~C5电容值均为3pF,模拟传输线上单位长度上的分布电容

终端负载输入电阻可看作开路

2.2无载线模型

驱动器:阶跃电源VtStep,上升时间1ns(不同仿真有所调整),幅值为1V

驱动器内阻:理想电源无内阻

时域扫描:结束时间60ns,步长0.01ns

TLD26特性阻抗均为50Ohm,时延为1ns的传输线

源端端接电阻为50Ohm

终端负载输入电阻可看作开路

3.仿真结果

图9.3无载线和有载线传输信号

当信号源上升时间为1ns,端接电阻均为50Ohm时,有载线和无载线传输信号如图9.3,可见此时有载线的传输信号比无载线的幅值小,可知此时有载线的端接电阻偏大,即有载线上的分布电容引起了有载线特性阻抗的降低。

十、感性突变的反射

1.原理简述

连接到传输线上的任何串联连接都有一些相应的串联回路电感。而这种电感的突变会对近端信号造成非单调变化(先升后降),而在远端使传输信号出现过冲。当信号的上升沿通过电感器时,则电感阻抗为:

Z=V/I=(L*dI/dt)/I=L/RT? (10-1)

Z为电感阻抗(Ohm),L为突变处串联电感值(nH),RT为信号上升边(ns)

因为要保证反射信号约为信号摆幅的10%,所以分立电感器引起的串联阻抗突变引起的增量小于导线阻抗的20%,因此可得经验法则:

Lmax <0.2*Zo*RT? (10-2)

Zo为传输线特性阻抗(Ohm),Lmax为最大串联电感值(nH),RT为信号上升边(ns)

可以建立如下仿真模型:

图10.1感性突变的反射仿真模型

2.仿真条件

驱动器:阶跃电源VtStep,上升时间1ns,幅值为1V:

驱动器内阻:10Ohm;

源端端接电阻:40Ohm:

时域扫描:结束时间6ns,步长0.01ns:

TLD33、TLD34特性阻抗均为50Ohm,时延为1ns的传输线:

终端负载输入电阻可看作开路。

3.仿真结果

图10.2串联电感值为0nH\5nH\10nH时的反射信号(左)和传输信号(右)

改变串联电感值,使其分别等于0、5nH、10nH,对应的反射信号和传输信号如图10.2所示。可知随着电感值的增加,信号过冲幅值逐渐增加,传输信号的时延逐渐增加。当电感值为10nH时,反射信号,传输信号过冲幅值基本等于传输信号稳态值的10%。因此可以认为当特性阻抗50Ohm,信号上升边1ns时,可容许最大串联电感值为10nH。符合式10-2中的结论。

图10.3不同串联电感值下的时延累加(信号源上升边为50ps)

当信号源上升边为50ps时,串联电感值分别为0、5nH、10nH时,传输信号的延时累加如图10.3所示,其对应的时延累加为0、50ps、100ps(待更新),与式(10-4)结论相符。

十一、补偿

1.原理简述

设计中常需要使用到专用连接件,电路中串联回路电感不可避免。因此需要采用补偿技术来控制串联回路电感产生的反射噪声。如图11.1所示,补偿方法为在连接件(串联回路电感L4)的两端并接补偿电容C2、C3,使连接件如同传输线的一部分,从而消除反射噪声。

补偿电容的计算方法为:

C=L1/Z^2?(11-1)

其中C为补偿电容(nF),L1为连接件电感(nH),Z为传输线特性阻抗(Ohm):

而最佳的接法为将补偿电容C分为两部分加载电容的两侧,即令C2=C3=0.5C。

图11.1补偿仿真模型

2.仿真条件

驱动器:阶跃电源VtStep,上升时间1ns,幅值为1V

驱动器内阻:10Ohm

源端端接电阻:40Ohm

时域扫描:结束时间20ns,步长0.01ns

L1电感值10nH

C2、C3均2pF

TLD39、TLD40特性阻抗均为50Ohm,时延为1ns的传输线

终端负载输入电阻可看作开路

3.仿真结果

图11.2分别在有连接件(蓝)、无连接件(红)、补偿情况(紫)的源端信号(左)和接收端信号(右)

如图11.2所示,有连接件未补偿情况下的接收端信号和源端信号相比无连接件信号,均出现了过冲,而补偿后的接收端信号和源端信号,反射噪声得到了抑制,较小的波动可以忽略,基本与无连接件信号重合。这说明补偿确实可以抑制感性突变对信号带来的不良影响。

十二、串扰仿真

1.原理阐述

串扰(Crosstalk)是四类信号完整性问题之一,指的是有害信号从一个线传递到相邻线。任何一对线之间都存在串扰。通常我们把噪声源所在的线称为动态线或攻击线,而把有噪声形成的线称为静态线或受害线。静态线上的靠近驱动源的一端称为近端,远离驱动端的一端称为远端,NEXT系数代指近端串扰(静态线上近端噪声峰值/动态线上信号电压),FEXT系数代指远端串扰(静态线上远端噪声峰值/动态线上信号电压)。经验法则:最大容许串扰约是信号摆幅的5%。

图12.1·近端噪声和远端噪声时间关系图

TD指的是耦合区域的时延,近端噪声持续时间是2*TD-RT,远端噪声持续时间是RT,近端噪声幅度随着耦合长度增加而增加,最终达到饱和,在饱和长度之前,有串扰率/饱和时串扰率=耦合长度L/饱和长度,近端串扰饱和长度计算公式:1/2*RT*v。远端噪声的峰值与耦合长度成比例,同时随着上升时间减小,远端噪声的脉冲宽度也减小,而峰值增加。

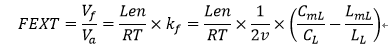

FEXT的计算关系式如下:

其中,FEXT表示远端串扰系数,Len表示耦合长度,RT表示上升时间, 表示信号传播速度,CmL 表示单位长度互容C12,CL表示信号路径上单位长度电容C11,LmL表示单位长度互感L12,LL表示信号路径上单位长度电感L11。

对于理想带状线:导线周围介质材料是同质且均匀分布,那么相对容性耦合和相对感性耦合完全相同,不会出现远端串扰。

以下为ADS串扰仿真模型:

图12.2串扰仿真模型

2.仿真条件

驱动器:阶跃电源VtStep,上升时间0.1~0.5ns,幅值0.2V

终端负载电阻:50Ohm

耦合长度:500~4000mil,步进500mil

时域扫描:结束时间5ns,步长=(上升时间/3)ns

层叠:使用ADS默认的四层板层叠

3.仿真结果

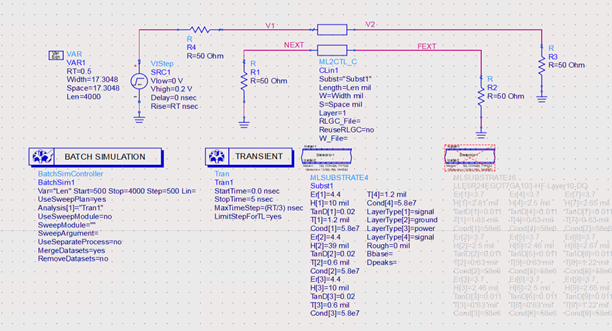

设置线宽为17.3048mil,线间距为17.3048mil(50Ω单端,1倍线宽),设置耦合长度为4000mil(大于理论饱和长度≈1/2*0.5ns*6in/ns=1500mil)。如下图,NEXT=4mV,根据4000mil的仿真结果反推TD约为0.6085ns(与理论TD=耦合长度/6in/ns=4mil/6in/ns=0.667ns相近),反推饱和长度为1600mil(与理论饱和长度1500mil相近)。

图12.3 走线间距为1倍线宽,RT=0.1ns,耦合长度逐步增加串扰图

如图12.3,耦合长度为1000mil时(小于饱和长度),此时近端噪声峰值小于NEXT,为2.479mV。耦合长度为500mil时,近端噪声峰值为1.254mV(可以发现近端噪声在耦合长度小于饱和长度时,实际噪声峰值与耦合长度与饱和长度的比值成比例)。而远端噪声随着耦合长度增加成比例增加,没有饱和长度。

更改线间距为51.9144mil(3倍线宽)时,可以看到近端和远端串扰大幅降低:

图12.4 走线间距为3倍线宽,RT=0.1ns,耦合长度逐步增加串扰图

更改上升时间RT为0.1~0.5ns,步进0.1ns,可以发现当上升时间变短时近端噪声峰值基本没变,远端串扰脉冲宽度减小,同时峰值增加:

图12.5 走线间距为1倍线宽,耦合长度为4000mil,RT=0.1~0.5ns串扰图

减小近端串扰方法:

①增大线间距②靠近返回平面③减小耦合长度(小于饱和长度)④使用防护布线(带状线)

减小远端串扰方法:

①增大线间距②靠近返回平面③减小耦合长度④拉长上升边⑤在表面层导线上方加介质材料⑥将敏感线布成带状线⑦使用防护布线(带状线)

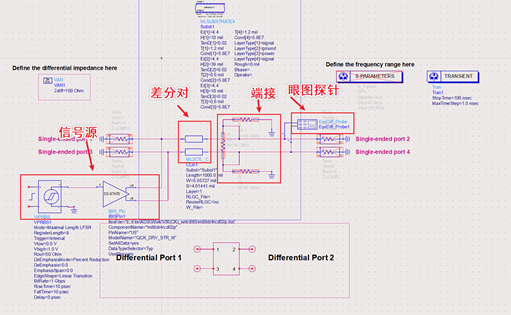

十三、差分对端接

1.原理简述

端接共模信号不是消除共模信号,只是阻止共模信号在电路之间往返振荡,端接的办法有4种。

第一种办法是π型端接,在每条信号线与返回路径之间接上一个电阻器,这两个电阻器并联时的阻值应等于共模阻抗。

图13.1 差分对π型端接结构

共模信号受到的等效电阻为两个电阻器R2的并联,差分信号受到的等效电阻为两个电阻器R2串联后再和电阻器R1并联。对于典型的紧耦合差分对而言,奇模阻抗大致为50Ω,偶模阻抗大致为55Ω,此时两条信号线之间的电阻值R1应为1kΩ,每条线与返回路径之间的电阻R2为55Ω。这种方式能同时端接100Ω差分阻抗和27.5Ω共模阻抗。

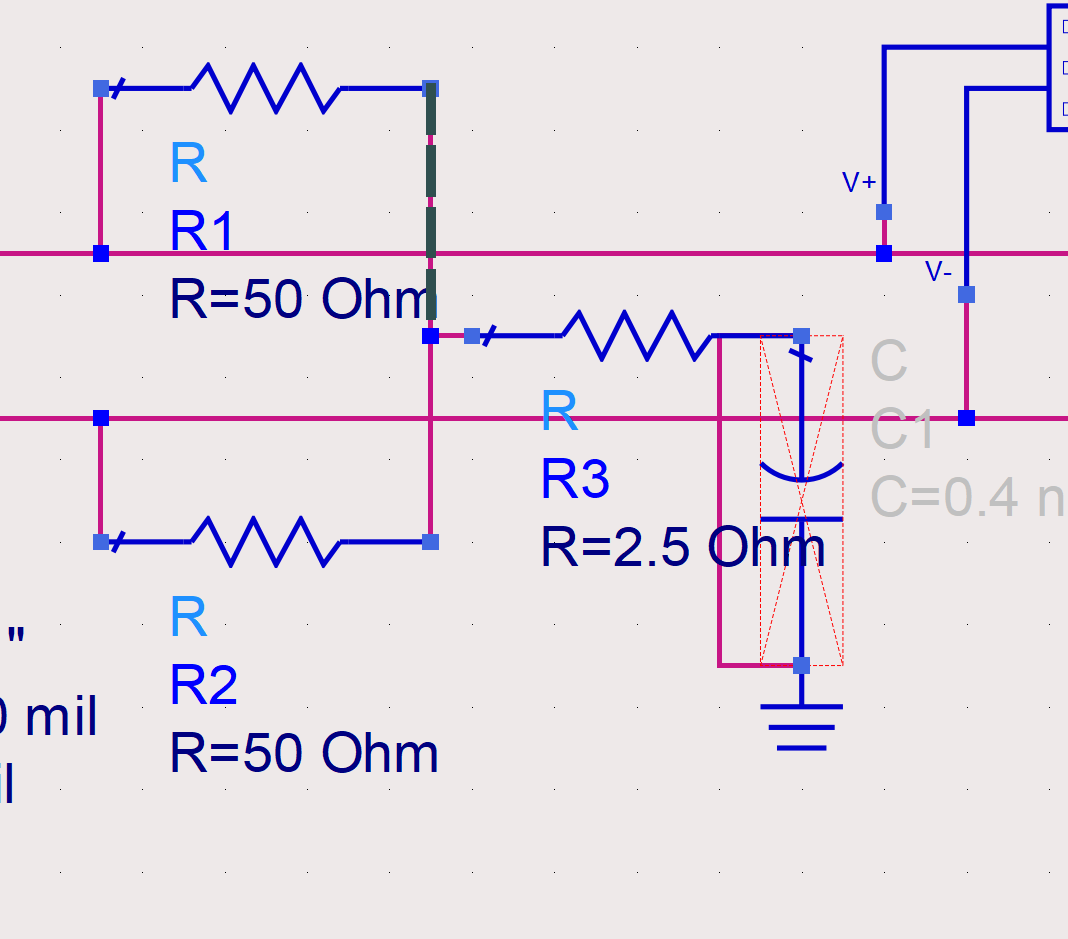

第二种办法是T型端接,差分信号受到的等效电阻是两个电阻器R1的串联,共模信号受到的等效电阻是两个电阻器R1并联后再和R2串联。对于典型的紧耦合差分对而言,T型端接中R1为50Ω,中央抽头与返回路径之间的电阻器为2.5Ω。

图13.2 差分对T型端接结构

第三种是在T型端接中加入隔直流电容,选择电容要保证共模信号受到的时间常数(RC)远大于信号中的最低频率分量所对应周期的数值,保证在信号最低频率分量内电容器的阻抗小于电阻器的阻抗。作为一阶估计,电容初步选择:

![]()

![]()

![]() 表示共模阻抗,例如共模阻抗为25Ω,上升边为0.1ns,那么隔直流电容约为10ns/25Ω=0.4nF。

表示共模阻抗,例如共模阻抗为25Ω,上升边为0.1ns,那么隔直流电容约为10ns/25Ω=0.4nF。

第四种办法是直接将每个信号线通过50Ω电阻端接到VTT电源,这一方案优点提供了良好的差分信号端接、适当的共模信号端接,以及良好的功耗,而且可以针对芯片上的阻抗端接。

2.仿真条件

使用DeignGuide中信号完整性应用的4port仿真做为模板修改,这样可以节省很多时间,当然照着模板自己搭建也没有问题

图13.3 差分对仿真条件(Ⅰ)

图13.4 差分对仿真条件(Ⅱ)

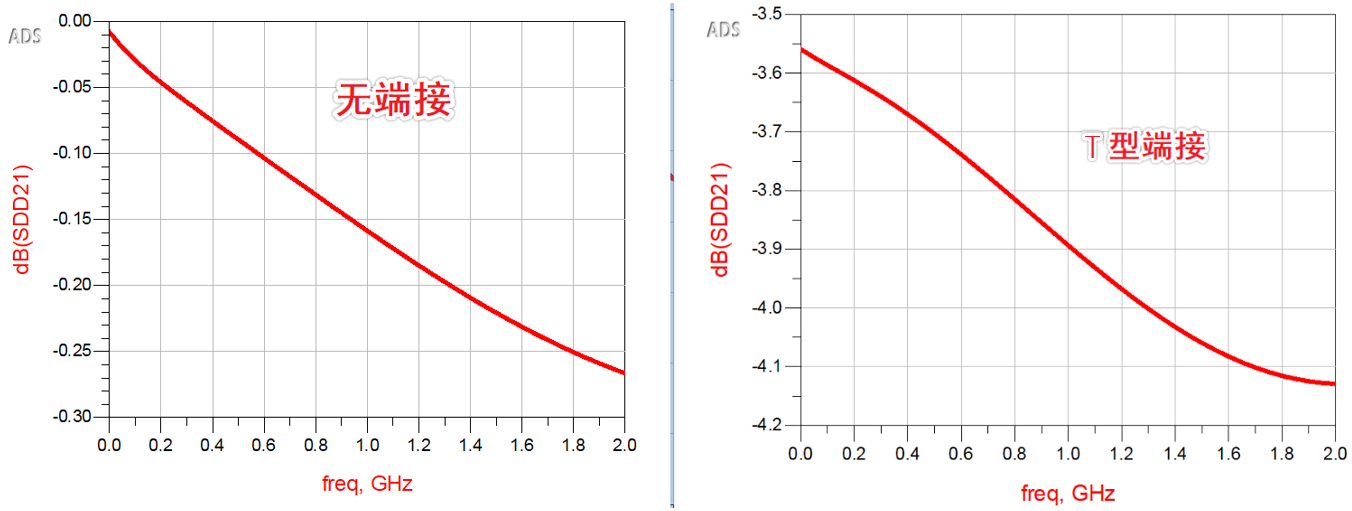

3.仿真结果

图13.5 π型端接仿真结果(Ⅰ)

图13.6 π型端接仿真结果(Ⅱ)

可以看到在π型端接结构下,差分对眼图有明显改善,反射减小了,但是信号被端接电阻分压,插损增大。

图13.7 T型端接仿真结果(Ⅰ)

图13.8 T型端接仿真结果(Ⅱ)

可以看到在T型端接结构下,差分对眼图有明显改善,反射减小了,但是信号被端接电阻分压,插损增大。

图13.9 T型端接中加入隔直流电容

可以看到增加隔直流电容波形没有明显变化

图13.10 VTT端接仿真结果(Ⅰ)

图13.11 VTT端接仿真结果(Ⅱ)

可以看到VTT端接结果与π、T型端接相似

?十四、有损传输线的损耗

1.原理简述

待更新

2.仿真条件

待更新

3.仿真结果

待更新

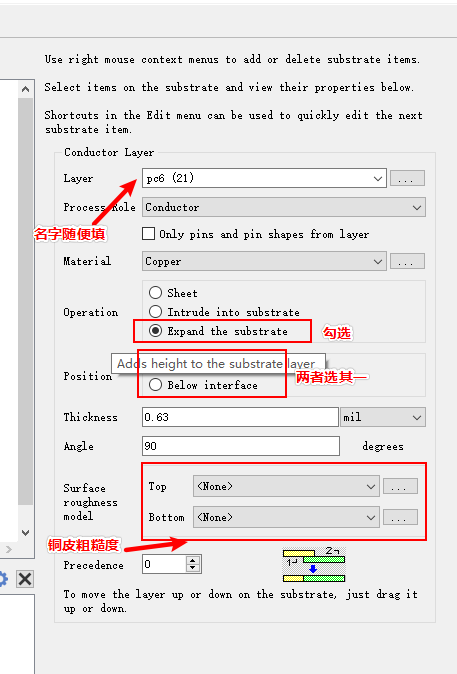

十五、过孔建模

1.原理简述

普通过孔呈容性,信号经过时会出现阻抗下跌并引起反射,因此高速信号对过孔进行建模仿真和补偿也是相当重要的。

2.仿真条件

工具:ADS Via Designer过孔建模模块,Via Designer调用的是ADS EMPro仿真引擎,采用FEM(三维全波有限元法)。

3.仿真结果

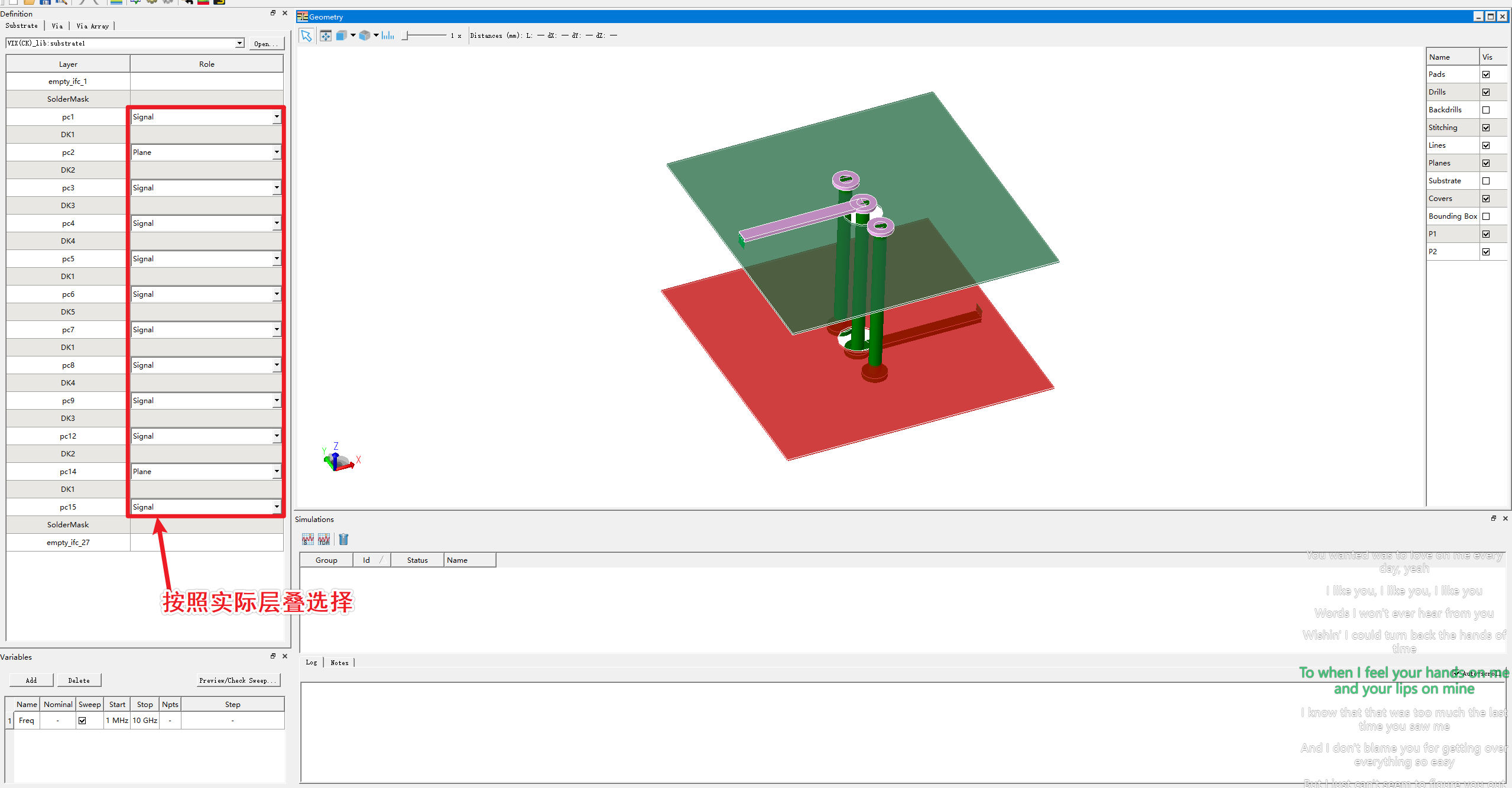

1)从”Tool”—>”Via Designer”进入

2)如果ADS中没有设置层叠会提示报错。建立层叠一般采用两种方式(个人习惯b)

? ? ? a)PCB导入ADS,这个网络上有很多教程,不赘述。

? ? ? b)自己设置层叠的话,可以参照板厂EQ给出的层叠文件,更加贴近实际情况:

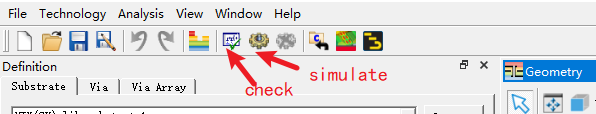

c)设置完成后可以点一下file-Check检查一下有没有错误

3)成功进入Via Designer后按照实际Substrate设置层属性

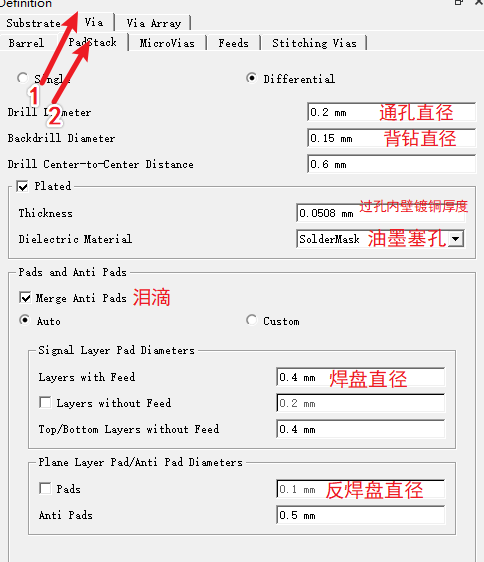

4)对Via各个参数进行设置

5)过孔的仿真只需要设置仿真的start和stop频率即可。软件会根据stop频率,以及仿真尺寸的大小,自动剖分mesh,并设置仿真频率点

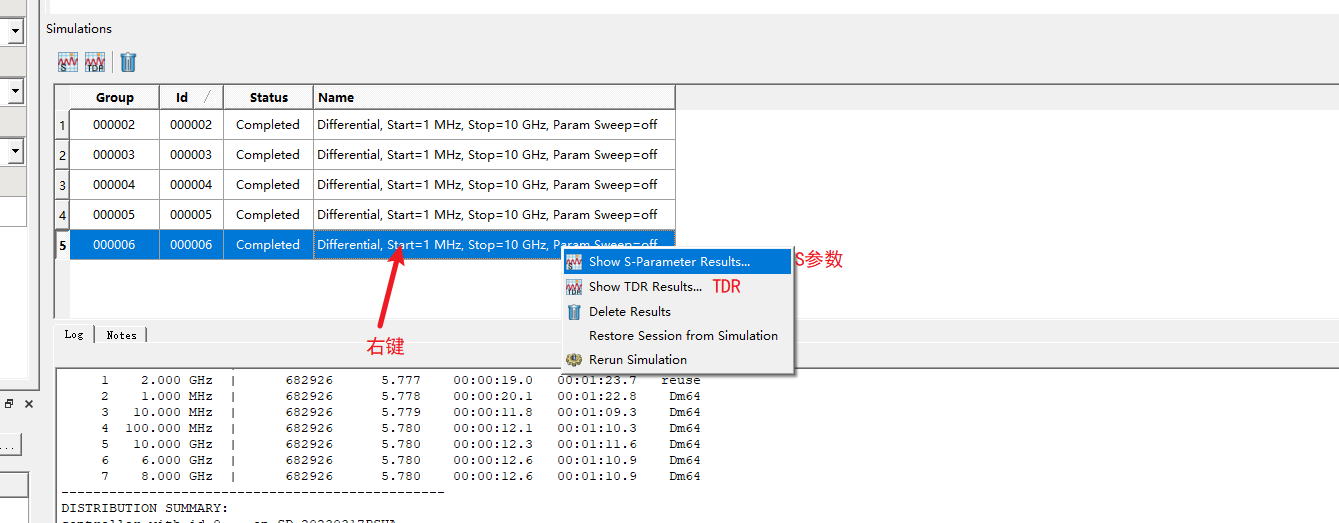

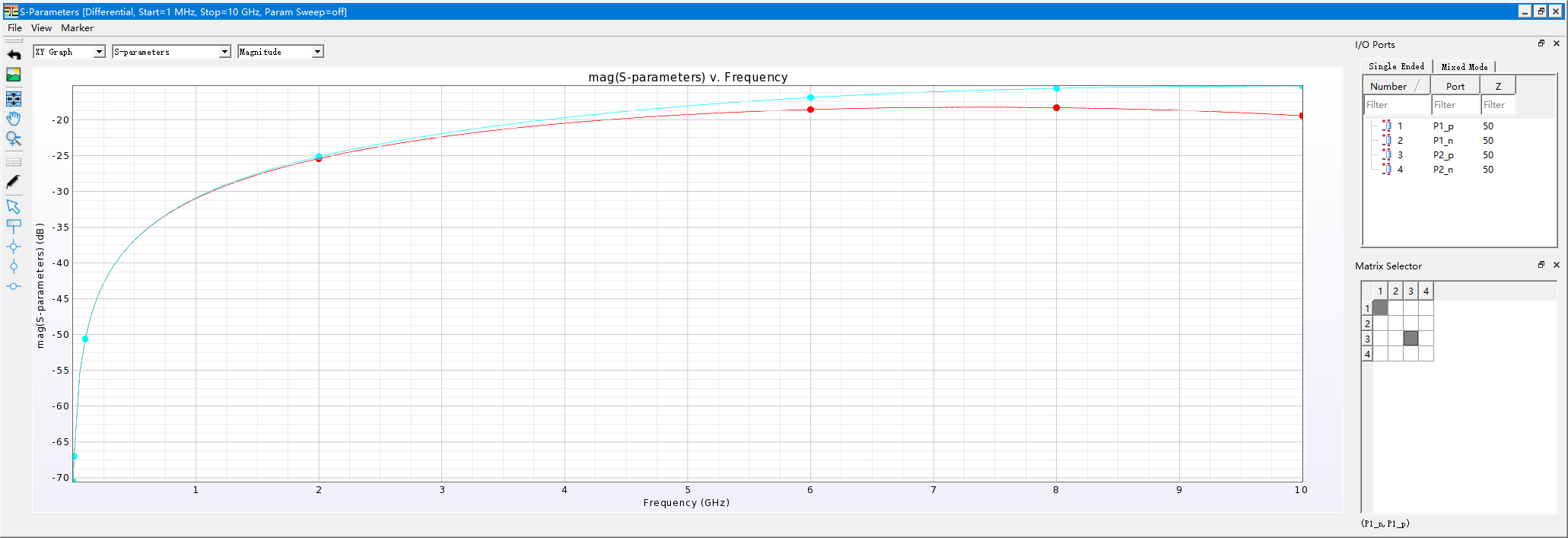

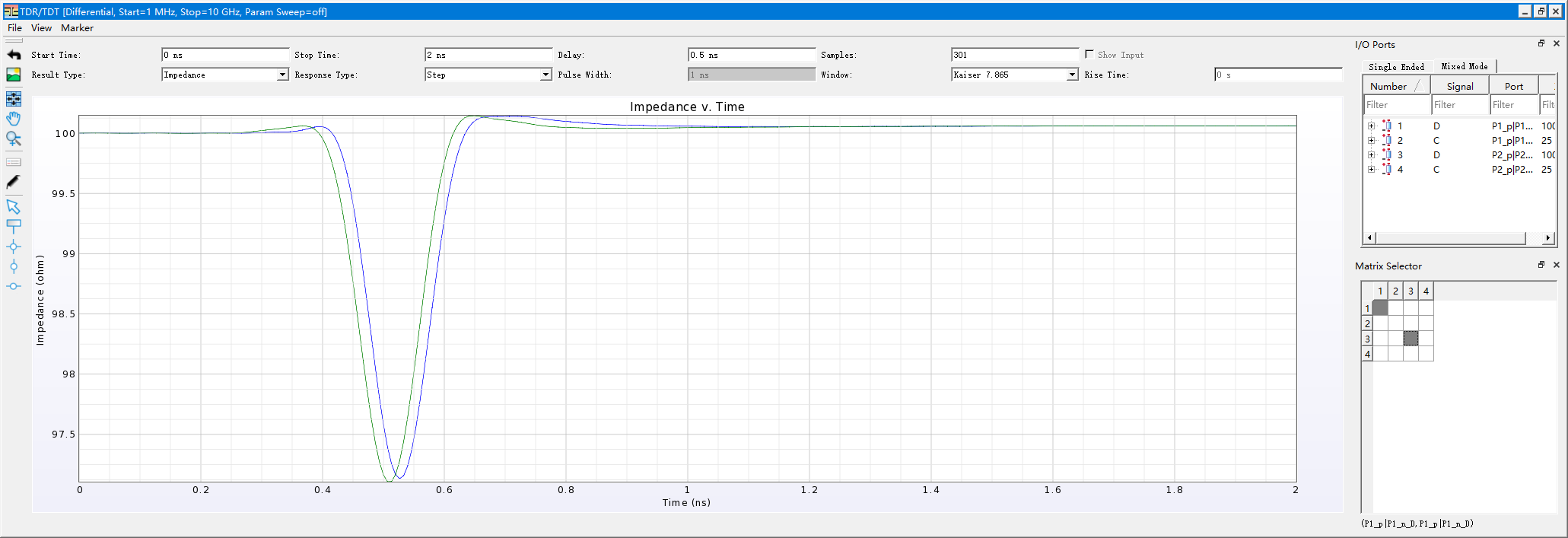

6)仿真完成后可以查看S参数和TDR曲线是否满足要求

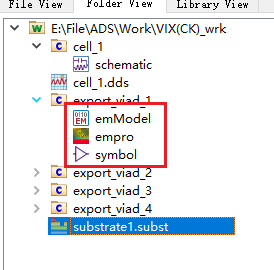

7)File--Export to cell选择想要导出的仿真结果,导出后结果可用于原理图仿真等

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!