计算机组成原理复习4

习题

练习题

- 下列不属于系统总线的为()

a.数据总线

b.地址总线

c.控制总线

d.片内总线

D

- 系统总线中地址总线的功能是()

a.选择主存单元地址

b.选择进行信息传输的设备

c.选择外存地址

d.指定主存和I/O设备接口电路的地址

D

解析:系统总线中的地址线用于指定要访问的内存或外设的地址。当处理器需要读取或写入到特定位置的数据时,它会将要访问的地址发送到地址线上。这样,系统中的其他设备就可以根据地址线上的信号来确定是否需要响应处理器的请求,以及进行相应的数据传输或处理。因此,地址线的功能是在计算机系统中实现对内存和外设的地址定位和访问。

- 系统总线中控制器的功能是()

a.提供主存,I/O接口设备的控制信号和响应信号

b.提供数据信息

c.提供时序信号

d.提供主存,I/O接口设备的响应信号

A

- 下列关于总线设计的叙述中,错误的是()

a.并行总线传输比串行总线传输速度快

b.采用信号线复用技术可以减少信号线数量

c.采用突发传输方式可提高总线数据传输速率

d.采用分离事务通信方式可提高总线利用率

A

解析:随着技术的发展,时钟频率越来越高,并行导线之间的相互干扰越来越严重;而串口因为导线少,线间干扰容易控制,反而可以通过不断提高时钟频率来提高传输速率。

- 下列选项中,可提高同步总线数据传输速率的是()

(1)增加总线宽度 (2)提高总线工作频率(3)支持突发传输 (4)采用地址/数据线复用方式

a.仅(1)(2)

b.仅(1)(2)(3)

c.仅(1)(4)

d.(1)(2)(3)(4)

B

- 突发传输是指在内存模块或者总线系统中的一种传输方式。在这种传输方式中,一系列的数据可以通过连续的时钟周期传输,而不需要每个数据都要发送一个地址。在突发传输中,首先发送一个地址,然后在接收到这个地址后,会一次性连续地传输相邻的数据。这可以提高内存或者总线的带宽,减少传输的延迟,提高系统的性能。

- 地址/数据线复用是指在同一条线上进行地址和数据信号的传输。这种方法通常用于存储器系统或总线结构中,可以减少系统中需要的总线数量,从而降低成本和复杂度。在地址/数据线复用中,同一根线路在不同的时间传输地址和数据信息,通过时序控制和协议来确保传输的正确性。当总线处于地址传输模式时,信号线会传输地址信息;而当处于数据传输模式时,这些线路则会传输数据信息。通过时序控制,可以确保在不同的时间段内进行地址和数据的正确传输。然而,地址/数据线复用也会引入一些额外的复杂性,如时序管理和对传输顺序的严格控制要求。因此,在系统设计时需要仔细考虑其优缺点,以满足系统性能和成本的平衡。

- 数据总线的宽度由总线的()特性决定

a.机械特性

b.功能特性

c.电气特性

d.时间特性

B

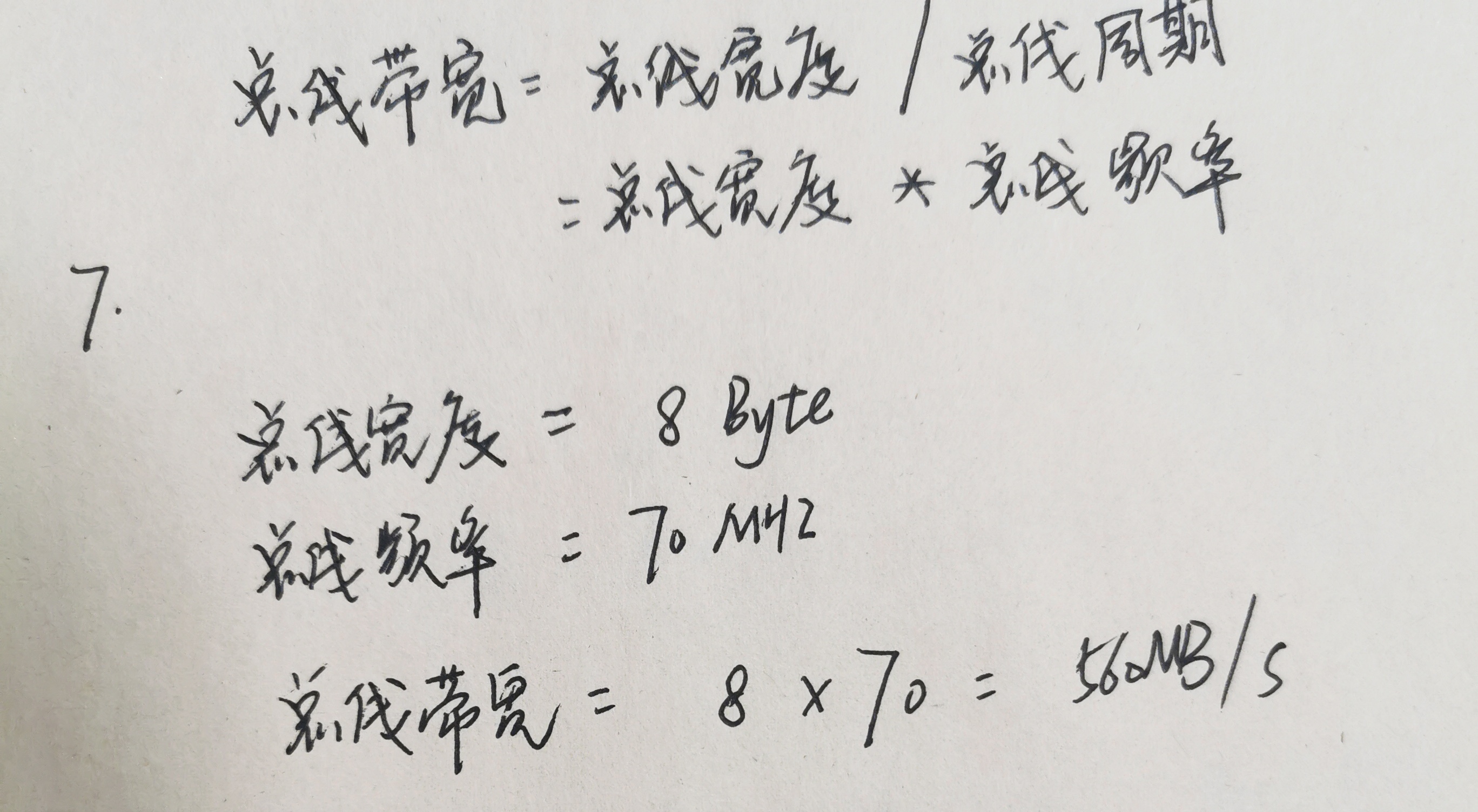

- 某总线在一个总线周期中并行传送8个字节的数据,假设一个总线周期等于一个总线时钟周期,总线时钟频率为70MHZ,求总线带宽是多少?

解析:

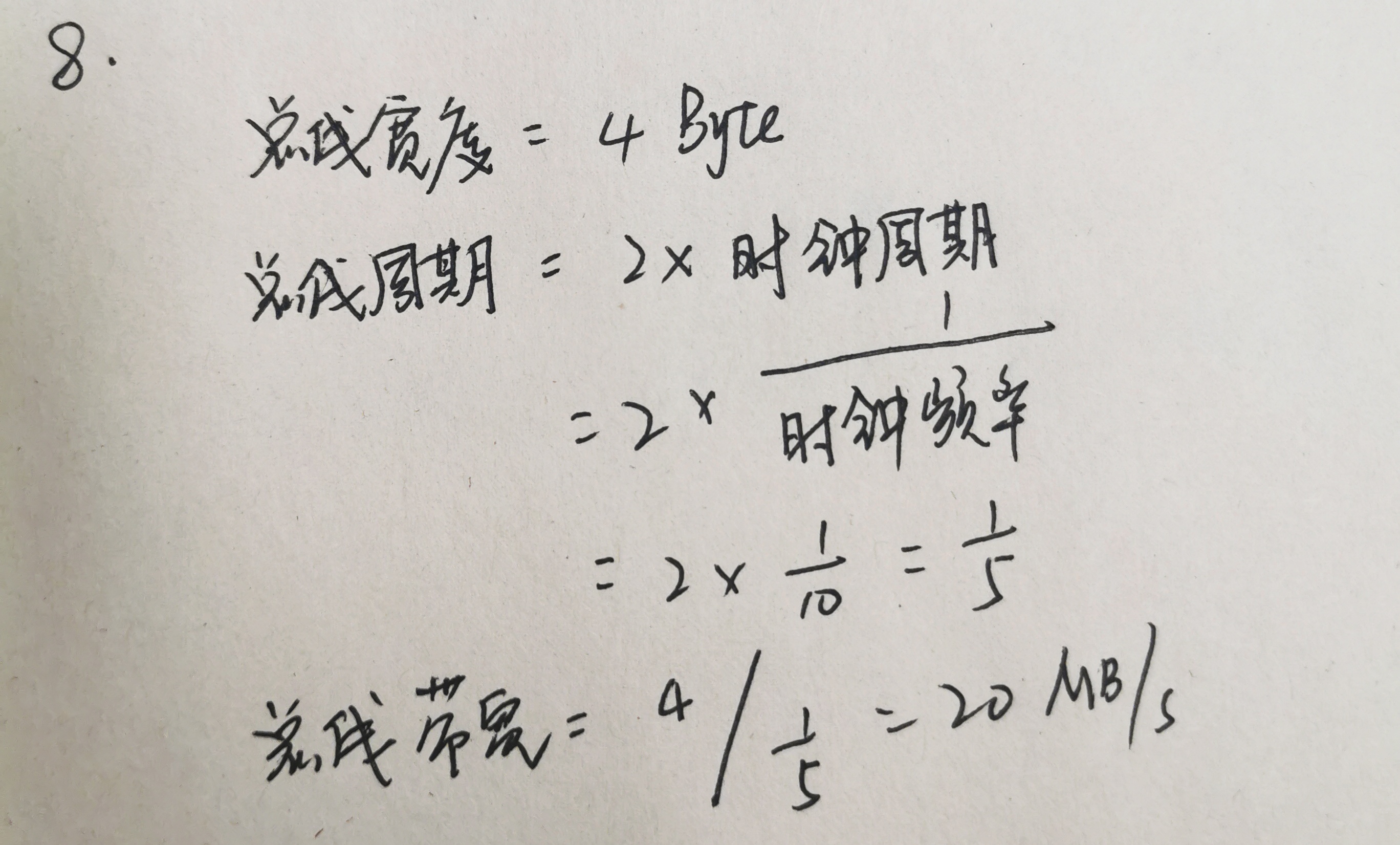

- 假设某系统总线在一个总线周期中并行传输4字节信息,一个总线周期占用两个时钟周期,总线时钟频率为10MHZ,则总线带宽是()

a.10MB/s

b.20MB/s

c.40MB/s

d.80MB/s

解析:

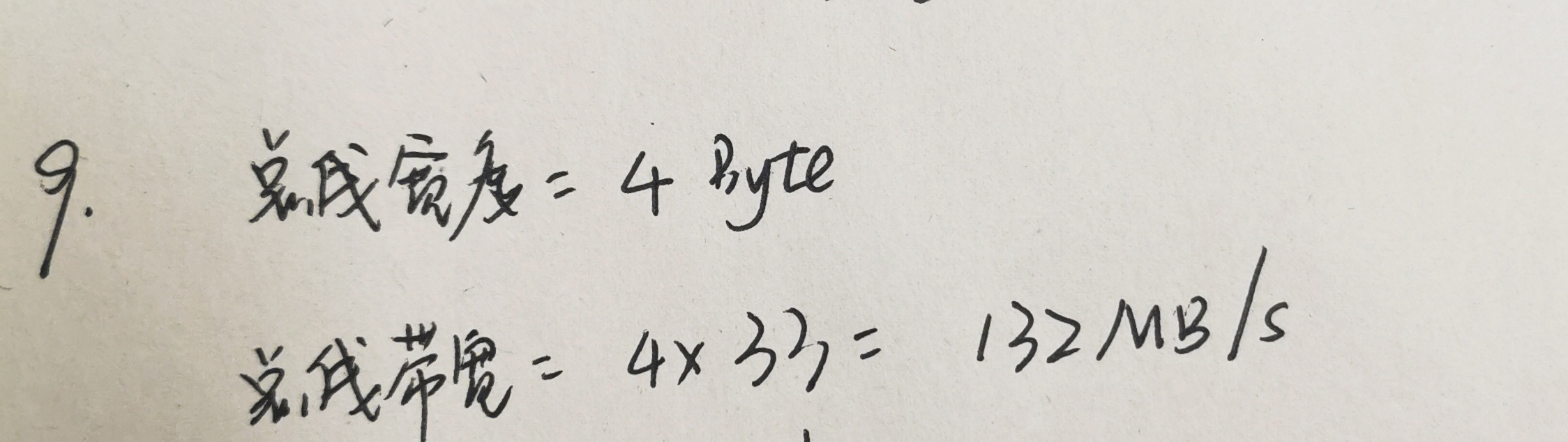

- 假设总线的时钟频率为33MHZ,且一个总线时钟周期为一个总线传输周期。若在一个总线传输周期并行传送4个字节的数据,求该总线的带宽,并分析哪些因素影响总线的带宽。

解析:

影响总线带宽的因素有:总线宽度,传输距离,总线发送和接收电路工作频率的限制以及数据传输形式等。

- 假设总线的时钟频率为100MHZ,总线的传输周期为4个时钟周期,总线的宽度为32位,试求总线的数据传输率。若想提高一倍数据传输率,可采取什么措施?

解析:

若想提高一倍数据传输率,可以在不改变总线时钟频率的前提下,使数据线宽度改为64位,也可以仍保持数据宽度为32位,但使总线的时钟频率增加到200MHZ

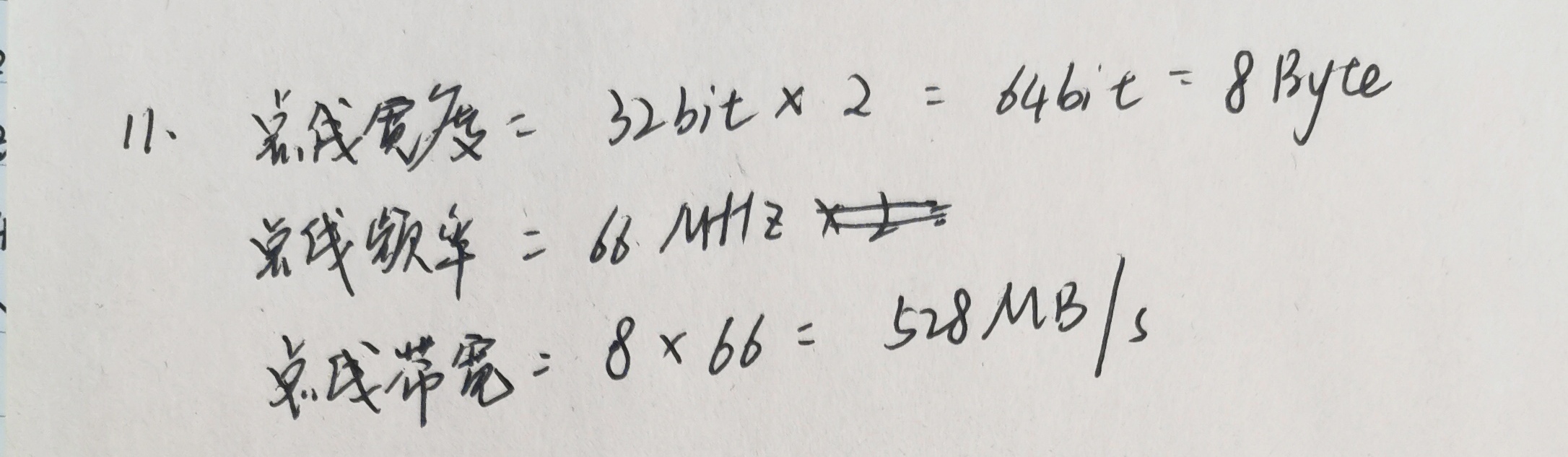

- 某同步总线采用数据线和地址线复用方式。其中地址/数据线有32条,总线时钟频率为66MHZ.每个时钟周期传送两次数据(上跳沿和下跳沿各传送一次数据),该总线的最大数据传输速率是()

a.132MB/s

b.264MB/s

c.528MB/s

d.1056MB/s

解析:

- 下列用于设备和设备控制器(I/O接口)之间互连的接口标准是()

a.PCI

b.USB

c.AGP

d.PCI-Express

解析:PCI外部设备互连总线,AGP加速图形接口,PCI-Express最新总线和接口标准。目前在PCIe,USB3.0等高速串行总线中都采用了8bit/10bit编码方式,这种方式的编码效率为80%.还有更高编码效率的64bit/66bit,128bit130bit方案。

- 现在lntel公司最新CPU中已经集成了PCIe3.0的显卡接口,其工作频率高达8GHZ。最大并行通路为40路,总线编码方式为128bit/130bit.支持全双工传输,尝试计算PCIe总线带宽。

解析:

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!