练习七-在Verilog中使用任务task

2023-12-13 06:22:09

在Verilog中使用任务task

1,任务目的

(1)掌握任务在verilog模块设计中的应用;

(2)学会在电平敏感列表的always中使用拼接操作、任务和阻塞赋值等语句,并生成复杂组合逻辑的高级方法。

当我们希望能够将一些信号进行运算并输出多个结果时,采用函数结构就显得很不方便,但是采用任务结构在这方面优势则十分突出。任务本身并不返回计算值,但它通过类似c语言中的形参和实参的数据交换,非常容易地实现运算结果的调用。

此外,还常利用任务来包装模块设计中的许多复杂任务的过程,将许多复杂的操作步骤用一个命名清晰易懂的任务隐藏起来,大大提高程序的可读性。

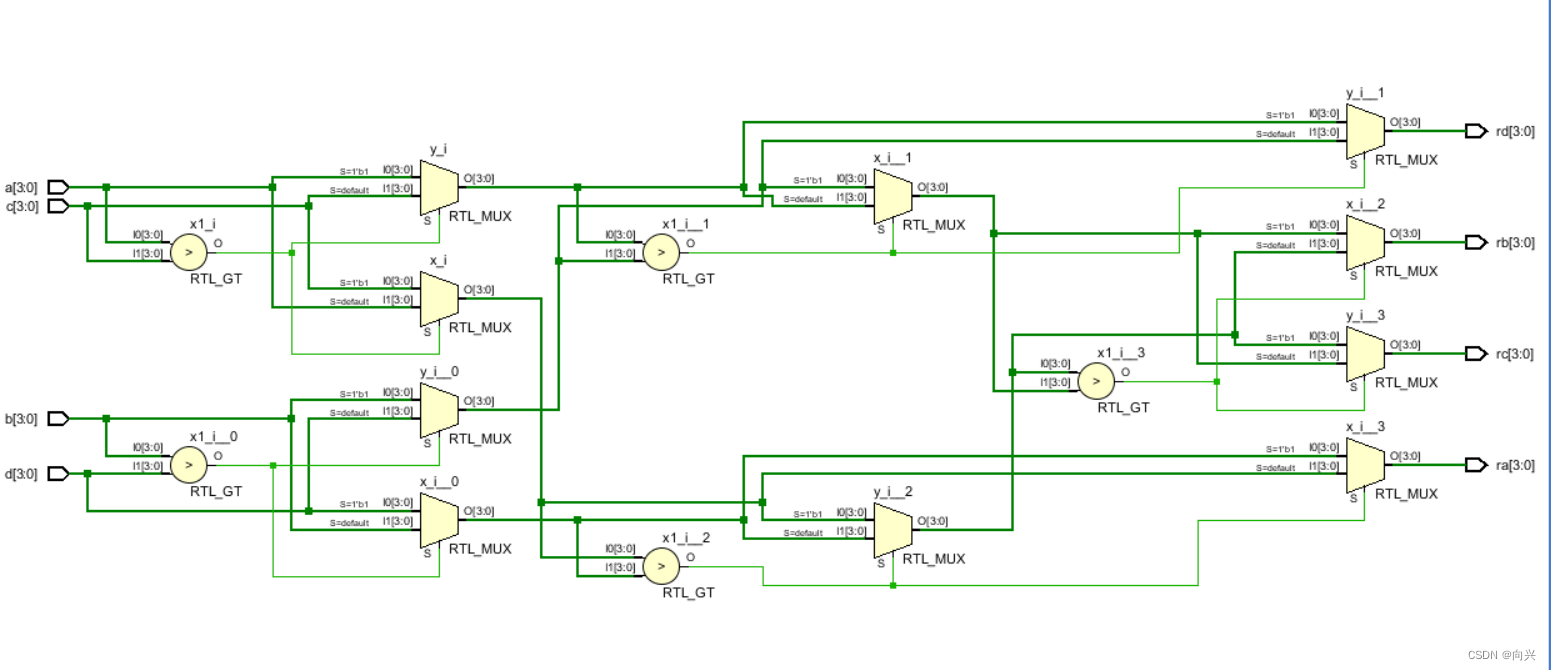

2,RTL代码,交换

// 在verilog中 使用任务 task

module sort4(

ra, rb, rc, rd,

a, b, c, d

);

input [3:0] a, b, c, d;

output reg [3:0] ra, rb, rc, rd;

reg [3:0] va, vb, vc, vd;

always@(a or b or c or d) begin

{va, vb, vc, vd} = {a, b, c, d};

sort2(va, vc); // va, vc 互换

sort2(vb, vd); // vb, vd 互换

sort2(va, vb); // va, vb 互换

sort2(vc, vd); // vc, vd 互换

sort2(vb, vc); // vb, vc 互换

{ra, rb, rc, rd} = {va, vb, vc, vd};

end

task sort2;

inout [3:0] x, y;

reg [3:0] tmp;

if(x > y) begin

tmp = x; // x与y变量的内容互换,要求顺序执行,则采用阻塞赋值方式

x = y;

y = tmp;

end

endtask

endmodule

3,测试代码

// 测试代码

module sort4_top;

reg [3:0] a, b, c, d;

wire [3:0] ra, rb, rc, rd;

initial begin

a = 0; b = 0; c = 0; d = 0;

repeat(50)

begin

#100 a = {$random}%15;

b = {$random}%15;

c = {$random}%15;

d = {$random}%15;

end

#100 $stop;

end

sort4 u_sort4(

.a (a),

.b (b),

.c (c),

.d (d),

.ra (ra),

.rb (rb),

.rc (rc),

.rd (rd)

);

endmodule

4,波形显示

文章来源:https://blog.csdn.net/qq_21952195/article/details/134524625

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!