嵌入式系统复习--ARM技术概述

上一篇

ARM体系结构

ARM体系结构的技术特征

- ARM的体系结构采用了若干Berkeley RISC处理器的特征

- Load/store体系结构

- 固定的32为指令

- 3地址指令格式

- 同时也放弃的一些Berkeley RISC特征

- 寄存器窗口

- 延迟转移

- 所有的指令单周期执行

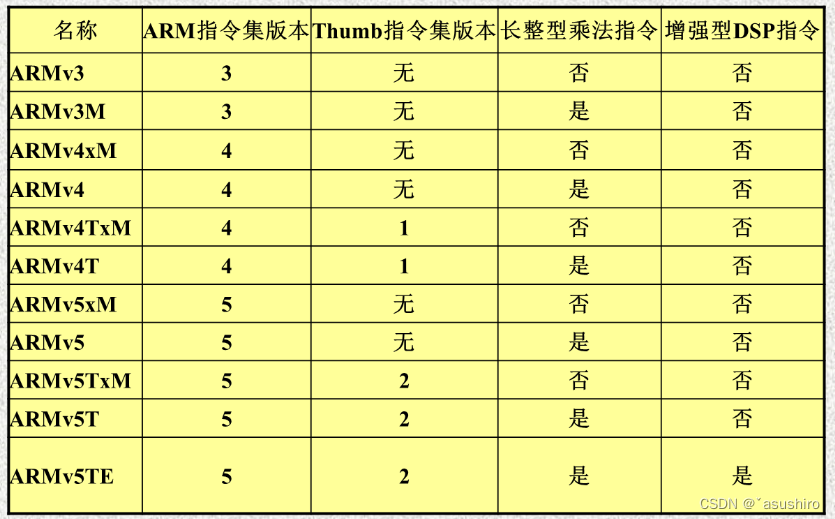

ARM体系结构的基本版本

ARM处理器体系结构发展了v1 ~ v8共8个版本

具有两种执行状态支持三个主要指令集:

A32(ARM):32为固定长度指令集,通过不同架构变体增强部分32为架构执行环境(AArch32)

T32(Thumb):以16为固定长度指令集的形式引入的,随后在引入Thumb-2技术时增强为16位和32位混合长度指令集,部分32位架构执行环境现在称为AArch32

A64:提供ARM和Thumb指令集类似功能的32位固定长度指令集,随ARMv8一起引入,是一种AArch64指令集。

ARM体系结构的演变

- Thumb指令集(T变种)

Thumb指令集是把32位的ARM指令集的一个子集重新编码后而形成一个特殊的16位的指令集 - 长乘指令(M变种)

长乘指令是一种生成64位相乘结果的乘法指令(此指令为ARM指令),M变种增加了两条长乘指令 - 增强型DSP指令(E变种)

E变种的ARM体系增加了一些增强处理器对典型的DSP算法处理能力的附加指令 - Java加速器Jazelle(J变种)

ARM的Jazelle技术时Java语言和先进的32位RISC芯片完美结合的产物 - ARM媒体功能扩展(SIMD变种)

ARM体系结构的命名规则

命名由下面几部分组成

- 基本字符串ARMv

- 基本字符串后为ARM指令集版本号

- ARM指令集版本号后为表示所含变种的字符。由于在ARM体系版本4以后,M变种称为标准部件,所以字符M通常也不单独列出来

- 最后使用的字符x表示排除某种功能

Thumb技术介绍

ARM的RISC体系结构的发展中已经提供了低功耗、小体积、高性能的方案。而为了解决代码长度问题,ARM体系结构有增加了T变种,开发了一种新的指令体系,这就是Thumb指令集,它是ARM技术的一大特色。

技术概述

它有从标准32位ARM指令集抽出来的36条指令格式,从新变成16位的操作码,提高代码密度。

支持Thumb的核仅仅是ARM体系结构的一种扩展,所以编译器既可以编译Thumb代码,又可以编译ARM代码,处理器状态可以方便的切换、运行到Thumb状态,在该状态下指令集是16位的Thumb指令集。

特点

优点:在性能代码大小之间取得平衡,在需要低的存储代码时采用Thumb指令系统,但又比纯粹16的系统更高的性能,因为实际执行的是32位指令,所以用Thumb指令编写最小代码量的程序,却取得以ARM代码执行的最好性能

缺点:

- 完成相同操作,需要更多指令,因此对系统运行时间要求苛刻的场合用ARM更合适

- 没有进行异常处理需要的一些指令,当发生异常中断时,还是需要使用ARM指令,这就需要处理器进行状态之间的切换

Thumb2技术

Thumb2内核技术,在与现有ARM技术方案完全兼容,他是一种混合型指令集,兼有16位及32位指令,增加32位指令解决了之前Thumb指令集不能访问协处理器、特权指令和特殊功能指令(例如SIMD)的权限。Thumb2现在可以实现所以的功能,就不需要在ARM/Thumb状态之间反复切换了,代码密度和性能得到显著提高。

ARM处理器工作状态

两种状态:

- ARM,执行字对准的32位ARM指令

- Thumb,执行半字对准的16位Thumb指令

在Thumb状态下,程序计数器PC使用位1选择另一个半字。

处理器在另种状态下切换时:

- 不影响处理器的模式或寄存器内容。

- 两种状态都有相应的状态切换命令

- 在最开始执行代码时,只能处于ARM状态

工作状态的切换方法:

- 进入Thumb状态

寄存器Rm状态位bit[0]为1时,执行

进入Thumb状态BX Rm - 进入ARM状态

寄存器Rm状态位bit[0]为0时,执行

进入ARM状态BX Rm

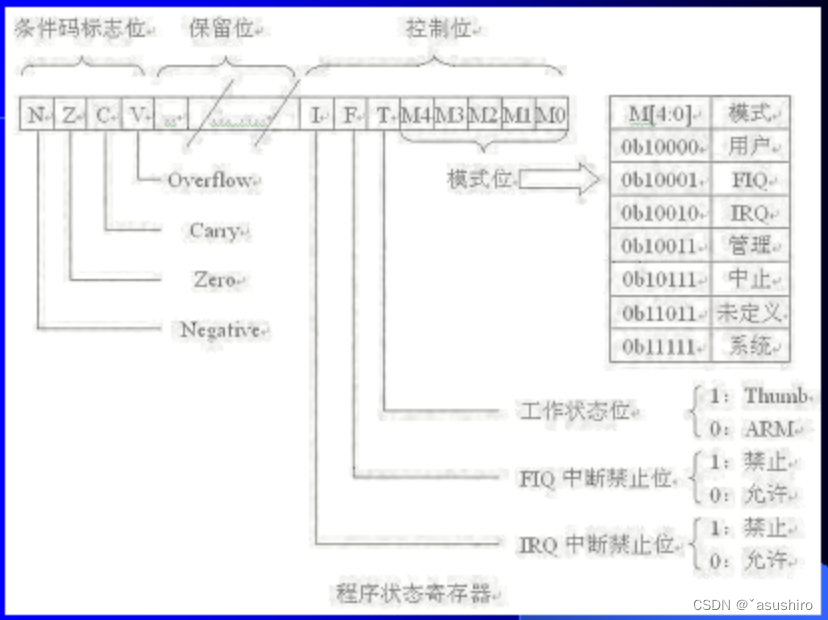

CPSR(当前程序状态寄存器)的低5位用于定义当前操作模式

| CPSR[4:0] | 模式 | 用途 | 可访问的寄存器 |

|---|---|---|---|

| 10000 | 用户 | 正常用户模式,程序正常执行 | PC,R14~R0,CPSR |

| 10001 | FIQ | 处理快速中断,支持高速数据传送或通道处理 | PC, R14_fiq ~ R8_fiq, R7~R0, CPSR, SPSR_fiq |

| 10010 | IRQ | 处理普通中断 | PC, R14_irq ~ R13_irq, R12 ~ R0, CPSR, SPSR_irq |

| 10011 | SVC | 操作系统保护模式,处理软件中断(SEI) | PC, R14_svc ~ R13_svc, R12 ~ R0, CPSR, SPSR_svc |

| 10111 | 中止(ABT) | 处理存储器故障、实现虚拟存储器和存储器保护 | PC, R14_abt ~ R13_abt, 12 ~ R0, CPSR, SPSR_abt |

| 11011 | 未定义 | 处理为定义的指令陷阱,支持硬件协处理器的软件仿真 | PC, R14_und ~ R13_und, R12 ~ R0, CPSR, SPSR_und |

| 11111 | 系统 | 运行特权操作系统任务 | PC, R14 ~ R0, CPSR |

注:标红的为异常模式

ARM寄存器组成概述

ARM处理器共有37个寄存器,可以分为两类寄存器:

- 32个通用寄存器

- R0 ~ R15

- R8_fiq~R14_fiq

- R13_irq、R14_irq

- R13_svc、R14_svc

- R13_abt、R14_abt

- R13_und、R14_und

- 6个状态寄存器

CPSR, SPSR_fiq, SPSR_irq, SPSR_svc, SPSR_abt, SPSR_und

其中通用寄存器分为:

- 不分组寄存器 (R0 ~ R7)

这意味着所有处理器模式下,都访问的是这些寄存器,真正意义下的通用寄存器 - 分组寄存器(R8 ~ R14)

R13通常用作堆栈指针(SP)

R14用作程序链接寄存器(Link Register (LR)) - 程序计数器(R15(PC))

R15值的改变将引起程序执行顺序的改变,可能引起不可预料的结果,采用多级流水线技术,因此保存在R15中的程序地址并不是当前指令的地址,一些指令对R15的用法有一些特殊的要求

ARM程序状态寄存器

- 所有处理器模式下都可以访问当前的程序状态寄存器CPSR。CPSR包含条件码标志、中断禁止位、当前处理器模式以及其他状态和控制信息。

- 在每种异常模式下都有一个对应的物理寄存器–程序状态保存寄存器(SPSR)。

- 当异常发生时,SPSR用于保存CPSR的状态,以便异常返回后恢复异常发生时的工作状态。

Thumb状态寄存器组织

- 8个通用寄存器(R0 ~ R7)

- 程序计数器(R15 (PC) )

- 堆栈指针(R13 (SP) )

- 链接寄存器(R14 (LR) )

- 当前状态寄存器(CPSP)

- 每个特权状态都有各自一组SP, LR, SPSR

ARM的异常响应过程

异常响应过程如下:

- 将CPSR的内容保存到将要执行的异常中断对应的SPSR中

- 设置当前状态寄存器CPSR中的相应位

- 将引起异常指令的下一条指令的地址保存到新的异常工作模式的R14(LR)

- 给程序计数器(PC)强制赋值

每个异常模式下都有

- SP堆栈寄存器

可用来定义一个存储区域保存其他用户寄存器,这样异常处理程序就可以使用这些寄存器 - LR连接寄存器

返回地址,中断结束返回的地址

而FIQ模式还有额外的专用寄存器R8_fiq ~ R12_fiq, 使用这些寄存器可以加快快速中断的处理速度。

从异常中断处理程序中返回过程:

- 所有修改过的用户寄存器必须从处理程序的保护堆栈中恢复(即出栈)

- 将SPSR_mode寄存器内容复制到CPSR中,使得CPSR从相应的SPSR中恢复,即恢复被中断的程序工作状态

- 根据异常类型将PC变回到用户指令流中相应指令出

- 最后清除CPSR中的中断禁止标志位I/F

异常中断的优先级:1.复位 2.数据异常中断 3.FIQ 4.IRQ 5.预取指异常中止 6.SWI,未定义指令

ARM的流水线方式

- 3级流水线(到ARM7为止是)

取指级,译码级,执行级

pc要根据流水线的对应位置,对R15的值相对改变 - 5级流水线

取指、译码、执行、缓冲/数据、回写

ARM存储器接口及存储器层次

ARM处理器支持的6中数据类型

- 8位有符号和无符号字节

- 16位有符号和无符号半字,他们以两字节为边界定位

- 32位有符号和无符号字,他们以4字节的边界定位

大端存储,是将数据的低位字节放到高地址处,高位字节放到低地址处。

小端存储,是将数据的低位字节放到低地址处,高位字节放到高地址处。

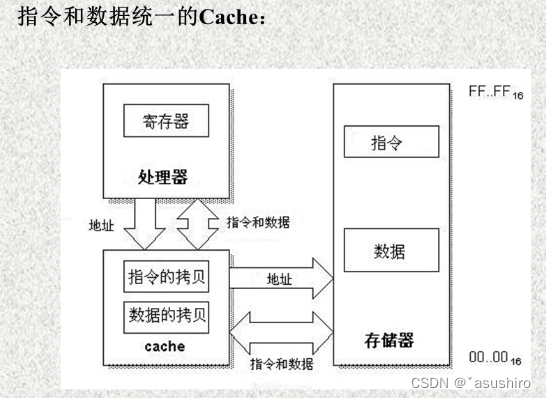

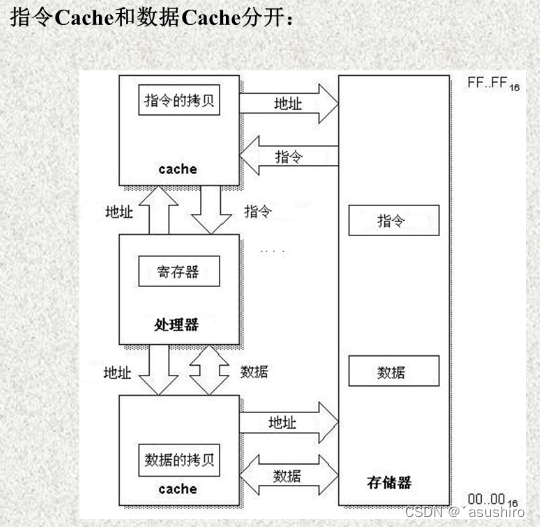

存储器层次

- 寄存器组

- 片上RAM

- 片上Cache

- 主存储器

- 硬盘

Cache及WRITE BUFFER

MMU完成的工作

- 实现从虚拟地址到物理地址的转换

- 存储器访问权限的控制

- 设置虚拟存储空间的缓冲特性

用于存储管理的系统控制协处理寄存器CP15

在基于ARM的嵌入式系统中,存储系统通常使用CP15来完成存储器的大部分管理工作。包含16个32位寄存器编号0 ~ 15

快速上下文切换技术

通过修改系统中不同进程的虚拟地址,避免在进行进程间切换时造成的虚拟地址到物理地址的重映射,从而提高系统性能。

ARM片上总线AMBA

- AHB: 用于连接高性能系统模块。它支持突发数据传输方式及单个数据传输方式,所有时序参考同一个时钟沿。

- ASB:用于连接高性能系统模块,支持突发数据穿输模式

- APB: 是一个简单接口支持低性能的外围接口

异常表示

R14_<exception_mode> = return link

SPSR_<exception_mode> = CPSR

CPSR[4:0] = exception mode number

CPSR[5] = 0 //在ARM状态运行

If <exception_mode> == Reset or FIQ then

CPSR[6] = 1

CPSR[7] = 1

PC = exceptoin vector address

复位操作:

一旦有复位输入,ARM处理器就立即停止执行指令,完成一列操作

R14_svc = UNPREDICTALE value

SPSR_svc = UNPREDICTALE value

CPSR[4:0] = 0b10011 // 进入管理模式

CPSR[5] = 0 // 在ARM状态运行

CPSR[6] = 1 //禁止快速中断

CPSR[7] = 1 //禁止正常中断

PC = 0x00000000

中断请求异常(IRQ)

通过处理器上的IRQ输入引脚,有外部引入IRQ中断异常,比FIQ有优先级低,当进入FIQ处理会屏蔽IRQ异常

R14_irq = address of next instruction to be

executed +4

SPSR_irq = CPSR

CPSR[4:0] = 0b10010 // 进入IRQ模式

CPSR[5] = 0 //在ARM状态运行

CPSR[7] = 1//禁止正常中断

PC = 0x00000018

下一篇

未完待续

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!