[Verilog] 设计方法和设计流程

主页: 元存储博客

1. 设计方法

Verilog 的设计多采用自上而下的设计方法(top-down)。设计流程是指从一个项目开始从项目需求分析,架构设计,功能验证,综合,时序验证,到硬件验证等各个流程之间的关系。

可以采用以下的设计方法:

自顶向下设计:首先确定整个设计的高层结构,然后逐步细化,直到实现最底层的模块。

模块化设计:将整个设计分解成多个模块,每个模块负责完成一个特定的功能。这样可以提高设计的可维护性和可扩展性。

参数化设计:将设计中的一些常量参数化,以方便灵活地修改和适应不同的需求。

时序和组合逻辑分离:将设计中的时序逻辑和组合逻辑分开,以简化设计和验证的复杂度。

2. 设计流程

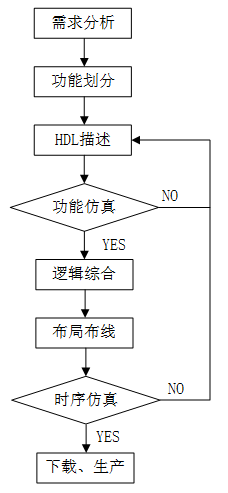

设计流程一般包括需求分析、工程估计、项目描述、功能划分、文本描述、功能仿真、逻辑综合、布局布线、时序仿真(后仿真)、板级验证、生产交付和后期维护。

-

需求分析:对用户的功能要求进行分析,确定技术指标和初步方案。评估项目的工程难度、时间和资源投入等。对整个电路的功能、接口和结构进行总体设计。

-

功能划分:将电路分解为功能模块,并分配子模块设计任务。

-

HDL描述:使用文本编辑器或专用的HDL编辑环境进行电路建模,并编写相关文档。

-

功能仿真(前仿真):对建模文件进行编译,并对模型电路进行功能上的仿真验证。

-

逻辑综合:将高层次描述转换为门级网表,并进行逻辑和时序优化。

-

布局布线:根据门级网表和约束文件,进行电路的布局和布线。

-

时序仿真(后仿真):利用布局布线后的电路模型进行时序验证。

-

板级验证:将设计的数字电路目标文件下载到FPGA/CPLD芯片中,并在电路板上进行调试和验证。

-

生产交付:如果需要在ASIC上实现,进行芯片制造。

-

后期维护:对电路进行改写、润色,解决bug和功能修改等。

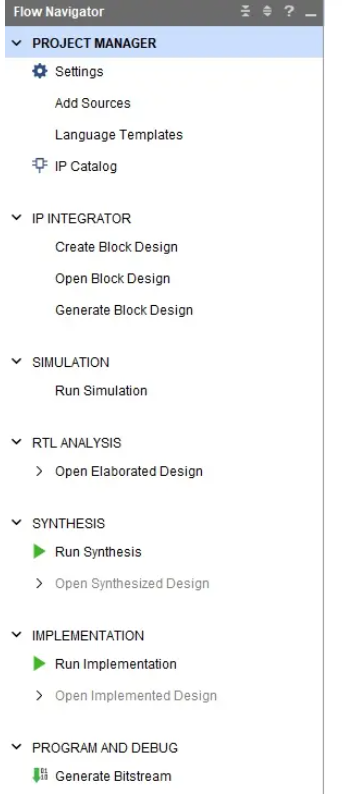

3 Vivado软件设计流程

Vivado 进行开发的典型流程:

-

项目创建:在Vivado 中创建一个新项目,选择项目名称和存储位置。可以选择从头开始创建一个新设计,或者导入一个已有的设计。

-

添加设计文件:将需要的设计文件添加到项目中。这些文件可以包括源代码文件(如Verilog 或VHDL 文件)、约束文件(如XDC 文件)和其他必要的文件。

-

约束文件定义:定义约束文件,以指定设计中的时序、引脚和时钟等信息。可以使用Xilinx Constraints Language (XDC) 编写约束文件。

-

仿真验证:使用Vivado 自带的仿真工具,对设计进行功能验证和验证。可以选择使用模拟波形查看器进行波形分析,以确保设计符合预期。

-

综合和实现:使用Vivado 的综合和实现工具,将设计综合为逻辑网表,并在目标设备上实现。综合将设计转换为门级电路,而实现则使用目标设备特定的资源和布局规则生成位流文件。

-

时序分析和优化:使用Vivado 的时序分析工具,对设计的时序进行分析和优化。可以使用时序查看器查看设计中的时序路径,并通过优化器工具改善设计的性能。

-

板级设计和集成:如果设计涉及硬件平台(如FPGA 或SoC),可以使用Vivado 的板级设计和集成工具,将设计与硬件平台进行集成。

-

部署和调试:将位流文件加载到目标设备中进行部署。可以使用Vivado 的调试工具和硬件调试器对设计进行调试,并进行性能优化。

-

生成文档和报告:使用Vivado 的文档生成工具,生成设计文档和报告,以记录设计过程和结果。

-

版本控制和团队协作:Vivado 提供了与常用版本控制系统(如Git)的集成,以便多人团队可以协同开发和管理设计。

总结

Verilog设计方法和设计流程是一个迭代的过程,需要不断地分析、设计、验证和优化,最终得到满足需求的设计方案。在设计过程中,需要充分考虑电路结构、逻辑实现、时序要求等因素,以及合理利用Verilog语言和EDA工具来辅助设计。

参考文献

声明

本文仅为学习交流目的。

文中部分文字和图片来源于互联网,列在参考的文献,但可能有遗漏。如有侵权,请告知我删除。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!