Low Cost and High Performance FPGA with ARM and SDRAM inside

AG10KSDE176

AGM AG10KSDE176 是由 AGM FPGA AG10K 与 SDRAM 叠封集成的芯片,具有 AG10K FPGA 的可编程功能,提供更多可编程 IO,同时内部连接大容量 SDRAM。

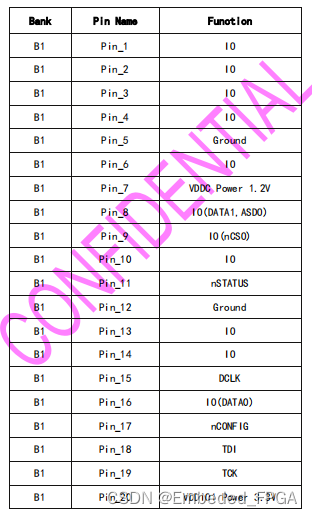

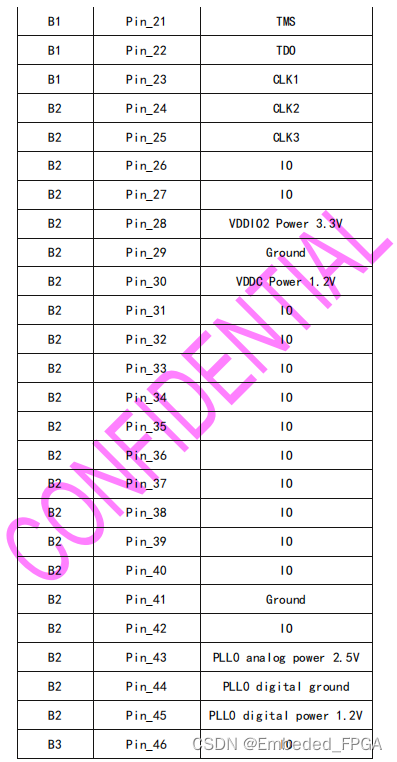

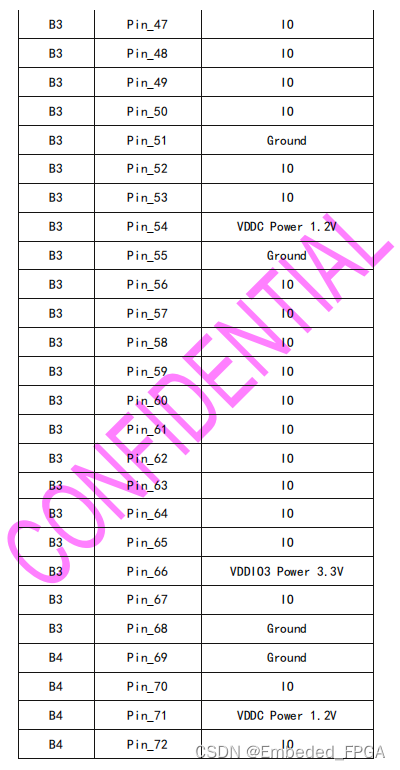

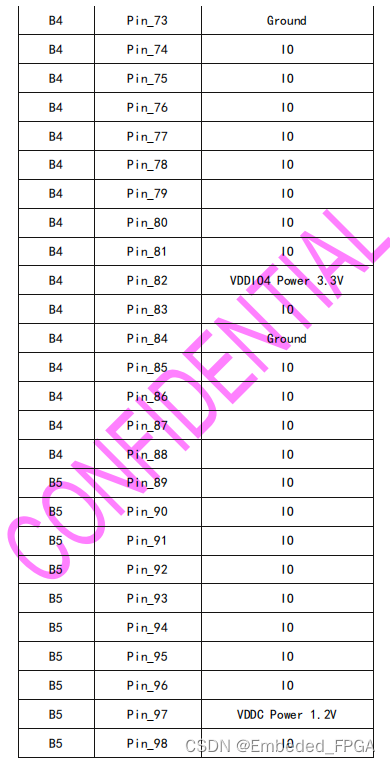

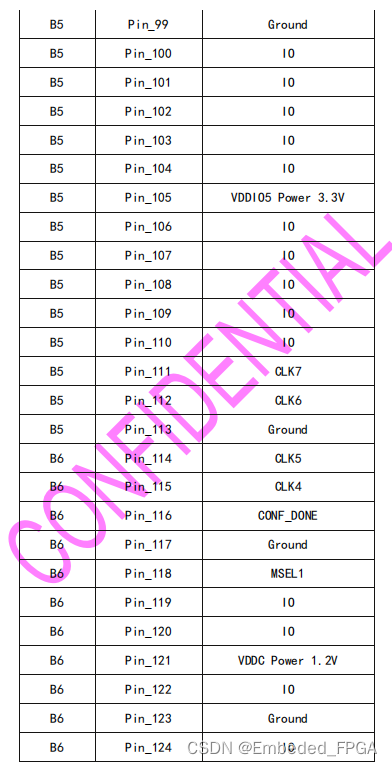

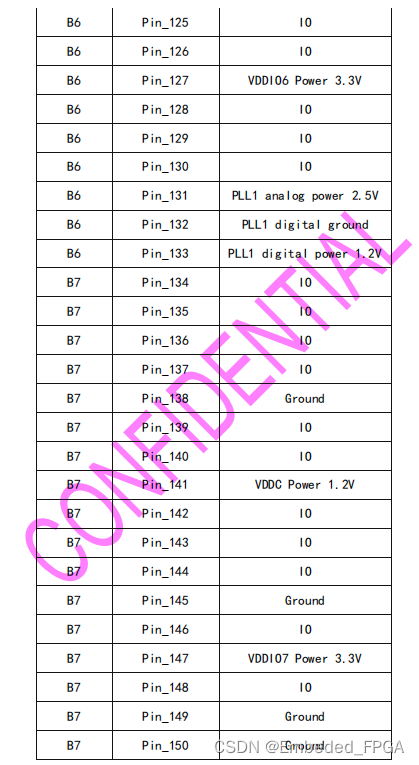

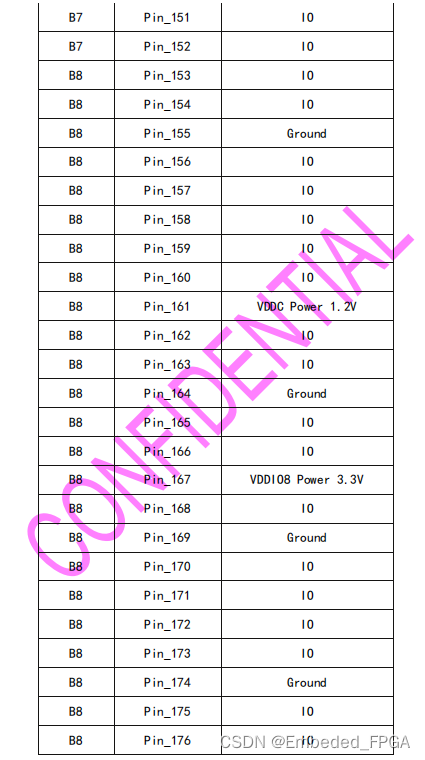

? FPGA 外部管脚输出

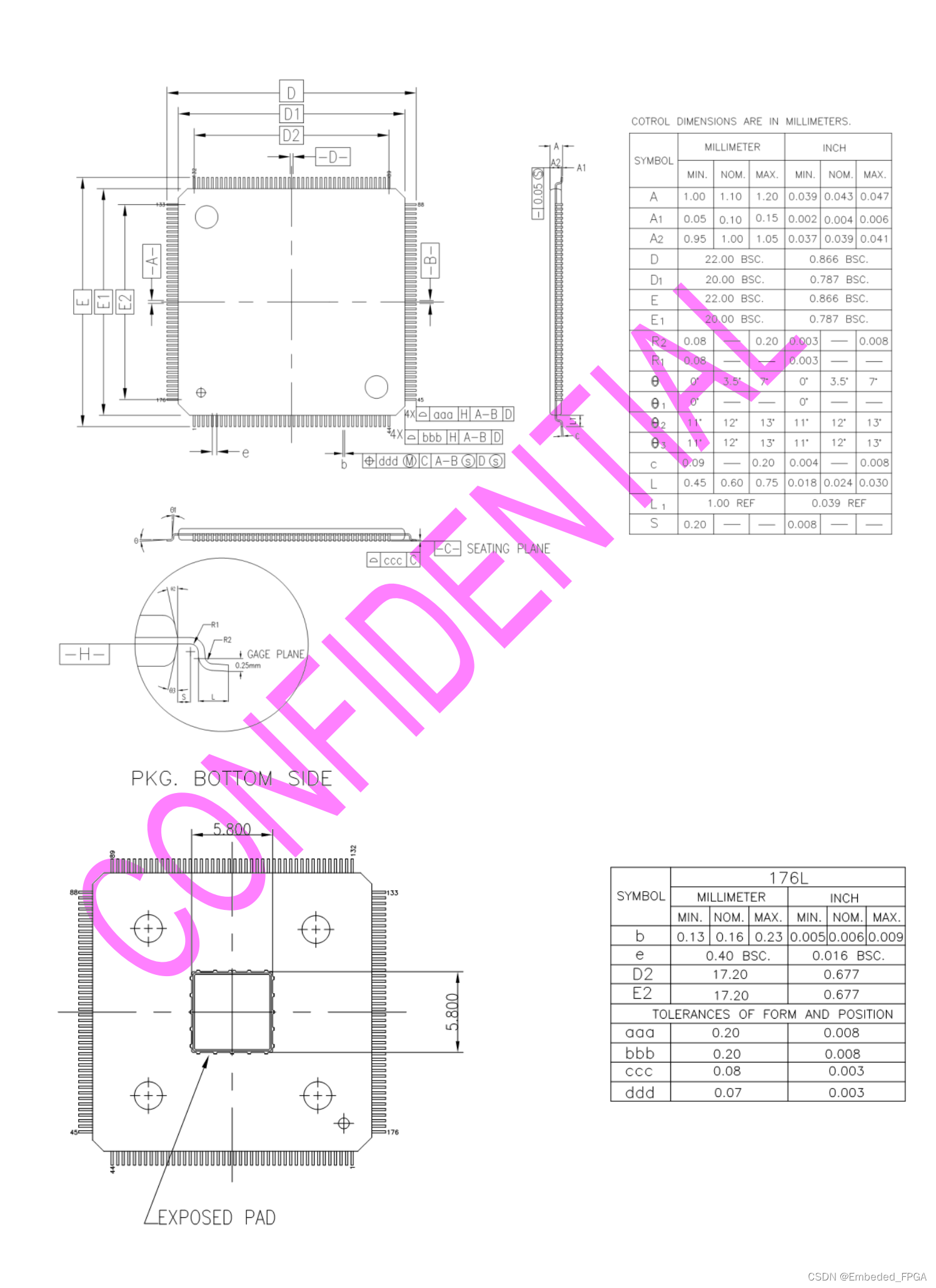

EQFP176 封装底部 Pad 为 GND,管脚说明请见下表:

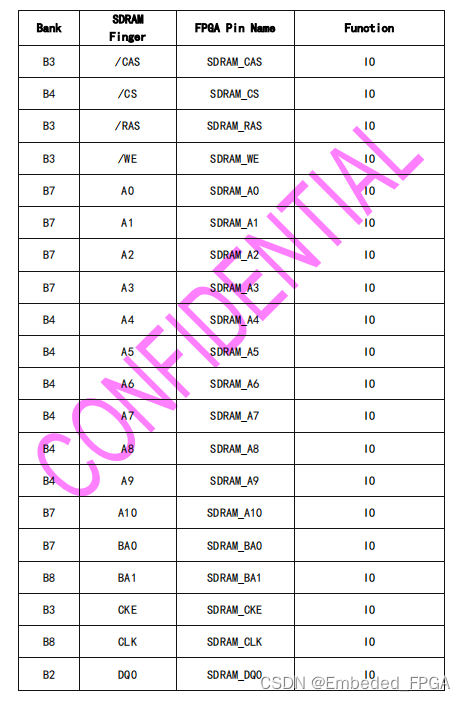

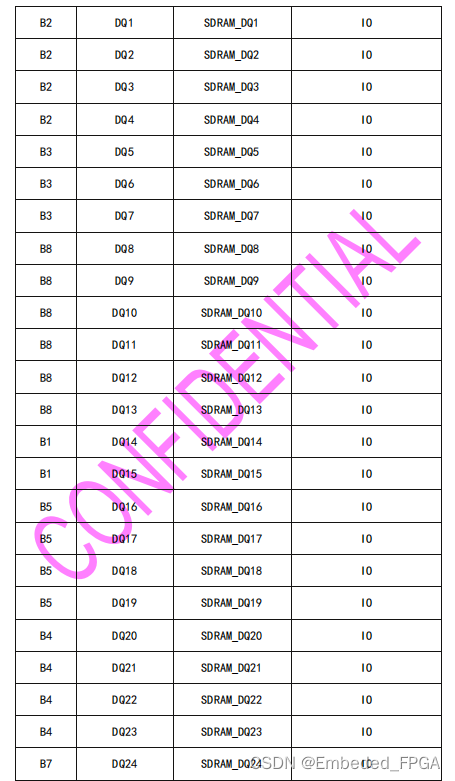

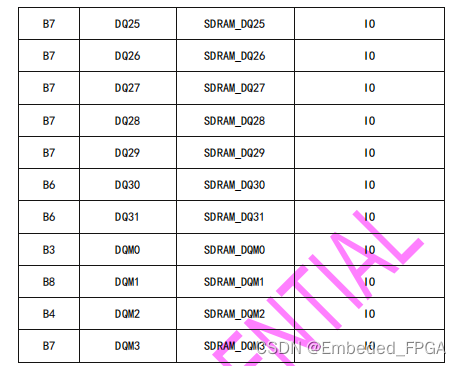

? SDRAM 说明

内部 SDRAM 为 64Mbit(512K words × 4 banks × 32 bits)容量。由于 SDRAM 为 3.3V 器件,FPGA 的 VCCIO 也需接 3.3V。

FPGA 的 IO 与 SDRAM 的内部连接,请见下表:

? 配置说明

AG10K 配置方式支持 JTAG,AS(Master)和 PS(Slave)方式,可通过 MSEL[2…0]选择。

其中 MSEL2 和 MSEL0 已在封装内接到 GND,仅需把外部管脚 MSEL1 按照下表设置,选择不同配置模式。AS 方式也是通过 JTAG 口直接烧写配置 FLASH。

? 封装图

? 软件开发流程(Compatible 模式)

用 Quartus 基于 Cyclone IV EP4CE10F17 为基础完成原始设计。管脚位置分配可先忽略。

建一新目录作为 AG10K 的项目目录。

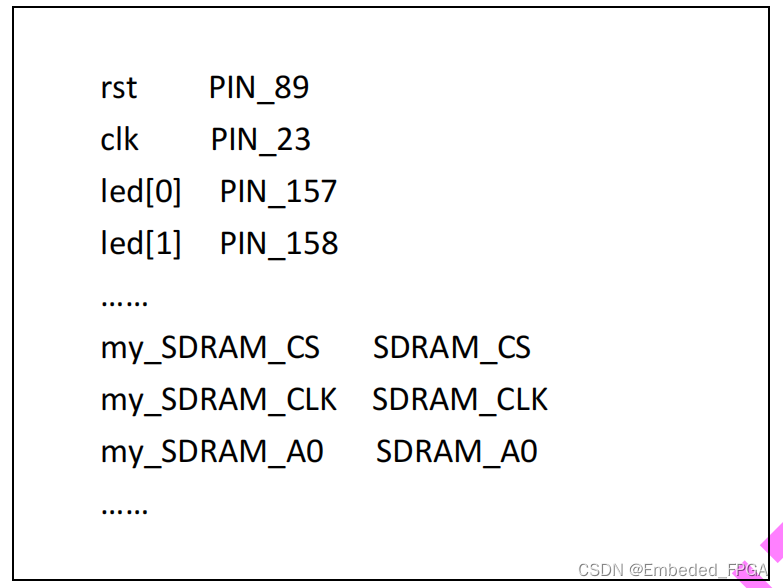

新建一个文本格式的管脚分配文件,命名为.ve。编辑 ve 文件加入 FPGA 的 IO位置设置。管脚名称请参考前面的管脚说明表格,ve 文件格式如下(管脚设计名称+空格+封装管脚名称):

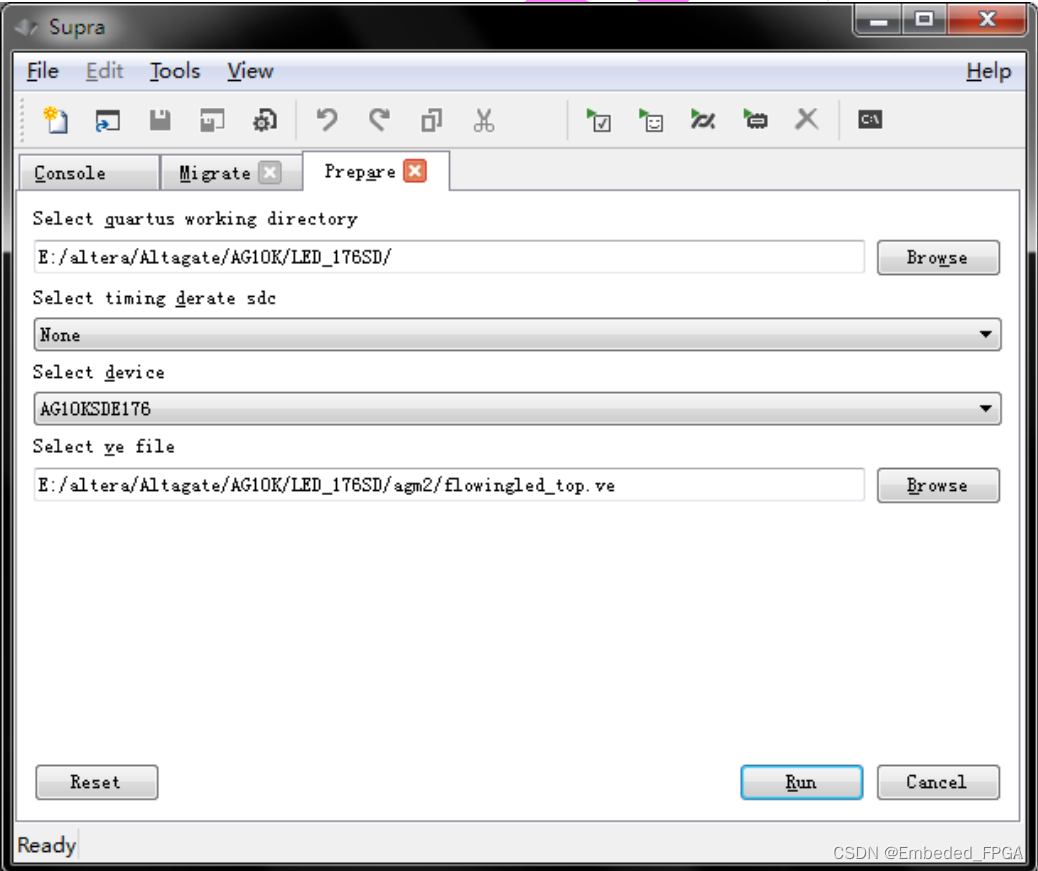

打开 AGM Supra 软件,新建工程,执行 Tools-Prepare。选择 Quartus II 项目目录,Device选 AG10KSDE176,并选择编辑好的 ve 文件后,点击 Run。正确运行后会生成 af_prepare.tcl等文件。

打开 Quartus 项目,通过 Tools-Tcl Scripts 运行 af_prepare.tcl 脚本文件,会把 ve 的内容导入到 EP4CE10 对应的管脚分配,并继续执行编译过程,在项目目录中生成 Simulation目录以及综合后的 vo 等文件。

注意:PIN_38 和 PIN_168 在 F256 里没有对应管脚,所以 Quartus 没有分配,可以忽略。

Supra 会在后面的编译中按照 ve 文件分配到 176 封装的具体管脚。如原 Quartus II 工程中有管脚分配信息,需先删除再执行 TCL。

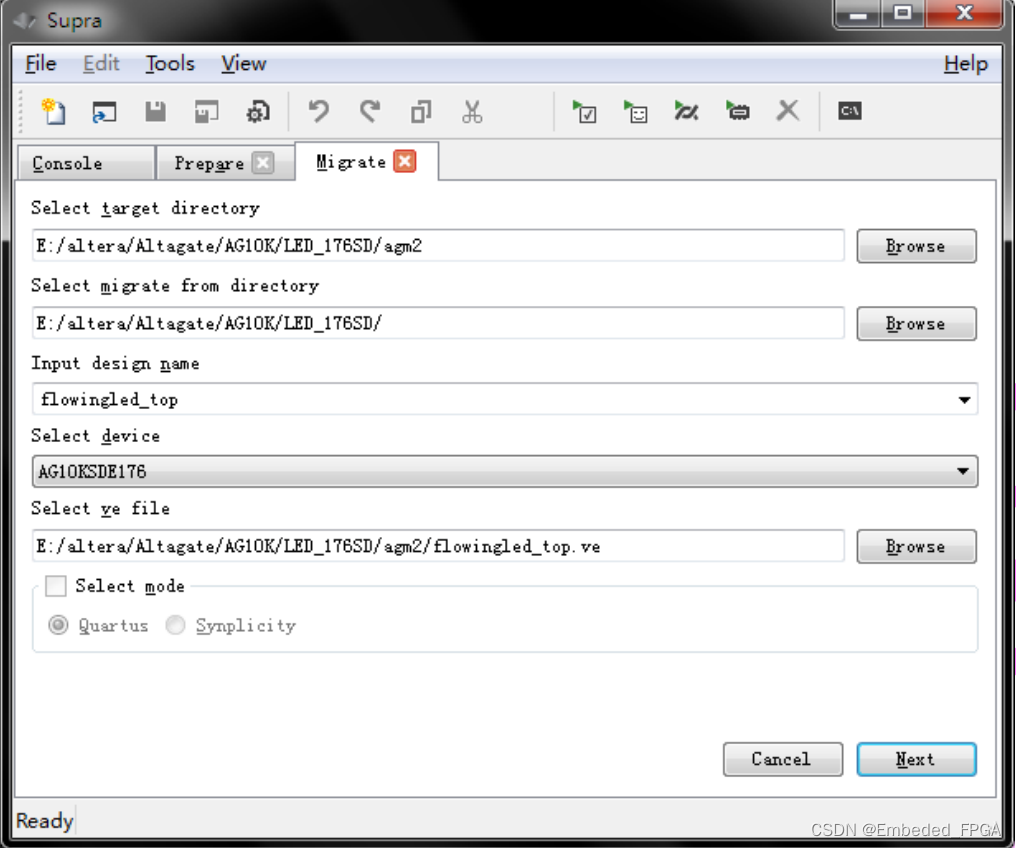

打开 AGM Supra 软件,执行 Tools-Migrate。Target directory 设为 AG10K 的项目目录,From directory 设为原 EP4CE10 的设计目录。选择 Device 为 AG10KSDE176,同样选择 ve 文件。

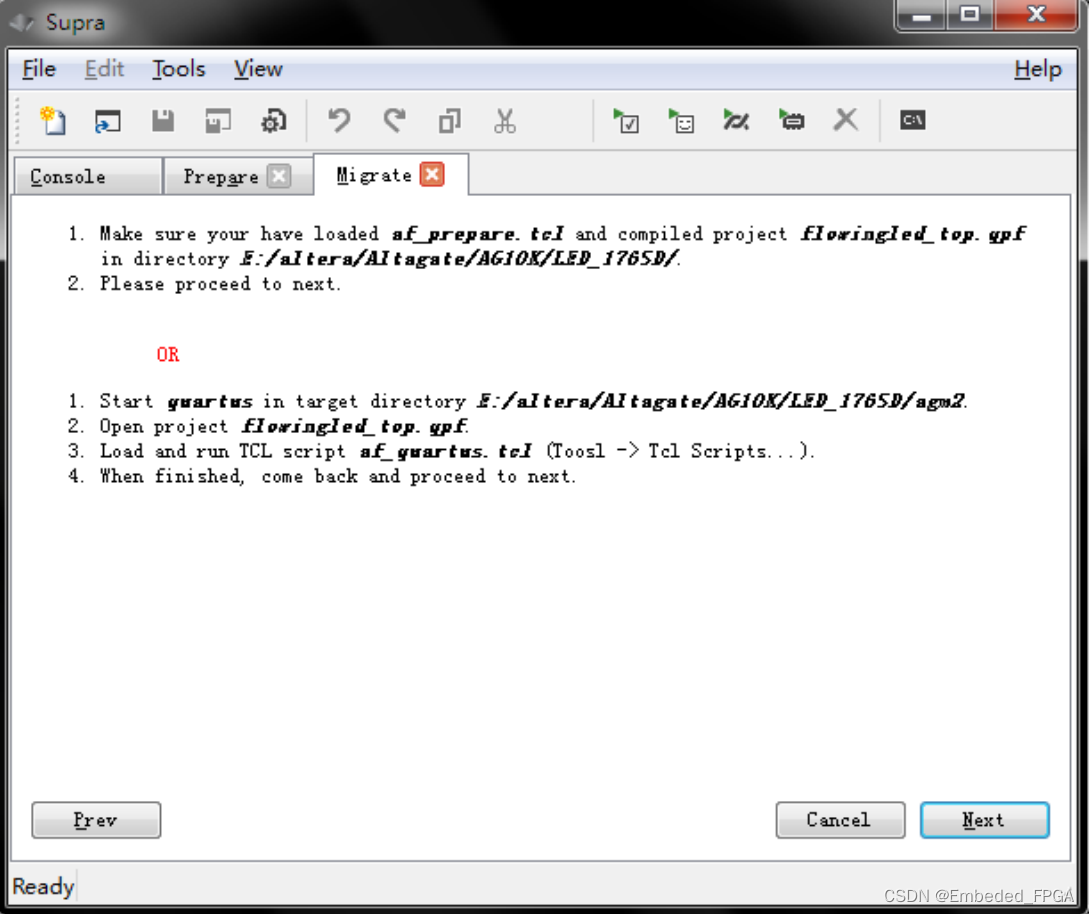

点击 Next,参考页面说明 OR 上面的部分,即直接点击 Next。

下面界面中可设置些编译参数,或采用默认设置即可。

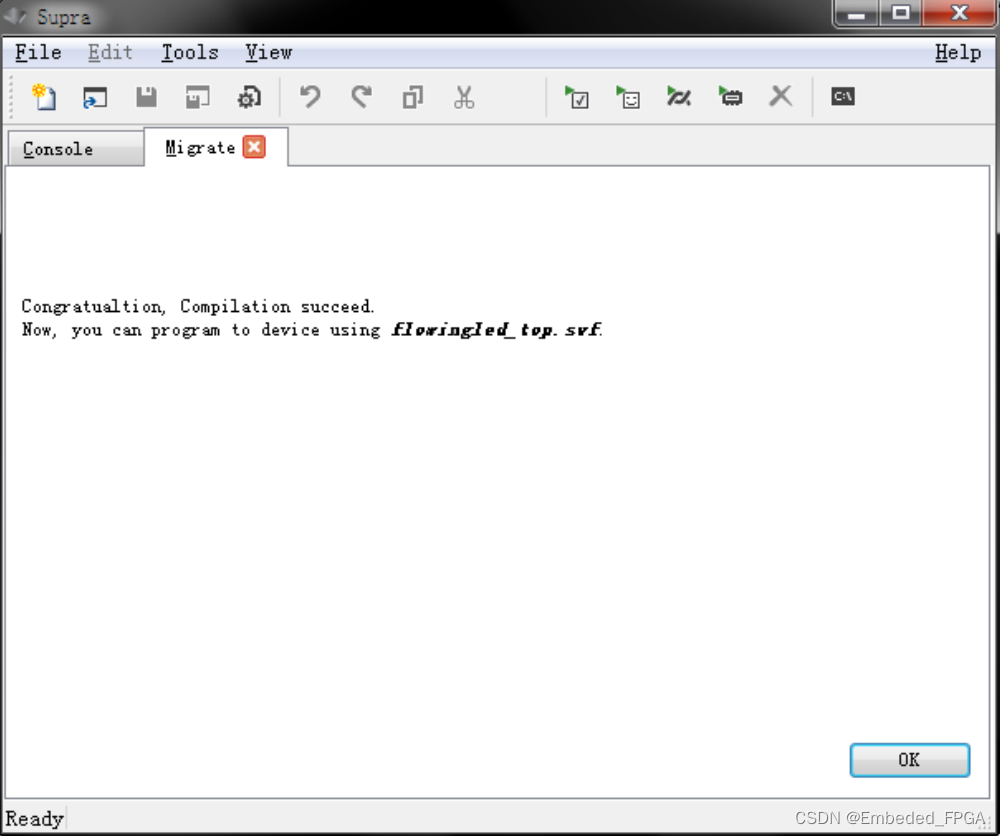

点击 Finish,进入编译过程,在 Console 界面可查看编译信息,成功后显示下面信息,并生成配置烧写文件。

如需修改原设计,由于 af_prepare.tcl 已把设置改好,不用重新执行 tcl,在 Quartus 中直接编译即可。然后在 Supra 中 Compile 界面进行最后编译。

? 器件烧写

Supra 软件中,选择菜单:Tools-Program。选择需烧写的 PRG 文件,采用默认下载线类型 USB-Blaster。

点击“Program”按钮,开始通过 JTAG 烧写 PCB 上 AG10K 或 FLASH 器件。

? 烧写文件类型:

_SRAM. prg 文件为片内 SRAM 写入,通过 JTAG 烧写,掉电即失效,可用于设计调试;

_master.prg 文件为 Master(AS)配置方式下,通过 JTAG 烧写 FLASH 的文件;

_master.bin 为 Master(AS)配置方式下,Flash 的通用烧写文件;

.bin 或 rbf 文件为 Slave(PS)配置方式所需文件,rbf 文件的字节高低位反向。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!