西南科技大学数字电子技术实验三(MSI逻辑器件设计组合逻辑电路及FPGA的实现)FPGA部分

2023-12-14 11:49:46

一、实验目的

- 进一步掌握MIS(中规模集成电路)设计方法。

- 通过用MIS译码器、数据选择器实现电路功能,熟悉它们的应用。

- 进一步学习如何记录实验中遇到的问题及解决方法。

二、实验原理

1、4位奇偶校验器

Y=S7i=0DiMi

D0=D3=D5=D6=D

D1=D2=D4=D7= `D

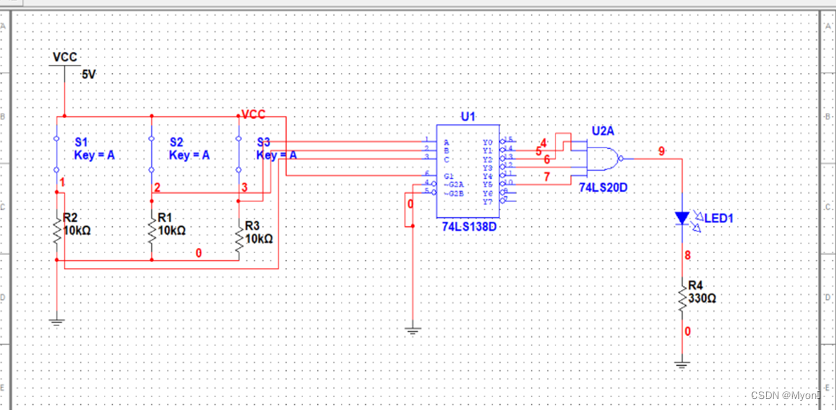

2、组合逻辑电路

F=A`B C +`A(B+C)

=A`B C+`AB(C+`C) +`AC(B+`B)

=m1+m2+m3+m5

= (`m1`m2 `m3`m5)’

三、程序清单(每条语句必须包括注释或在开发窗口注释后截图)

1、4位奇偶校验器

module jiou_d151_2

(

input [2:0]control_1,

input d,

output h

);

wire w,y;

wire d_0,d_1,d_2,d_3,d_4,d_5,d_6,d_7;

assign h=y;

assign d_0=d;

assign d_3=d;

assign d_5=d;

assign d_6=d;

assign d_1=~d;

assign d_2=~d;

assign d_4=~d;

assign d_7=~d;

mult_151_8 uu(

.g_1 (1'b0),

.control_1 (control_1),

.cont_1(y),

.ncont_1(w),

文章来源:https://blog.csdn.net/Myon5/article/details/134905173

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!