AG16K MCU ARM Cortex M3

AGM AG16K MCU 器件是 FPGA+MCU 的 SoC 单芯片产品。

FPGA 单元具有 16K LEs 的逻辑资源,MCU 为硬核 ARM Cortex M3。

MCU 特性

? 内核 ARM32 位的 Cortex M3 CPU

- 最高 200 Mhz 工作频率

- 单周期乘法和硬件除法

- 集成的嵌套式的中断控制器(NVIC)提供确定性的中断处理

? 高达 128K 字节的 SRAM

? 调试模式 - 串行调试模式(SWP)和 JTAG 接口

- Cortex M3 内嵌跟踪模块(ETM)

? 定时器 - 两个定时器,每个可被配置为一个 32 位的定时器或两个 16 位的定时器

- 独立的看门狗定时器

? GPIO

3 组 GPIO,每组 GPIO 是 8bit,取决于用户的配置

? 通信接口 - SPI 接口,用于访问程序存储器 FLASH,支持 FLASH 快速读写模式

- Uart 接口

- 访问外设的 AHB Master 接口

- 与 FPGA 交互的 AHB Slave 接口

- 共享 MCU 内部 RAM 访问接口;

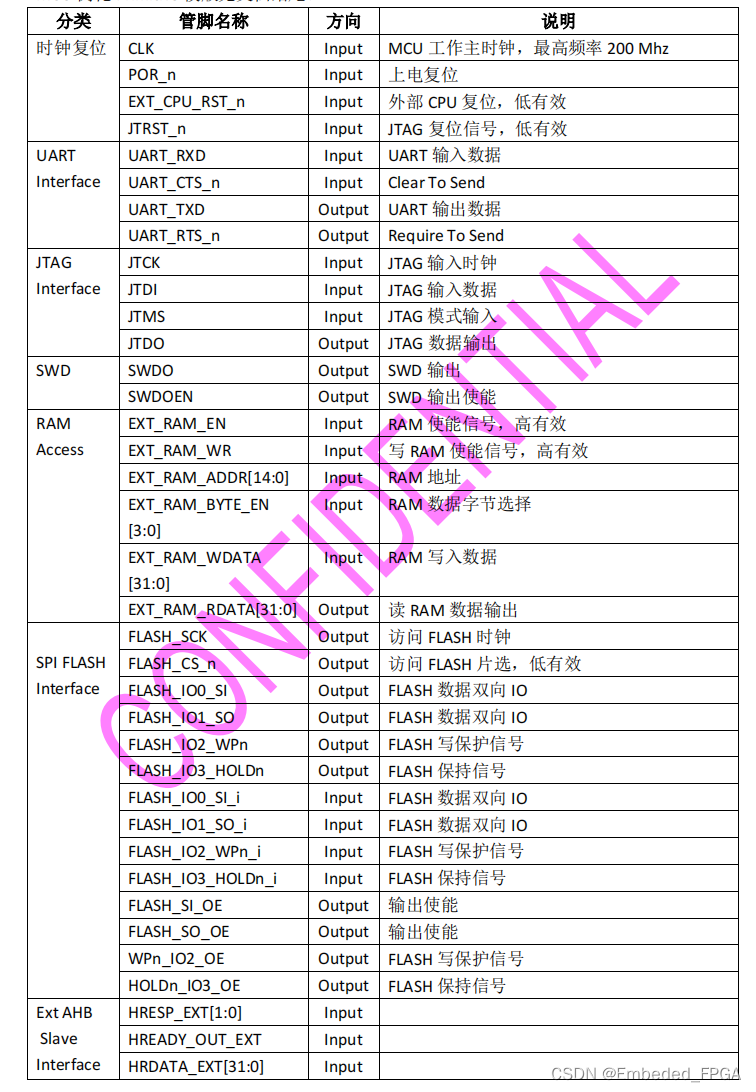

MCU 管脚说明:

所有 MCU 接口均可灵活配置为任意 FPGA 外部 IO,或 FPGA 内部连接。

MCU 例化 Primitive 模版见文档结尾。

注:在使用 MCU EXT AHB Interface 前,需要先对该接口进行使能才能正常使用。

使能寄存器 EXTAHBEN,具体见文档中寄存器说明;

? 设计说明

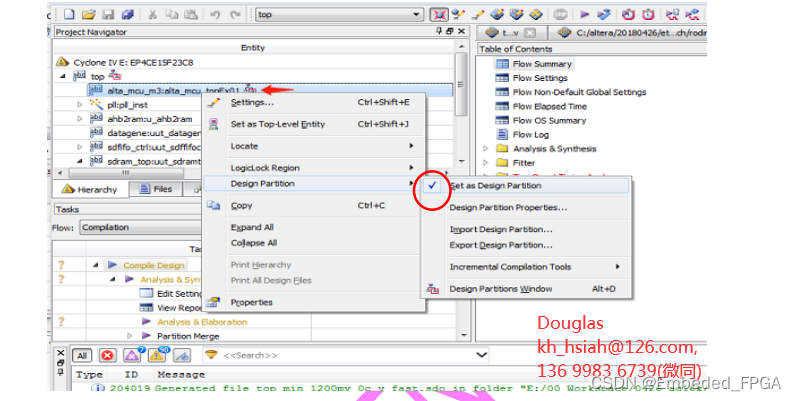

AG16K MCU 的 FPGA 工程中,需调用 alta_mcu_m3 的硬核 IP,包含在 alta_sim.v 的库文

件中,这个文件默认在 supra 的安装目录中,如:D:\Supra\etc\arch\rodinia。Quartus II

project 要添加这个文件,同时,要把 alta_mcu_m3 设为 Design Partition,如下图:

MCU 的 SPI 接口接到 FPGA 的 AS 口(复用配置管脚),就可以从配置 FLASH 读取软件程序了。

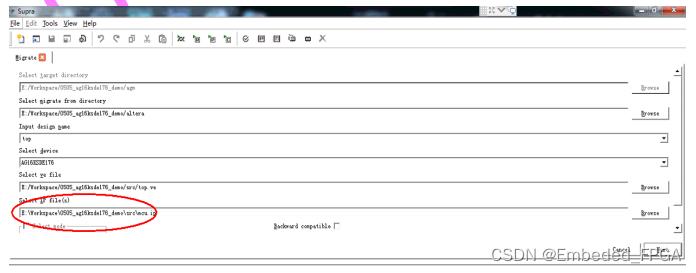

alta_mcu_m3 还有 2 个参数需要确定,需在 Supra 软件执行 migrate 时,添加 mcu.ip 文件,mcu.ip 文件用户自行创建,内容如下:

IP mcu_inst

TYPE : alta_mcu_m3;

PARAMETER

FLASH_BIAS : 24’h060000 BITS; //MCU 程序在 FLASH 中存放的首地址

CLK_FREQ : 8’h64 BITS; //MCU 主时钟频率(100MHz)

END_PARAMETER

END_IP

注: mcu.ip 文件中 IP 名字(如上:mcu_inst)需与设计中的自定义的 IP 名字完全一致;mcu 在 FLASH 中的存放地址 FLASH_BIAS 和 mcu 工作频率一定要与实际设计一致;

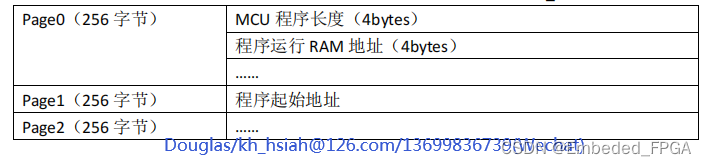

MCU 程序在 SPI FLASH 里的存储格式:

以下为偏移地址,存放 FLASH 中的起始地址由 MCU.IP 中的FLASH_BIAS 给出。

该存储格式可通过 2018.06.01 之后版本的 Supra 软件 Tools 中的 Generate 生成,流程如下:

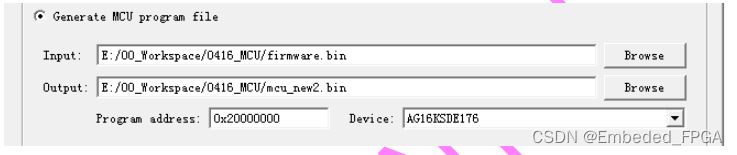

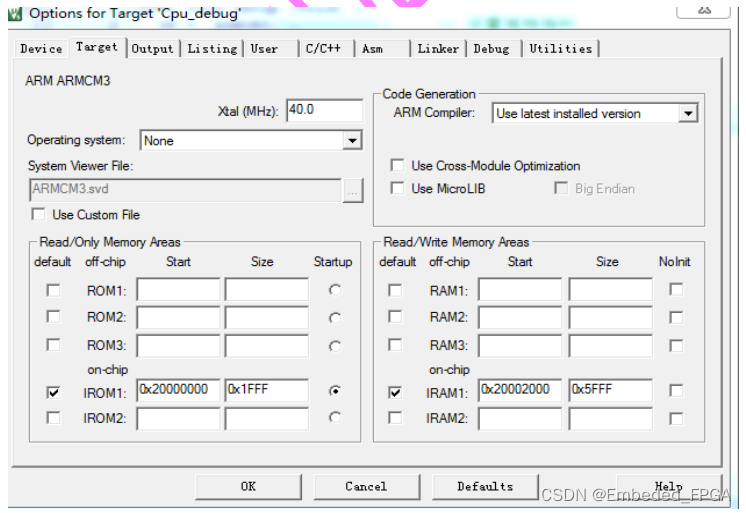

其中,Input文件为Keil生成的mcu程序文件,输出为合成后的存储格式Bin文件,Program address 为上方表格中“程序运行 RAM 地址(4bytes)”,即 Keil 中设置的程序运行地址。

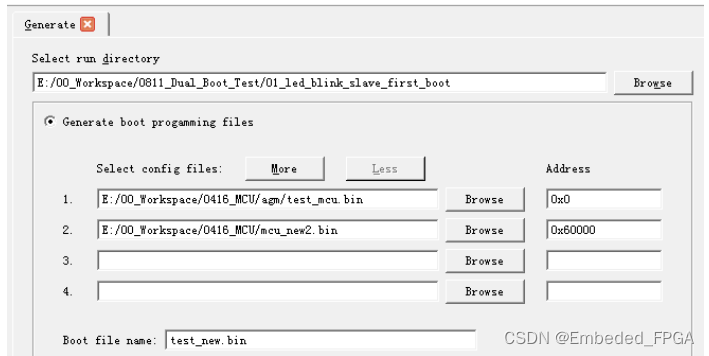

通过正常 FPGA 设计流程(参见 Manual_Supra),可得到 FPGA 硬件编程文件。

最后通过 Generate 将 MCU 程序和 FPGA 程序打包,生成 flash 烧写文件。其中 MCU 程序的地址,根据 mcu.ip 中设置的 FLASH_BIAS 进行设置。

? 软件设计

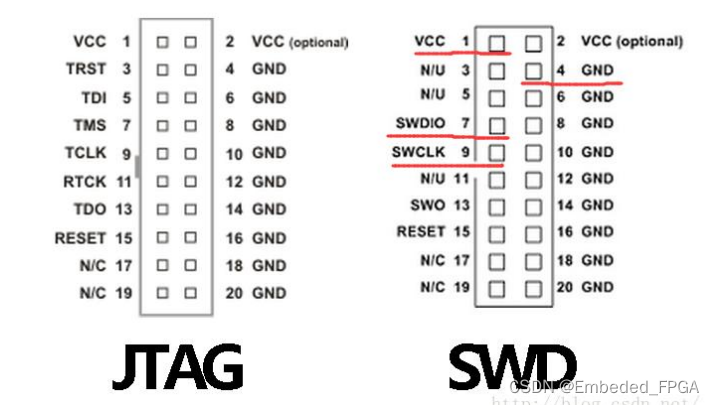

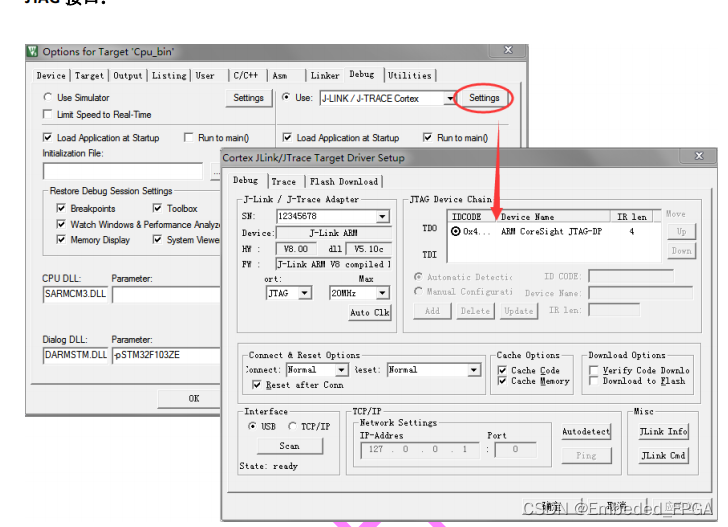

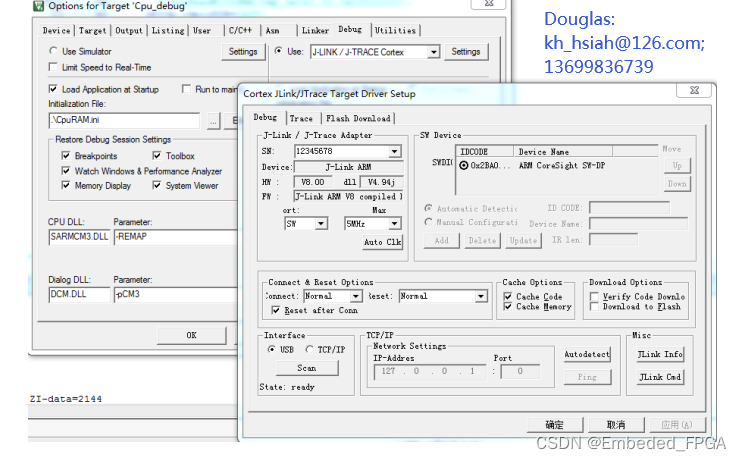

AG16K 的 MCU 可用 SWD 或者 JTAG 调试接口,管脚可通过任意 FPGA IO 引出,即可通过 ARM M3 调试工具进行软件设计和调试,如 J-LINK 和 Keil。

SWD 接口:

SWD 接口最少只需 VCC, GND, SWDIO, SWCLK 四个 pin 脚即可调试。SWD 接口的复用 JTAG接口的 JTMS 和 JTCK 两个管脚,如上图所示。

使用 SWD 接口替代 JTAG 接口时,需设置顶层 SWDIO 端口为 inout 型,同时代码中添加语句:“ assign SWDIO = SWDOEN ? SWDO : 1’bz; ”,MCU SWD 接口接法如下:

.JTRST_n ( ),

.JTCK (SWCLK ),

.JTDI ( ),

.JTMS (SWDIO ),

.JTDO ( ),

.SWDO (SWDO ),

.SWDOEN (SWDOEN ),

JTAG 接口:

SWD 接口:在这里插入图片描述

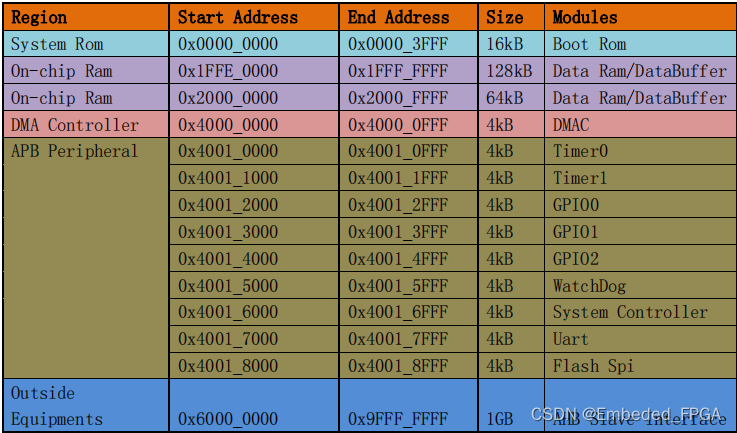

? MCU 地址映射表:

一、基本地址空间

Note: 0x2000_0000-0x2000_FFFF 地址映射的 64KB SRAM 与 0x1FFF_0000-0x1FFF_FFFF 地址映射的 64KB SRAM 是同一个;

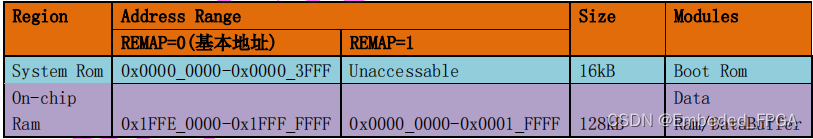

二、地址 REMAP

当通过 CPU 的 DBUS、IBUS 访问代码区空间(0x0000_0000-0x1FFF_FFFF)时,可以通过 REMAP功能改变地址映射。

REMAP=0 时,0x0000_0000 地址映射在 ROM 上,CPU 从 ROM 启动。

REMAP=1 时,0x0000_0000 地址映射在 On-chip Ram 上,CPU 从 On-chip Ram 启动。

注意,REMAP 的设置,只对来自 DBUS、IBUS 的访问有效。

来自 CPU SBUS 以及 DMA 等其他 AHB Master 的访问,无论 REMAP 如何设置,都按照基本地址空间的地址访问。

? MCU 寄存器地址说明:

? MCU 例化模版:

注意:其中 EXT_RAM,AHB_SLAVE, AHB_MASTER 接口不使用时,一些控制管脚需设置定值;

alta_mcu_m3 mcu_inst (

.CLK ( ),

.POR_n ( ),

.EXT_CPU_RST_n ( ),

.JTRST_n ( ),

.JTCK ( ),

.JTDI ( ),

.JTMS ( ),

.JTDO ( ),

.SWDO ( ),

.SWDOEN ( ),

.UART_RXD ( ),

.UART_CTS_n ( ),

.UART_TXD ( ),

.UART_RTS_n ( ),

// On-Chip Memory Ports

.EXT_RAM_RDATA ( ),

.EXT_RAM_EN (1’b0 ),

.EXT_RAM_WR ( ),

.EXT_RAM_ADDR ( ),

.EXT_RAM_BYTE_EN ( ),

.EXT_RAM_WDATA ( ),

// AHB Slave Ports

.HRESP_EXT (2’b00 ),

.HREADY_OUT_EXT ( ),

.HRDATA_EXT ( ),

.HTRANS_EXT ( ),

.HADDR_EXT ( ),

.HWRITE_EXT ( ),

.HSEL_EXT ( ),

.HWDATA_EXT ( ),

.HSIZE_EXT ( ),

.HREADY_IN_EXT ( ),

// AHB Master Ports

.HRESP_EXTM ( ),

.HREADY_OUT_EXTM ( ),

.HRDATA_EXTM ( ),

.HTRANS_EXTM (2’b0 ),

.HADDR_EXTM ( ),

.HWRITE_EXTM ( ),

.HSEL_EXTM (1’b0 ),

.HWDATA_EXTM ( ),

.HSIZE_EXTM ( ),

.HREADY_IN_EXTM (1’b1 ),

.HBURSTM ( ),

.HPROTM (4’b0 ),

.FLASH_SCK (FLASH_SCK ),

.FLASH_CS_n (FLASH_CS_n ),

.FLASH_IO0_SI_i (FLASH_IO0_SI ),

.FLASH_IO1_SO_i (FLASH_IO1_SO ),

.FLASH_IO0_SI (flash_io0_si_o ),

.FLASH_IO1_SO (flash_io1_so_o ),

.FLASH_IO2_WPn (flash_io2_wpn_o ),

.FLASH_IO3_HOLDn (flash_io3_holdn_o ),

.FLASH_IO2_WPn_i (1’b1 ),

.FLASH_IO3_HOLDn_i (1’b1 ),

.FLASH_SI_OE (flash_si_oe ),

.FLASH_SO_OE (flash_so_oe ),

.WPn_IO2_OE (flash_wpn_oe ),

.HOLDn_IO3_OE (flash_holdn_oe ),

.GPIO0_I ( ),

.GPIO1_I ( ),

.GPIO2_I ( ),

.GPIO0_O ( ),

.GPIO1_O ( ),

.GPIO2_O ( ),

.nGPEN0 ( ),

.nGPEN1 ( ),

.nGPEN2 ( )

) ;

assign FLASH_IO0_SI = (flash_si_oe == 1’b1)? flash_io0_si_o :1’bz;

assign FLASH_IO1_SO = (flash_so_oe == 1’b1)? flash_io1_so_o :1’bz;

assign FLASH_IO2_WPN = (flash_wpn_oe == 1’b1)? flash_io2_wpn_o :1’bz;

assign FLASH_IO3_HOLDN = (flash_holdn_oe == 1’b1)? flash_io3_holdn_o :1’bz;

最详细的基于AG16K的Cortex M3应用手册,欢迎使用,有疑问请联系kh_hsiah@126.com/Douglas。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!