verilog基本语法-case语句-译码电路,编码电路,选择器电路

2023-12-14 14:37:41

概述:

本节主要讲解LUT构造的组合逻辑电路中的译码电路,编码电路,选择器电路。这些基本电路是使用的最广泛的电路,但是一般情况下很容易忽略这些电路。其中译码电路是构成RAM中写地址的电路,而选择电路是构成RAM中数据读出的地址。编码电路用于模数转换器ADC的编码等。这些都是使用FPGA的过程 中经常用到的,但是容易忽视他的设计原理。本节通过基本的verilog语句来测试这些电路的构造原理。

使用case语句构造

case(a)

_:_;

...

endcase主要内容

1.译码电路

2.编码电路

3.选择器电路

1.译码电路

代码

module assign1(

input[1:0] A,

output reg [3:0] y

);

always @(*)

case (A)

2'b00 : y <= 4'b0001;

2'b01 : y <= 4'b0010;

2'b10 : y <= 4'b0100;

2'b11 : y <= 4'b1000;

default : y <= 4'b0000;

endcase

endmoduleRTL结构图

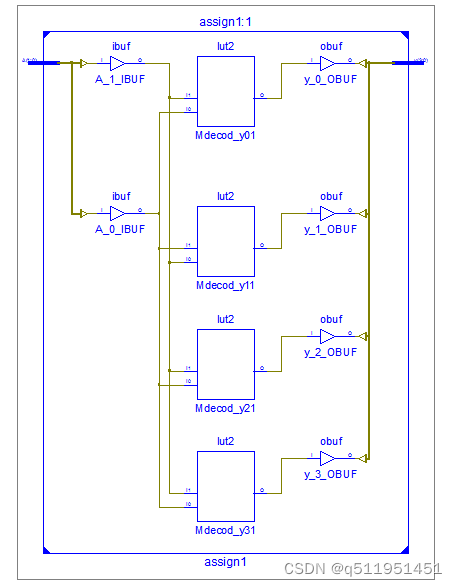

技术原理图

2.编码电路

代码

module assign1(

input[3:0] A,

output reg [1:0] y

);

always @(*)

case (A)

4'b0001 : y <= 2'b00;

4'b0010 : y <= 2'b01;

4'b0100 : y <= 2'b10;

4'b1000 : y <= 2'b11;

default : y <= 2'b00;

endcase

endmoduleRTL结构图

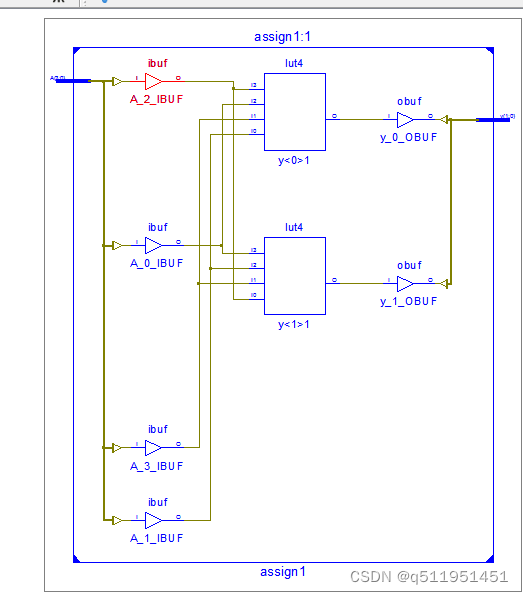

技术原理图

3.选择电路

代码

module assign1(

input[1:0] A,

input din1,din2,din3,din4,

output reg y,

output y2

);

assign y2 = A[0]? din2 : din1; // 2选1

always @(*) // 4选1

case (A)

2'b00: y = din1;

2'b01: y = din2;

2'b10: y = din3;

2'b11: y = din4;

endcase

endmodule

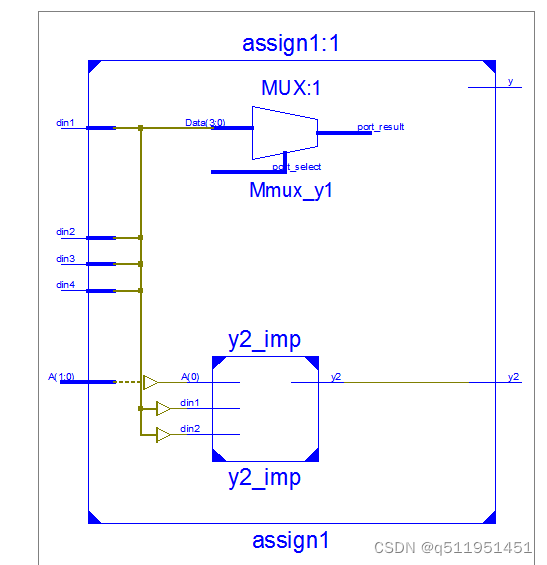

RTL结构图

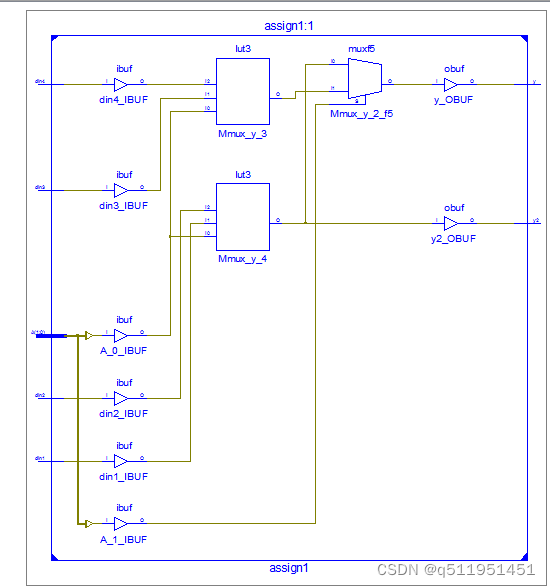

技术原理图

4. 总结

1. 通过awalys @(*) 语句实现组合逻辑语句

2. case语句可以实现译码电路,编码电路,选择电路的实现

3. 译码电路和编码电路会遇到宽组合逻辑设计场合,列如1G的ram的写地址线,65536位ADC的编码等,

4. 选择电路是FPGA内部结构的基本元件,他的使用频率高,使用LUT+MUX结合来设计组合电路,可以提高资源的利用率。此外选择器也作为存储器的读出地址线。

文章来源:https://blog.csdn.net/q511951451/article/details/134991807

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!