HI3559AV100和FPGA 7K690T的PCIE接口调试记录-续

2023-12-14 11:31:07

上文![]() https://blog.csdn.net/fzktongyong/article/details/134963814?spm=1001.2014.3001.5501????????上一篇文中PCIE实测速度和理论计算有较大偏差,经过尝试后有所提升。

https://blog.csdn.net/fzktongyong/article/details/134963814?spm=1001.2014.3001.5501????????上一篇文中PCIE实测速度和理论计算有较大偏差,经过尝试后有所提升。

1、提升效果

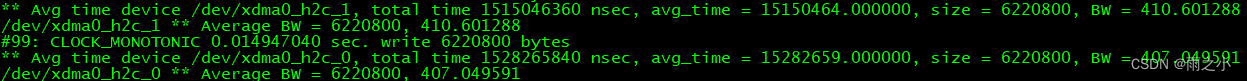

? ? ? ? 1)、RC写操作,实测速度817MB/s(410+407)

? ? ? ? ? ? ? ? 先前为670MB/s。

????????

? ? ? ? 2)、RC读操作,实测速度710MB/s(357+353)

? ? ? ? ? ? ? ? 先前为500MB/s。

2、提升原理

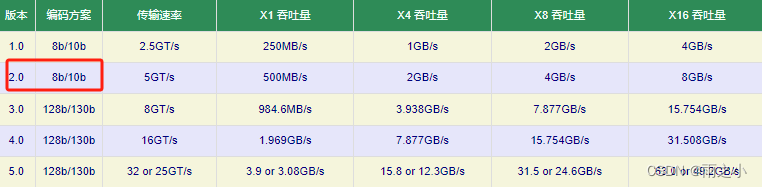

? ? ? ?标准的PCIE接口速率如下:

????????因为FPGA的PCIE速度是可以接近于理论的,主要是CPU的控制管理速度跟不上,所以我尝试了XDMA的双通道接口,XDMA最多有4通道。多通道理论上是可以实现对FPGA的DMA并行控制,因此如果使用4通道的DMA可能会有更多的速度提升。

????????

文章来源:https://blog.csdn.net/fzktongyong/article/details/134988298

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!